微机总线

Posted 绀香零八

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了微机总线相关的知识,希望对你有一定的参考价值。

文章目录

总线技术

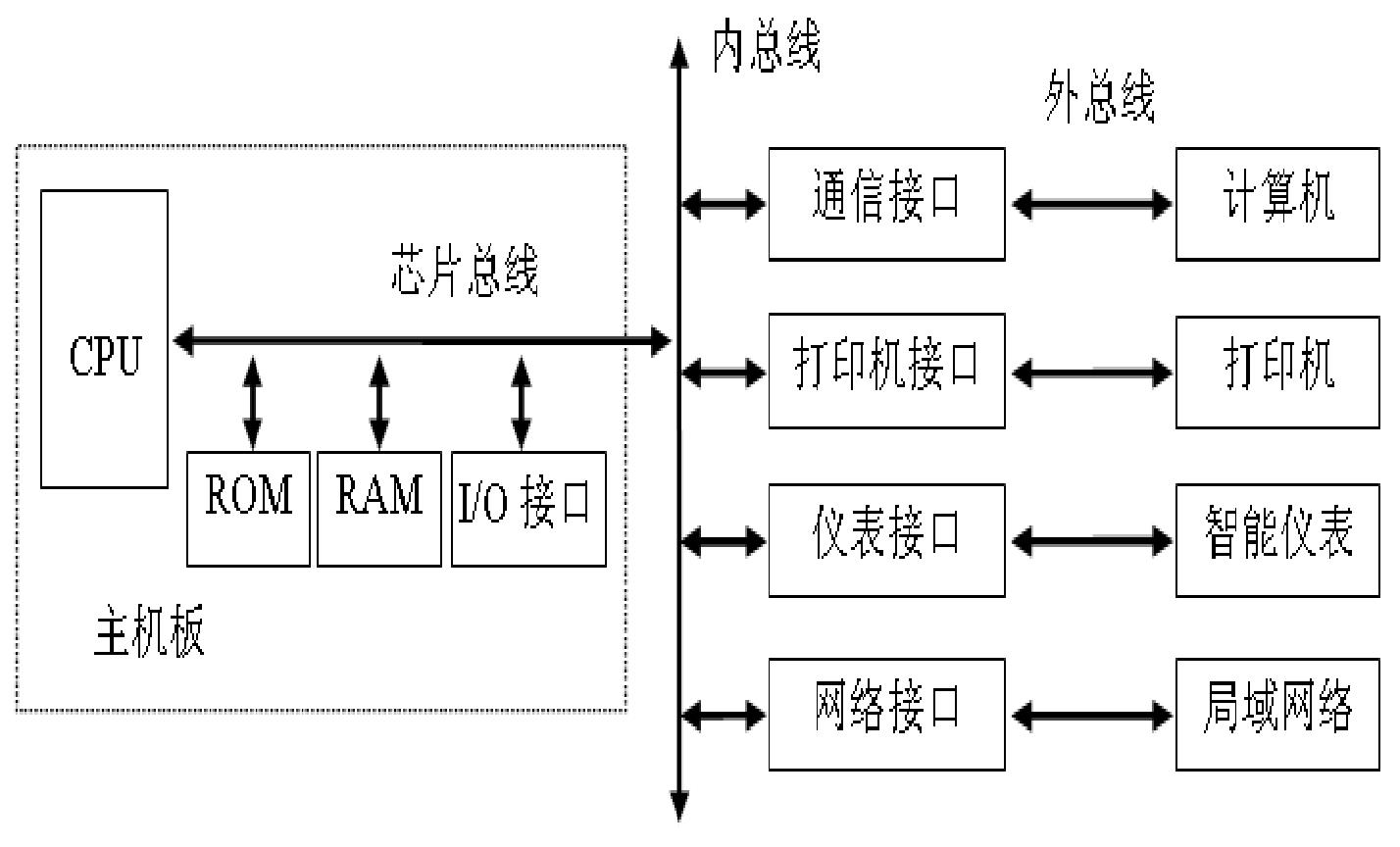

· 微型计算机系统的总线结构:以总线作为信息传输的公共通道

· 总线结构的特点:通过总线相互连接、实现数据传输;组态灵活、易于扩展等

· 广泛应用的总线都实现了标准化

· 便于在互连各个部件时遵循共同的总线规范

总线类型

· 芯片总线(Chip Bus)

芯片级互连,大规模集成电路芯片内部,或系统中各种不同器件连接在一起的总线

局部总线(Local Bus),微处理器的引脚信号

片内总线,大规模集成电路芯片内部连接

· 内总线(Internal Bus)

模板级互连,主机内部功能单元(模板)间连接的总线

板级总线、母板总线,或系统总线

系统总线(System Bus)是微机系统的主要总线

内部总线从一条变为多条,形成多总线结构

· 外总线(External Bus)

设备级互连,微机与其外设或微机之间连接的总线

过去,指通信总线;现在,常延伸为外设总线

微机总线层次结构

总线的数据传输

主设备(Master):控制总线完成数据传输

从设备(Slave):被动实现数据交换

某一时刻,只能有一个主设备控制总线,其他设备此时可以作为从设备

某一时刻,只能有一个设备向总线发送数据,但可以有多个设备从总线接收数据

- 总线操作

· 总线请求和仲裁(Bus request & Arbitration)

使用总线的主模块提出申请,总线仲裁机制确定把总线分配给请求模块

· 寻址(Addressing)

主模块发出将要访问的从模块地址信息以及有关命令,启动从模块

· 数据传送(Data Transfer)

源模块发出数据,经数据总线传送到目标模块

· 结束(Ending)

数据、地址、状态、命令信息均从总线上撤除,让出总线 - 总线仲裁

· 总线仲裁:决定当前控制总线的主设备

· 集中仲裁:系统具有中央仲裁器(控制器),负责主模块的总线请求和分配总线的使用

· 分布仲裁:各个主模块都有自己的仲裁器和唯一的仲裁号,主模块请求总线时,发送其仲裁号,比较各个主设备仲裁号决定 - 同步方式

· 同步时序

总线操作过程由共用的总线时钟信号控制

适合速度相当的器件互连总线,否则需要准备好信号让快速器件等待慢速器件(半同步)

处理器控制的总线时序采用同步时序

· 异步时序

总线操作需要握手联络(应答)信号控制

传输的开始伴随有启动(选通或读写)信号

传输的结束有一个确认信号,进行应答

操作周期可变、可以混合慢速和快速器件 - 传输类型

· 读数据传送:数据由从设备到主设备

· 写数据传送:数据由主设备到从设备

· 猝发传送(数据块传送):给出起始地址,将固定块长的数据一个接一个地从相邻地址读出或写入

· 写后读(Read-After-Write):先写后读同一个地址单元,适用于校验

· 读修改写(Read-Modify-Write):先读后写同一个地址单元,适用共享数据保护

· 广播(Broadcast):一个主设备对多个从设备的写入操作 - 性能指标

· 总线宽度

总线能够同时传送的数据位数

位数越多,一次能够传送的数据量越大

· 总线频率

总线信号的时钟频率

时钟频率越高,工作速度越快

· 总线带宽(Bandwidth)

单位时间传输的数据量

总线带宽越大,总线性能越高

总线带宽=总线传输速率=吞吐率

总线带宽=传输的数据量÷需要的时间

常用单位 1M=106

每秒兆字节(MB/s) 每秒兆位(Mb/s)或每秒位(bps)

举例

5MHz的8086微处理器

16÷(4×0.2×10-6)bps=20×106 bps=2.5 MB/S

66MHz的Pentium,基本非流水线总线周期

64÷2×66×106 bps=264 MB/S

66MHz的Pentium,2-1-1-1猝发读周期

32÷5×66×106 B/S=422.4 MB/S

总线带宽 = 传输的数据量/需要的时间 = 字宽(长)*主频/ 时钟数

8086处理器的数据总线是16位,典型的时钟频率是5MHz,即每个时钟周期是0.210^-6s。8086需要4个时钟周期构成一个总线周期,实现一次16位数据的传送,带宽为

16 / (40.2*10^-6)b/s = 20 * 10 ^6b/s=20Mb/s = 2.5MB/s

1M = 10^6

总线信号和总线时序

· 地址总线

主控模块(如处理器)的地址总线输出

从模块(如存储器或I/O端口)的地址总线输入

· 数据总线

双向传输,在主从模块间传送、交换数据信息

· 控制总线

有输出也有输入信号

基本功能是控制存储器及I/O读写操作

还包括中断与DMA控制、总线仲裁、数据传输握手联络等

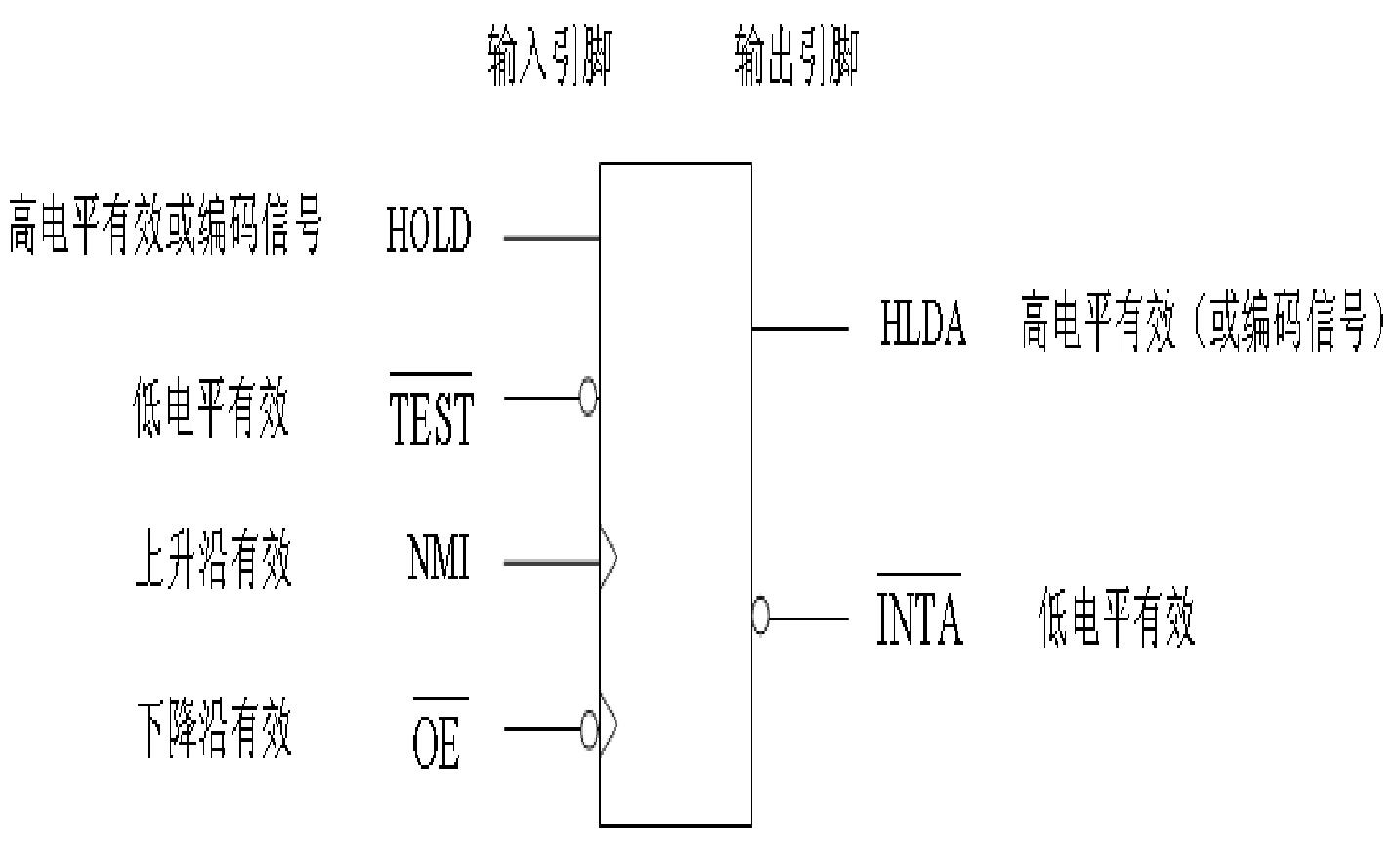

- 引脚信号

信号的功能:用英文单词或英文缩写表示引脚名称

信号的流向:处理器输出到外部,从外部输入到处理器内部

有效方式:低电平、高电平有效,上升沿、下降沿有效、高电平和低电平都有效

三态能力:高阻状态放弃对引脚的控制;其他设备控制该引脚

- 总线时序

· 总线时序(Timing)

描述总线信号随时间变化的规律以及总线信号间的相互关系

采用时序图形象化地表现时序

· 指令周期:一条指令从取指、译码到最终执行完成的过程

· 总线周期或机器周期:伴随有数据交换的总线操作

· T状态:处理器的基本工作节拍,对应时钟周期

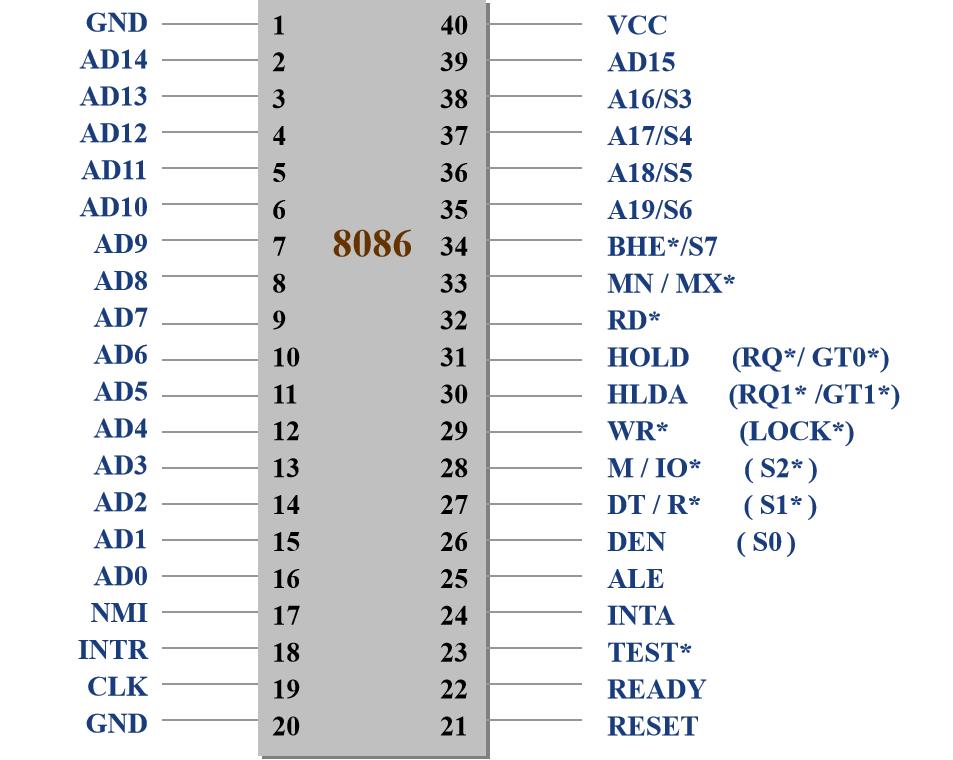

8086的引脚信号

处理器的外部特性表现在它的引脚信号上

40个引脚

地址/数据信号

· AD15~AD0(Address/Data)

地址/数据分时复用引脚,共16个引脚

单向输出地址总线,双向数据总线,三态输出

· A19/S6~A16/S3(Address/Status)

地址/状态分时复用引脚,4个三态输出信号

输出高4位地址、状态信号

· BHE*/S7(Byte High Enable/Status)

高字节允许/状态分时复用引脚,三态输出信号

输出低有效表示传送高字节数据,状态信号

总线复用:同一引脚在不同时刻具有不同功能

读写控制信号

· 8086处理器的引脚信号具有两种工作模式

面向小系统的最小组态模式:8086本身提供了系统所需要的全部控制信号

组成较大系统的最大组态模式:8086需要配合其他芯片形成控制信号,但可以连接数值协处理器、I/O协处理器等构成多处理器系统

· 两种组态的不同只是反映在外部引脚上

· 由一个引脚接高电平或低电平区别

· 内部工作方式一样

- 基本读写引脚

· ALE(Address Latch Enable)

地址锁存允许,三态、输出、高电平有效

有效时,表示复用引脚正在传送地址信号

· M/IO*(Memory/Input and Output)

访问存储器或者I/O,三态、输出、高低电平均有效

高电平(M),表示处理器访问存储器

低电平时(IO*),表示处理器访问I/O端口

· WR*(Write)

写控制,三态、输出、低电平有效

有效时,表示处理器正将数据写到存储单元或I/O端口

· RD*(Read)

读控制,三态、输出、低电平有效

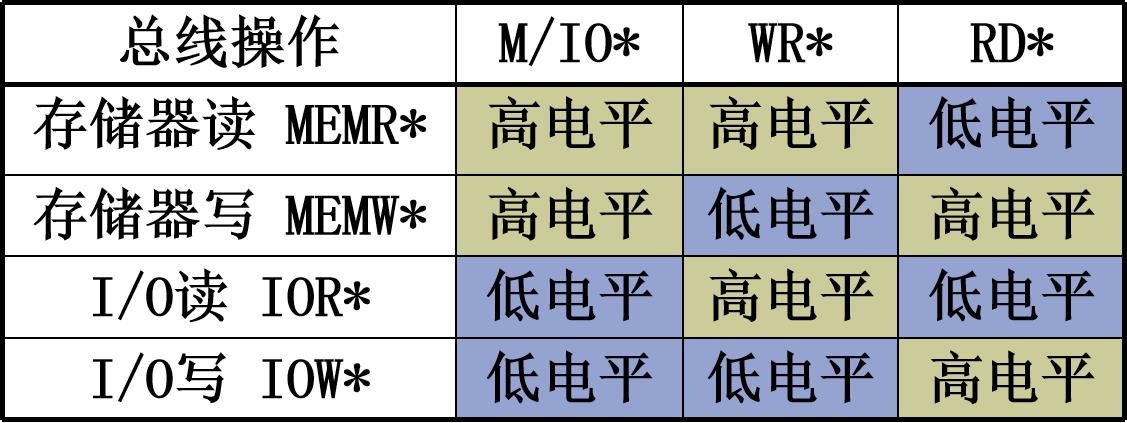

有效时,表示处理器正从存储单元或I/O端口读取数据 - 基本总线操作

· 存储器读(Memory Read)

处理器从存储器读取代码或读取操作数

每条指令执行前都需从主存取指,以存储单元为源操作数的指令在执行时

· 存储器写(Memory Write)

处理器向存储器写入操作数,以存储单元为目的操作数的指令在执行时

· I/O读(Input/Output Read)

处理器从外设读取操作数

只有执行输入指令IN时才有

· I/O写(Input/Output Write)

处理器向外设写出操作数

只有执行输出指令OUT时才有

读写控制信号的组合

- 同步操作引脚

· 同步操作

读写操作要保证存储器或外设与处理器速度一致

否则,慢速的I/O或存储器发出一个信号

让快速的处理器等待

· READY 就绪(准备好)

输入信号,高电平有效表示可以进行数据读写

利用该信号无效请求处理器等待数据

处理器在进行读写前检测READY引脚

其他控制信号

· 处理器必定具有

地址总线、数据总线、基本读写控制信号

· 还有

中断请求和响应信号、总线请求和响应信号、时钟信号、复位信号、电源Vcc、地线GND

- 中断请求和响应引脚

· INTR(Interrupt Request)

可屏蔽中断请求,高电平有效的输入信号

有效时,表示中断请求设备向处理器申请可屏蔽中断

中断IF标志对该中断请求进行屏蔽

主要用于实现外设数据交换的中断服务

· INTA*(Interrupt Acknowledge)

可屏蔽中断响应,低电平有效的输出信号

有效时,表示来自INTR引脚的中断请求已被处理器响应

· NMI(Non-Maskable Interrupt)

不可屏蔽中断请求,上升沿有效的输入信号

有效时,表示外界向CPU申请不可屏蔽中断

中断级别高于可屏蔽中断请求INTR

常用于处理系统发生故障等紧急情况下的中断服务 - 总线请求和响应引脚

· HOLD

总线请求,高电平有效的输入信号

有效时,表示其他总线主控设备申请使用总线

· HLDA(HOLD Acknowledge)

总线响应,高电平有效的输出信号

有效时,表示处理器已响应总线请求

总线释放:地址总线、数据总线及具有三态输出能力的控制总线呈现高阻状态 - 其他引脚

· RESET

复位,高电平有效的输入信号

有效时,将迫使处理器回到其初始状态

8086复位后,寄存器CS=FFFFH,IP=0000H

· CLK(Clock)

时钟输入,频率稳定的数字信号

处理器的基本操作节拍

频率的倒数是时钟周期的时间长度

8086的总线时序

· 处理器以统一的时钟信号为基准,控制其他信号跟随时钟相应改变,实现总线操作

· 每个时钟周期,进行不同的操作、处于不同的操作状态(State)

T1 T2 T3 T4

· 8086处理器的基本总线周期:4个时钟周期

· 4个基本总线周期

读总线周期:存储器读和I/O读

写总线周期:存储器写和I/O写

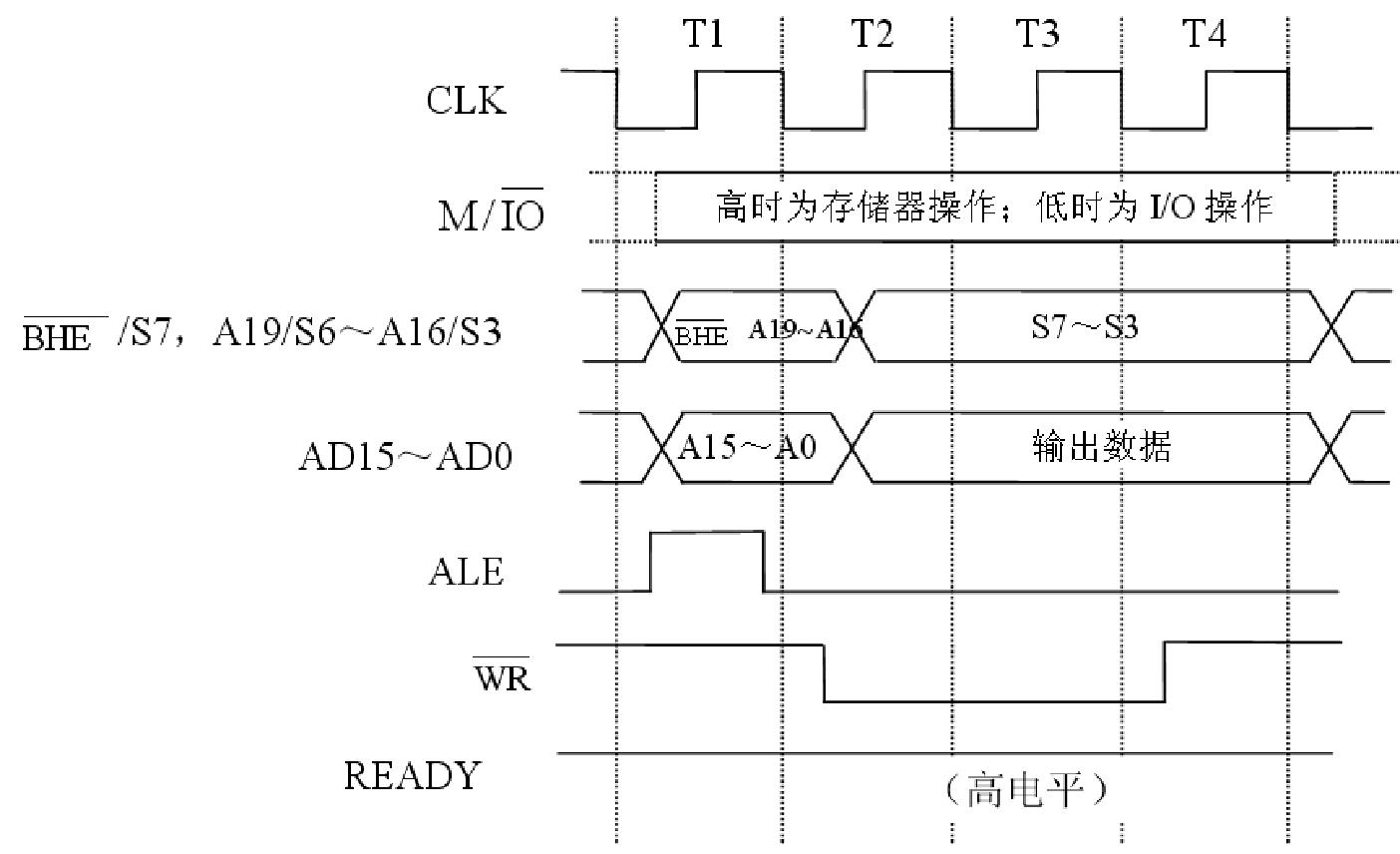

写总线周期

· 完成对存储器或I/O端口的一次写操作

· T1状态

输出20位存储器地址A19~A0

M/IO输出高电平,表示存储器操作

或者M/IO输出低电平,表示I/O操作

ALE输出正脉冲,表示复用总线输出地址

· T2状态

输出控制信号WR*和数据D15~D0

· T3状态

检测数据传送是否能够完成

· T4状态

完成数据传送

写总线周期时序

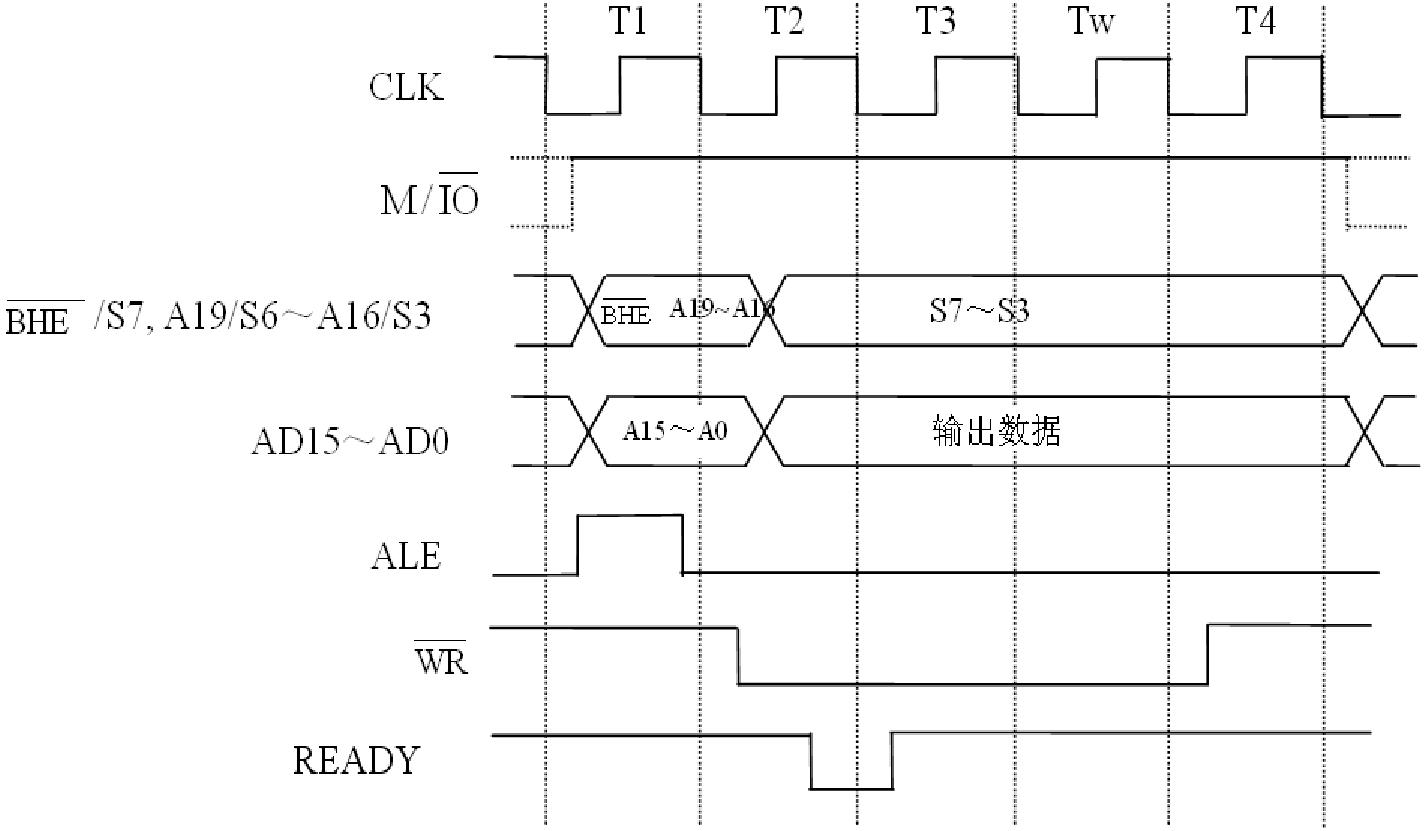

等待状态

处理器运行速度远远快于存储器和I/O端口

控制READY信号为低无效,不进入T4状态,插入等待状态Tw

Tw状态:引脚信号延续T3时的状态

一个Tw状态的长度是一个时钟周期

在Tw的前沿,继续对READY进行测试

无效继续插入Tw;有效时转入T4状态

具有一个Tw的存储器写总线周期时序

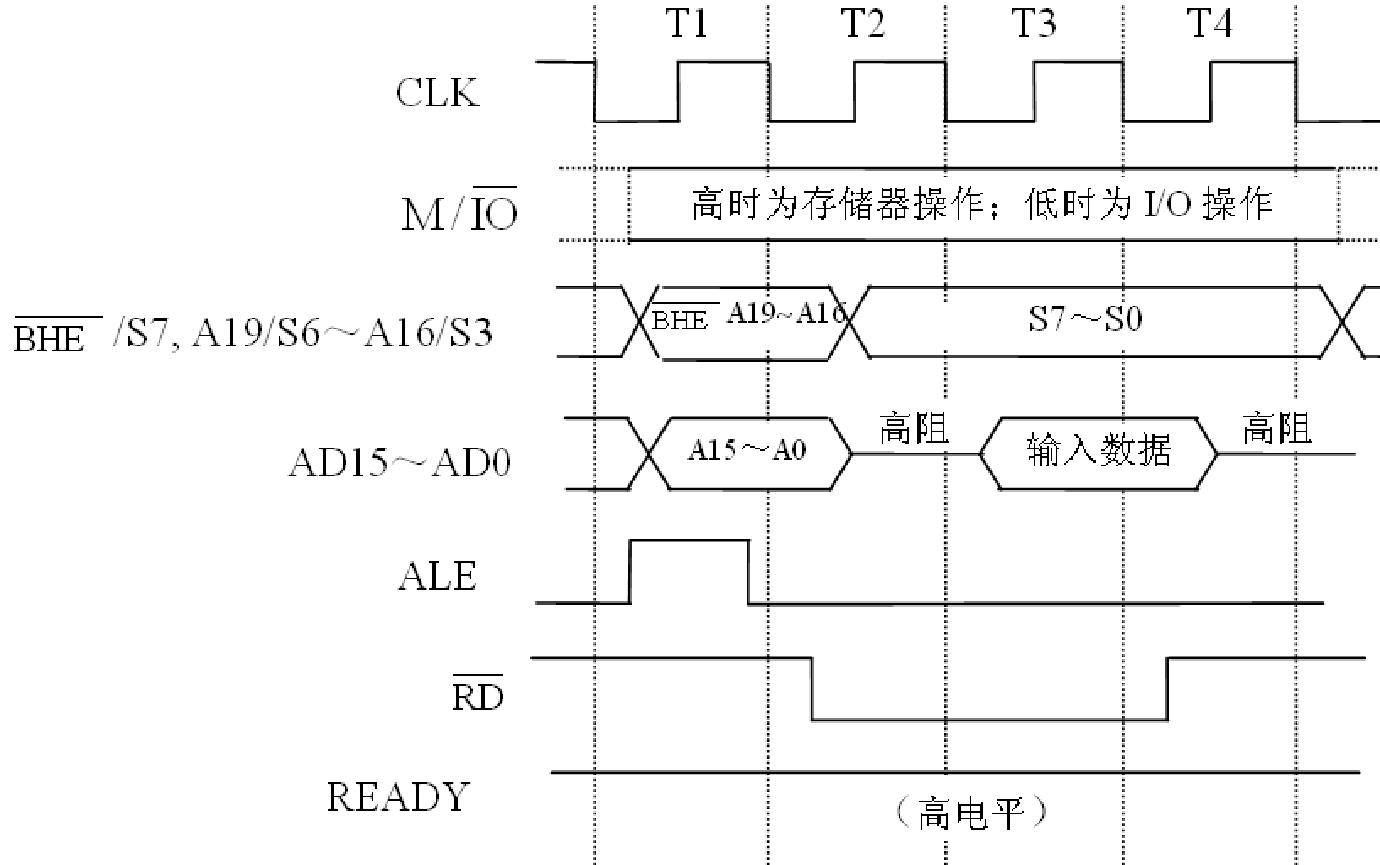

读总线周期

· 完成对存储器或I/O端口的一次读操作

· T1状态

输出20位存储器地址A19~A0

M/IO输出高电平,表示存储器操作

或者M/IO输出低电平,表示I/O操作

ALE输出正脉冲,表示复用总线输出地址

· T2状态

输出控制信号RD*,存储器或I/O端口发送数据

· T3状态和Tw状态

检测数据传送是否能够完成

· T4状态

获取数据,完成传送

读总线周期时序

微机系统总线

PC总线的发展

· 16位PC机:单总线结构

IBM PC机和IBM PC/XT机的IBM PC总线

IBM PC/XT机的IBM AT总线,即ISA总线

· 早期32位PC机

与MCA总线竞争的EISA总线(扩展 ISA总线)

32位局部总线VESA

· 当前32位PC机:多总线结构

存储总线

系统总线:外设部件互连PCI、PCI-X

显示总线:图形加速接口AGP、PCI-E

外设接口:键盘接口、鼠标接口、并行打印机接口、串行通信接口,通用串行接口USB,IEEE 1394接口

ISA总线

· 16位系统总线,用于IBM PC/AT及其兼容机

· 由前62引脚(A和B面)和后36引脚(C和D接面)两个插槽组成:

1.IBM PC机和IBM PC/XT机的IBM PC总线

前62个信号,其中8位数据总线、20位地址总线

时钟频率4.77MHz,4个时钟周期传送8位数据

2.IBM AT机增加部分

后36个信号,16位数据引脚和24位地址引脚

8MHz总线频率,2个时钟周期传送16位数据

- 数据和地址线

SD15~SD0:16位双向数据信号线

SBHE:高字节允许信号

SA19~SA0:低20位经过锁存输出的地址线

LA23~LA17:高7位可锁存地址信号线

16位数据总线支持16位和8位设备,24位地址总线寻址16MB主存空间

- 读写控制线

BALE:缓冲地址锁存允许,指示CPU总线周期

IOR*,IOW*:I/O读和I/O写信号

MEMR*,SMEMR*:存储器读

MEMW*,SMEMW*:存储器写

MEMCS16*:16位存储器总线周期

IOCS16*:16位I/O总线周期

I/O CH RDY:I/O通道准备好输入信号

0WS*:零等待状态(Zero Wait State) - 中断请求线

IRQ3~IRQ7,IRQ9~IRQ12,IRQ14,IRQ15

可屏蔽中断请求信号,优先权顺序

IRQ9~IRQ12,IRQ14,IRQ15,IRQ3~IRQ7

16位PC机共有16个请求引脚

IRQ0和IRQ1用于系统主机板的时钟和键盘中断

IRQ2用于两个中断控制器连接

IRQ8用于实时时钟

IRQ13连接数值协处理器

其余引向系统总线,有些已分配给系统外设 - DMA传送控制线

AEN:地址允许,指示DMA总线周期

DRQ0~DRQ3,DRQ5~DRQ7:DMA请求

DACK0~DACK3,DACK5~DACK7:DMA响应

T/C:计数结束信号,表示DMA传送结束

MASTER*:主设备

16位PC机的共有8个DMA通道

DRQ0~DRQ3用于8位DMA传送

DRQ5~DRQ7用于16位DMA传送

DRQ4已经用于连接两个DMA控制器

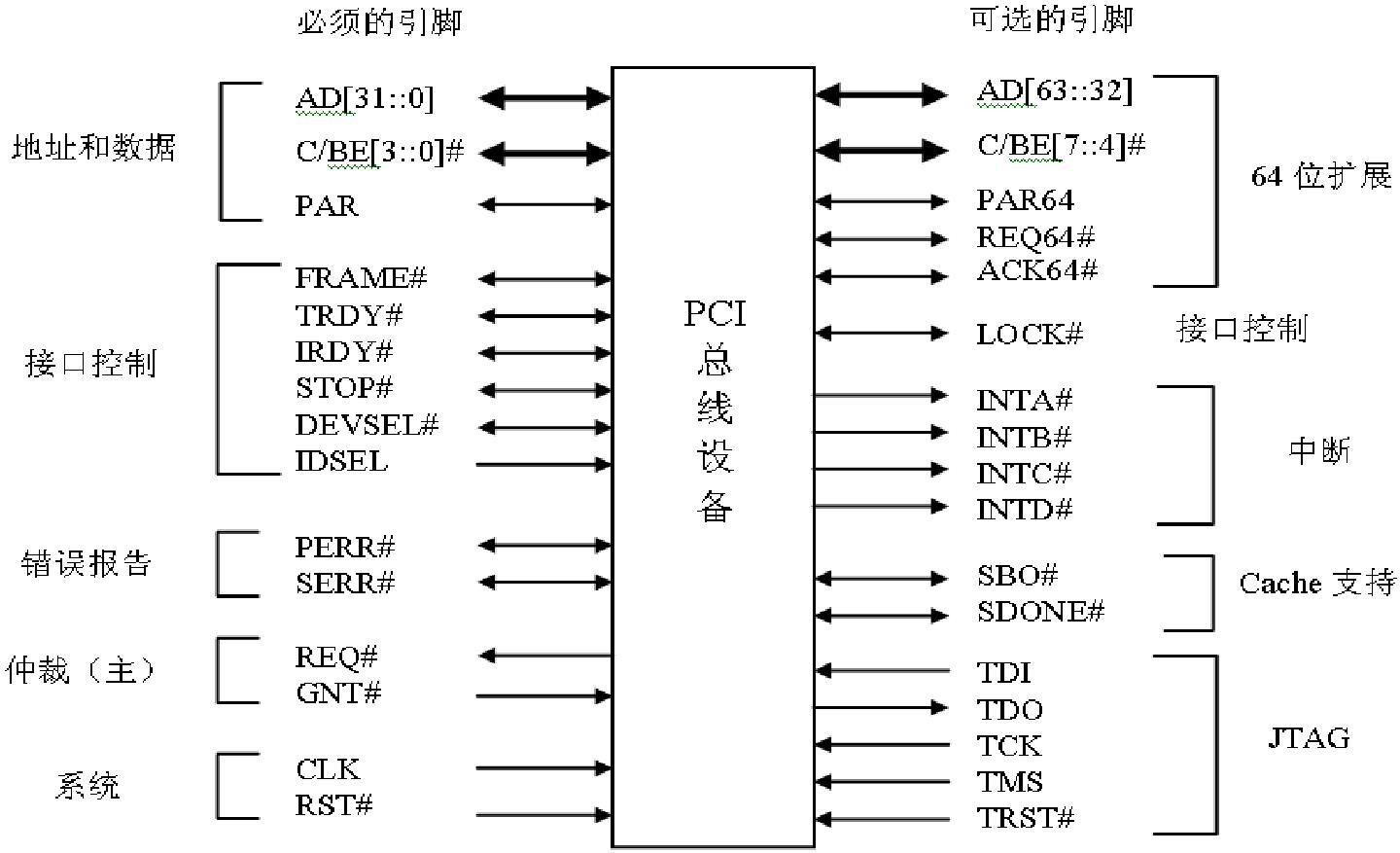

PCI总线

- PCI总线信号

地址和数据引脚

AD[31::0],AD[63::32]:64位地址和数据复用信号

C/BE[3::0]#,C/BE[7::4]#:命令和字节有效复用信号

PAR,PAR64:奇偶校验信号

接口控制引脚

FRAME#:帧信号,表示总线周期开始

IRDY#:初始方就绪信号

TRDY#:目标方就绪信号

STOP#:停止信号

DEVSEL#:设备选择信号

IDSEL#:初始化设备选择信号

LOCK#:封锁信号

- PCI总线周期

· I/O读写周期

主设备与I/O设备交换数据,不支持猝发传送

· 存储器读、存储器行读、存储器多重读周期

猝发读取不同的数据量

· 存储器写周期:猝发写入数据

· 存储器写和无效周期

保证写入,同时广播“无效”信息

· 中断响应周期:响应I/O设备中断

· 特殊周期:主设备广播信息到多个目标设备

· 双地址总线周期:传输64位地址

· 配置读和写周期

对PCI总线设备的配置信息进行读写,实现自动配置 - PCI总线时序

· 同步时序协议,数据传输需要两个阶段

第一个阶段(一个时钟):提供地址

第二个阶段(最少一个时钟):交换数据

· 非猝发传送需要2个时钟周期

· 支持无限猝发传送,第一个时钟提供地址,后续时钟交换数据,也就是2-1-1-1……

· 最大总线带宽

每个时钟传送64位数据,时钟频率66MHz

8×66 MB/S=528 MB/S

以上是关于微机总线的主要内容,如果未能解决你的问题,请参考以下文章