组成原理课程设计论文

Posted

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了组成原理课程设计论文相关的知识,希望对你有一定的参考价值。

参考技术A组成原理课程设计论文

当代,论文常用来指进行各个学术领域的研究和描述学术研究成果的文章,简称之为论文。它既是探讨问题进行学术研究的一种手段,又是描述学术研究成果进行学术交流的一种工具。它包括学年论文、毕业论文、学位论文、科技论文、成果论文等。接下来我为你带来组成原理课程设计论文,希望对你有帮助。

篇一:计算机组成原理实验报告

一、 实验名称:运算器实验

二、 实验目的:

1.学习数据处理部件的工作方式控制。 2. 学习机器语言程序的运行过程。

三、 实验原理:

CP226实验仪的运算器由一片CPLD实现,包括8种运算功能。运算时先将数据写到寄存器A和寄存器W中,根据选择的运算方式系统产生运算结果送到直通门D。

实验箱上可以向DBUS送数据的寄存器有:直通门D、左移门L、右移门R、程序计数器PC、中断向量寄存器IA、外部输入寄存器IN和堆栈寄存器ST。它们由138译码器的

四、 实验内容:

1. 计算37H+56H后左移一位的值送OUT输出。 2. 把36H取反同54H相与的值送人R1寄存器。

五、 实验步骤:

实验内容(一):

1. 关闭电源。用8位扁平线把J2和J1连接。

2. 用不同颜色的导线分别把K0和AEN、K1和WEN、K2和S0、K3和S1、K4和S2、

K6和X0、K7和X1、K8和X2、K9和OUT连接。 3. K15~K0全部放在1位,K23 ~K16放0位。

4. 注视仪器,打开电源,手不要远离电源开关,随时准备关闭电源,注意各数码管、

发光管的稳定性,静待10秒,确信仪器稳定、无焦糊味。 5. 设置实验箱进入手动模式。

6. 设置K0=0,K8K7K6=000,K23 ~K16=0011 0111。 7. 按下STEP键,在A寄存器中存入37。 8. 设置K0=1,K1=0,K23 ~K16=0101 0110。 9. 按下STEP键,在W寄存器中存入56。

10. 设置K0=1,K1=1,K8K7K6=110,K4K3K2=000。 11. 按下STEP键,L寄存器显示1A。 12. 设置K9=0,其他保持不变。

13. 按下STEP键,OUT寄存器显示1A。 14. 关闭实验箱电源。

实验内容(二):

1. 基本与实验内容(一)的前5个步骤相同(去掉连接OUT寄存器的导线)。 2. 连接K10和SA,K11和SB,K12和RWR。

3. 设置K0=0,K8K7K6=000,K23~K16=0011 0110。 4. 按下STEP键,A寄存器显示36。 5. 设置K8K7K6=100,K4K3K2=110。 6. 按下STEP键,A寄存器显示9C。

7. 设置K1K0=01,K8K7K6=000,K4K3K2=111,K23~K16=0100 0101。 8. 按下STEP键,W寄存器显示45。

9. 设置K1K0=11,K8K7K6=100,,4K3K2=011,K10K11=10,K12=0。 10. 按下STEP键,D寄存器和R1寄存器显示40。 11. 关闭实验箱电源。

六、 实验结论:

实现数据处理部件的工作方式控制和机器语言程序的运行过程。

七、 体会:

通过本次试验,我对运算器实验了解更深了并进一步巩固了第一周所学的内容。

八、 思考题:

如何计算3456H+12EFH的值? 答:

通过CP226实验仪,把S2S1S0设置为100,可以使用带进位加法运算。由于是四位16进制,可以把它拆开,从个位开始计算,一位一位向上计算通过带进位加法器,即算(64H*64H+64H*10H*3H+64H*3H+10H*9H+8h)+(64H*10H*4H+64H*8H+10H*4H+7H)

篇二:计算机组成原理实验报告

【实验环境】

1. Windows 2000 或 Windows XP

2. QuartusII、GW48-PK2或DE2-115计算机组成原理教学实验系统一台,排线若干。

【实验目的】

1、熟悉原理图和VHDL语言的编写。2、验证全加器功能。

【实验原理】

设计一个一位全加器,能完成两个二进制位的加法操作,考虑每种情况下的进位信号,完成8组数据的操作。

【实验步骤】

1.1建立工程项目

1.1.4 原理图设计

新建项目后,就可以绘制原理图程序了。下面以一位全加器如图1-12所示为例,讲解原理图的编辑输入的方法与具体步骤。

图1-12 一位全加器原理图

(1)执行菜单“File”→“New…”,或在工具栏中单击图标,弹出如图1-13所示的“New”对话框。在此对话框的“Design Files”项中选择“Block Diagram/Schematic File”,在单击“OK”按钮,QuartusⅡ10.0的主窗口进入如图1-14所示的原理图工作环境界面。

图1-13 “New”对话框

(2)在如图1-14所示的原理图工作环境界面中单击图标或在原理图编辑区的空白处双击鼠标或在原理图编辑区的空白处右键单击在弹出的菜单中选择“Insert”中的任意一个,弹出如图1-15所示的元件输入对话框,在“Name”栏中直接输入所需元件名或在“Libraries: ”的相关库中找到合适的元件,再单击“OK”按钮,然后在原理图编辑区中单击鼠标左键,即可将元件调入原理图编辑区中。为了输入如图1-12所示的原理图,应分别调入and2、xor2、or3、input、output。对于相同的器件,可通过复制来完成。例如3个and2门,器操作方法是,调入一个and2门后,在该器件上单击鼠标右键,在弹出的菜单中选择“Copy”命令将其复制,然后在合适的位置上右键,在弹出的菜单中选择“Paste”命令将其粘帖即可。1

图1-14 原理图工作环境界面

图1-15 元件输入对话框

如果元件放置好后,需要改元件的位置时,对于单个器件而言,在该器件上按住鼠标左键,拖到合适的位置后再松开鼠标左键即可;对于多个器件而言,应该按下鼠标左键框选需要移动的所有器件,然后将光标移动到选择的器件上,待光标变成可移动的“十”字光标,此时按住鼠标左键将其拖到合适的位置即可。

如果要删除元件时,应先将元件选中,然后按“Del”键或右键在弹出的菜单中选择“Del”。

如果要旋转元件时,应先将元件选中,然后右键在弹出的菜单中可选“Filp Horizontal”(水平翻转)、“Filp Vertical”(垂直翻转)、“Rotate by Degrees”(逆时针方向旋转,可选90°、180°、270°)等命令。

(3)将光标指向元件的引脚上,光标变成“十”字形状,按下鼠标左键并拖动,就会有导线引出,连接到另一端的元件上后,松开鼠标左键,即可绘制好一根导线,按此方法绘制好全部导线,如图1-16所示。

2

图1-16 导入元件和绘制导线(注意:用鼠标拖出的导线只能最多转一个弯)

图1-17 修改引脚名对话框

(4)双击或右键单击“pin_name”输入引脚,将弹出如图1-17所示的对话框。在此对话框的“Gerneral”页的“Pin name(s) ”项中输入引脚名,如:S,然后单击“确定”按钮,即可将“pin_name”输入引脚名改为“S”。按此方法依次修改其他引脚。修改后如图1-16所示。

(5)执行菜单命令“File”→ “Save…”,或在工具栏中单击

名并单击“保存”按钮即可(此时最好不要更改存储路径)。

图标,弹出“Save AS”对话框,在此对话框中输入文件

2.1 顶层VHDL文件设计

2.1.1 创建工程和编辑设计文件

首先建立工作库,以便设计工程项目的存储。任何一项设计都是一项工程(Project),都必须首先为此工程建立一个放置与此工程相关的所有文件的文件夹,此文件夹将被EDA软件默认为工作库(Work Library)。

在建立了文件夹后就可以将设计文件通过QuartusII的文本编辑器编辑并存盘,详细步骤如下:

1、新建一个文件夹。利用资源管理器,新建一个文件夹,如:e : eda 。注意,文件夹名不能用中文。

2、输入源程序。打开QuartusII,选择菜单“File”“New”,在New窗中的“Device Design Files”中选择编译文件的语言类型,这里选“VHDL Files”(如图2-1所示)。然后在VHDL文本编译窗中键入VHDL程序(如图2-2所示)。3

图2-1 选择编辑文件的语言类型

图2-2编辑输入设计文件(顶层设计文件ADD1.VHD)

图2-3利用“New Preject Wizard”创建工程

篇三:计算机组成原理实验2.2_实验报告

一、 实验目的与要求

(1) 掌握Cache 控制器的原理及其设计方法。

(2) 熟悉CPLD 应用设计及EDA 软件的使用。

二、 实验设备

PC 机一台,TD-CM3+或TD-CMX 实验系统一套。

三、 实验原理

本实验采用的地址变换是直接映象方式,这种变换方式简单而直接,硬件实 现很简单,访问速度也比较快,但是块的冲突率比较高。其主要原则是:主存中一块只能映象到Cache 的一个特定的块中。

假设主存的块号为B,Cache 的块号为b,则它们之间的映象关系可以表示 为:b = B mod Cb

其中,Cb 是Cache 的块容量。设主存的块容量为Mb,区容量为Me,则直接 映象方法的关系如图2-2-1 所示。把主存按Cache 的大小分成区,一般主存容量为Cache 容量的整数倍,主存每一个分区内的块数与Cache 的总块数相等。直接映象方式只能把主存各个区中相对块号相同的那些块映象到Cache 中同一块号的那个特定块中。例如,主存的块0 只能映象到Cache 的块0 中,主存的块1 只能映象到Cache 的块1 中,同样,主存区1 中的块Cb(在区1 中的相对块号是0)

也只能映象到 Cache 的块0 中。根据上面给出的地址映象规则,整个Cache 地址与主存地址的低位部分是完全相同的。

直接映象方式的地址变换过程如图2-2-2 所示,主存地址中的块号B 与Cache 地址中的块号b 是完全相同的。同样,主存地址中的块内地址W 与Cache 地址中的块内地址w 也是完全相同的,主存地址比Cache 地址长出来的部分称为区号E。

1

在程序执行过程中,当要访问 Cache 时,为了实现主存块号到Cache 块号的变换,需要有一个存放主存区号的小容量存储器,这个存储器的容量与Cache 的块数相等,字长为主存地址中区号E 的.长度,另外再加一个有效位。

在主存地址到Cache 地址的变换过程中,首先用主存地址中的块号去访问区号存储器(按地址访问)。把读出来的区号与主存地址中的区号E 进行比较,根据比较结果和与区号在同一存储字中的有效位情况作出处理。如果区号比较结果相等,有效位为‘1’,则Cache 命中,表示要访问的那一块已经装入到Cache 中了,这时Cache 地址(与主存地址的低位部分完全相同)是正确的。用这个Cache 地址去访问Cache,把读出来的数据送往CPU。其他情况均为Cache没有命中,或称为Cache 失效,表示要访问的那个块还没有装入到Cache 中,这时,要用主存地址去访问主存储器,先把该地址所在的块读到Cache 中,然后CPU 从Cache 中读取该地址中的数据。

本实验要在CPLD 中实现Cache 及其地址变换逻辑(也叫Cache 控制器),采用直接相联地址变换,只考虑CPU 从Cache 读数据,不考虑CPU 从主存中读数据和写回数据的情况,Cache和CPU 以及存储器的关系如图2-2-3 所示。

Cache 控制器顶层模块如图2-2-4 所示,主存地址为A7A0,共8 位,区号E 取3 位,这样Cache 地址还剩5 位,所以Cache 容量为32 个单元,块号B 取3 位,那么Cache 分为8 块,块内地址W 取2 位,则每块为4 个单元。图2-2-4 中,WCT 为写Cache 块表信号,CLR 为系统总清零信号,A7A0 为CPU 访问内存的地址,M 为Cache 失效信号,CA4CA0 为Cache 地址,

2

MD7MD0 为主存送Cache 的数据,D7D0 为Cache 送CPU 数据,T2 为系统时钟, RD 为CPU 访问内存读信号,LA1 和LA0 为块内地址。

在 QuartusII 软件中先实现一个8 位的存储单元(见例程中的MemCell.bdf),然后用 这个8位的存储单元来构成一个32 X 8 位的Cache(见例程中的CacheMem.bdf),这样就实现了Cache的存储体。

再实现一个4 位的存储单元(见例程中的TableCell.bdf),然后用这个4 位的存储单

元

来构成一个8 X 4 位的区表存储器,用来存放区号和有效位(见例程中的CacheTable.bdf),在这个文件中,还实现了一个区号比较器,如果主存地址的区号E 和区表中相应单元中的区号相等,且有效位为1,则Cache 命中,否则Cache 失效,标志为M,M 为0 时表示Cache 失效。

当Cache 命中时,就将Cache 存储体中相应单元的数据送往CPU,这个过程比较简单。 当Cache 失效时,就将主存中相应块中的数据读出写入Cache 中,这样Cache 控制器就要产生访问主存储器的地址和主存储器的读信号,由于每块占四个单元,所以需要连续访问四次主存,这就需要一个低地址发生器,即一个2 位计数器(见例程中的Counter.vhd),将低2 位和CPU 给出的高6 位地址组合起来,形成访问主存储器的地址。M 就可以做为主存的读信号,这样,在时钟的控制下,就可以将主存中相应的块写入到Cache 的相应块中,

最后再修改区表(见例程中的(CacheCtrl.bdf)。

四、 实验步骤

1、实验接线:

3

2、实验步骤:

(1) 使用Quartus II 软件编辑实现相应的逻辑并进行编译,直到编译通过,Cache 控

制

器在EPM1270 芯片中对应的引脚如图2-2-5 所示,框外文字表示I/O 号,框内文字表示该引脚的含义(本实验例程见‘安装路径Cpld CacheCtrlCacheCtrl.qpf’工程)

(2) 关闭实验系统电源,按图2-2-6 连接实验电路,并检查无误,图中将用户需要连接的信号用圆圈标明。

(3) 打开实验系统电源,将生成的POF 文件下载到EMP1270 中去,CPLD 单元介绍见实验1.2。

(4) 将时序与操作台单元的开关KK3 置为‘运行’档,CLR 信号由CON 单元的CLR 模拟给出,按动CON 单元的CLR 按钮,清空区表。

(5) 预先往主存写入数据:联机软件提供了机器程序下载功能,以代替手动读写主存,机器程序以指定的格式写入到以TXT 为后缀的文件中。

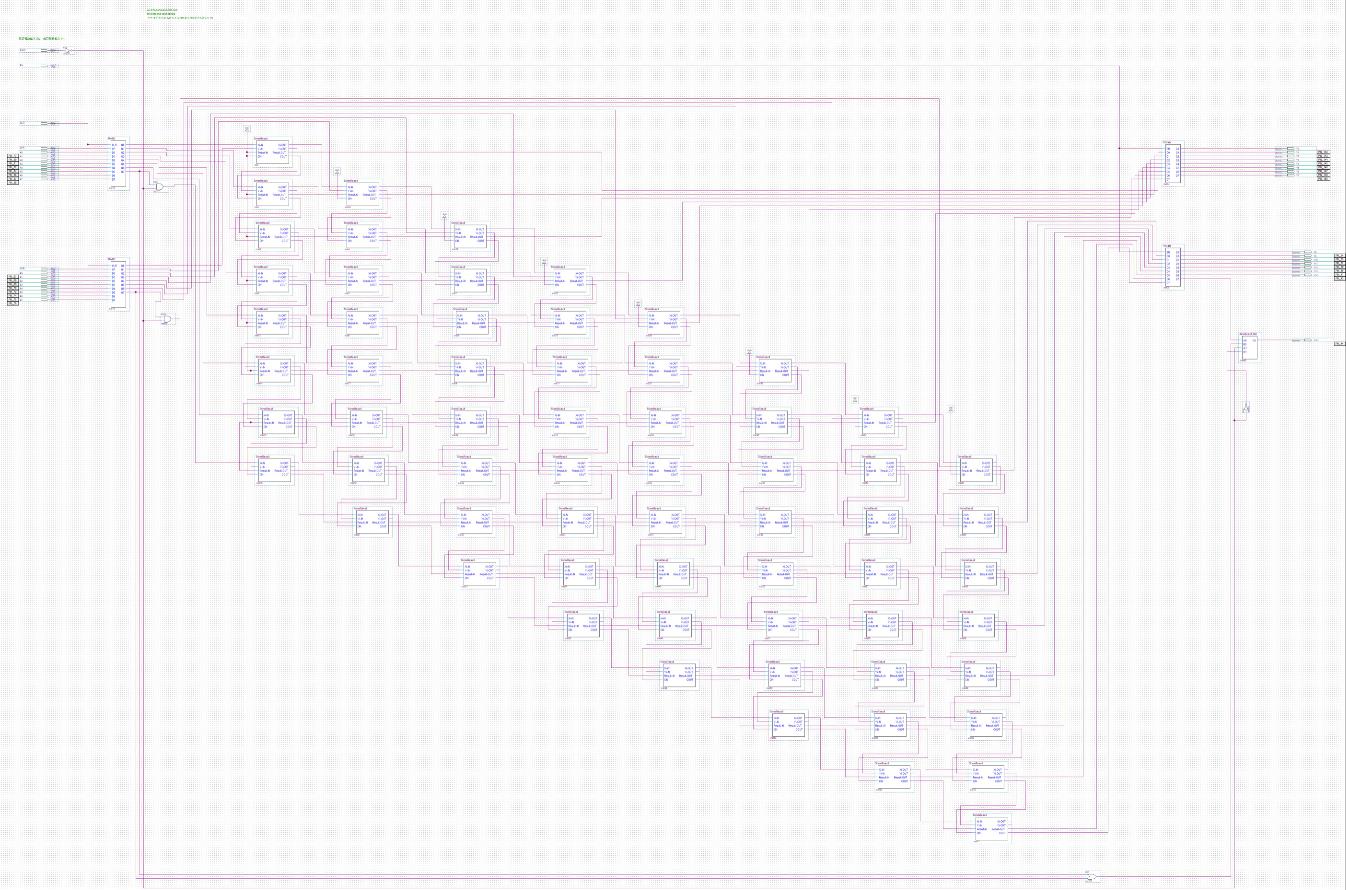

;山东大学软件学院计算机组成原理课程设计整机实验

一、实验时间

2021年5月20日,12周

2021年5月27日,13周,整机实验检查,打分

二、实验任务

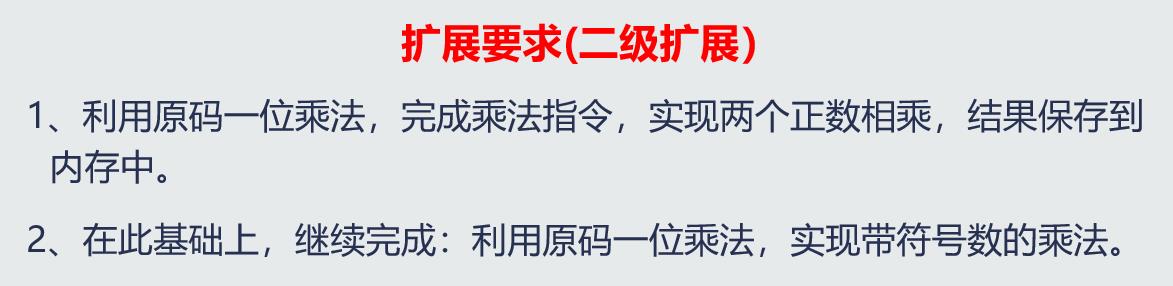

完成整机实验的拓展功能2:两个正数相乘+带符号的原码一位乘

注意乘法的拓展分为两步

第一步:两个正数的原码一位乘

第二步:带符号数的原码一位乘

三、对实验要求的理解

在拓展要求2中,第一步拓展实现的是正数的原码一位乘,由于对于正数来说,原码和补码是一样的,因此不需要转换

但如果要实现带符号位的原码一位乘,由于负数的补码和原码不一样,因此需要用对二求补器将运算前的数据由补码转为原码,运算后的原码转成补码,并存入内存中

这个拓展的实现有多种思路,有的实验老师要求比较严格,要求所有数据必须全部经过一个ALU,但我们实验老师要求比较松,可以用阵列乘法器实现乘法,因此对于这个功能,我使用了阵列乘法器实现

对于另一种实现方式,比较麻烦,我没有研究,但也有很多人做出来了

由于我采用了比较简单的阵列乘法器实现最终的乘法,对于其它人的参考价值不大,因此本博客到整机实验结束后才最终更新

四、具体实现

4.1 具体实现思路

下面介绍我对乘法的具体实现方法

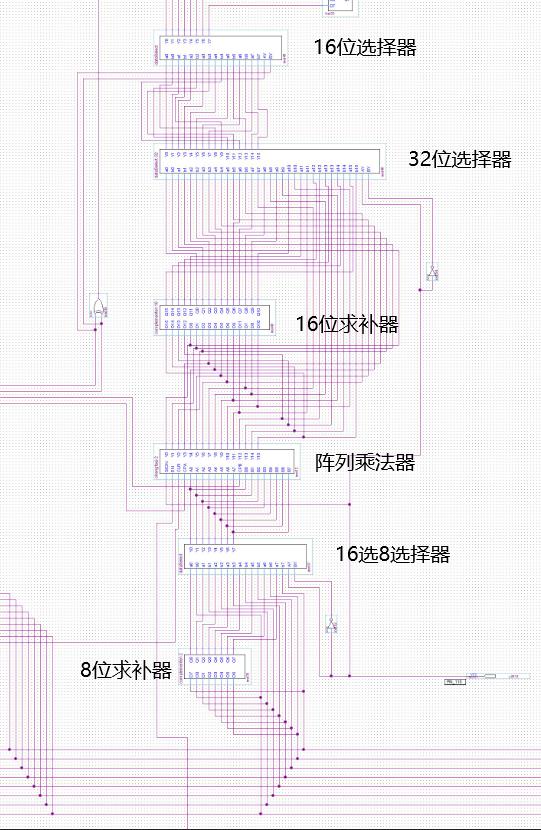

- 使用LOAD指令取出两个数,存放到寄存器组的R0和R1中

- 从R0和R1分别取出乘法的两个数,经过对二求补器后打入阵列乘法器的A寄存器和B寄存器

- 乘法结果经过16位对2求补器,将结果转换为补码

- 通过2路选择器选择乘法结果16位的高8位输出,保存在R1中

- 通过2路选择器选择乘法结果16位的低8位输出,保存在R0中

- 将R0和R1里保存的结果存储到内存中

使用阵列乘法器相当于将乘法的难度缩减为加法

其中,输入使用了8位对2求补器,乘法结果输出使用了16位对2求补器

具体的微操作如图

MUL Ri,Rj

乘法指令为双字长,第一字长给定OP和寄存器打入脉冲

第二字长仅给定寄存器打入脉冲

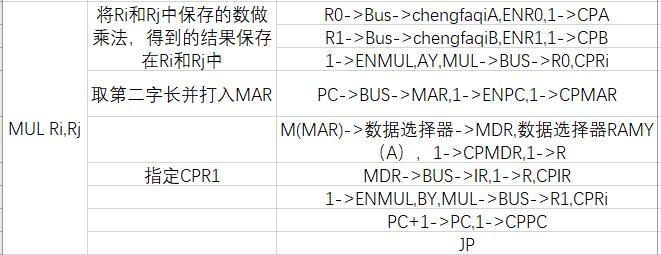

STOREMUL

乘法存数指令,第一字长给定OP+寄存器打入脉冲

第二字长给定乘法结果高8位存数地址

第三字长给定乘法结果低8位存数地址

4.2 对2求补器

8位对2求补器,符号位不变,当符号位为1时,启动求补,符号位为0时,直接输出原数据

对二求补器的工作原理是,总后向前,找到第一个1,这个1不变,前面的全部取反(除符号位以外)

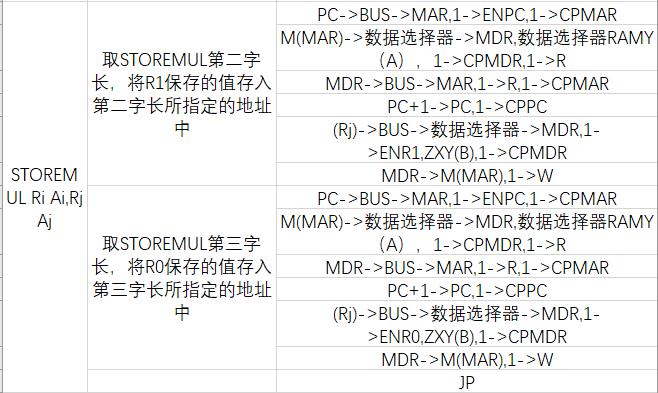

4.3 阵列乘法器

阵列乘法器由于图太大(大于5MB),传不上来,这里只能传一个模糊的图

4.4 乘法器区域图

输入使用8位对2求补器将补码转换为原码,输出使用16位对2求补器将乘法结果由原码转换为补码

另外,由于我的阵列乘法器实现的是两个正数相乘(最高位位1时也是正数),因此这里输入用了直送和通过求补器两种方式,输出同样提供了两种方式,但事实上,由于计算机中存储的是有符号补码,当最高位为1时,一定是有符号数,因此不需要这么麻烦。这是由于我开始时没考虑到,后来才意识到。实际上应该做简化处理,不需要这么多选择器,只要让输入输出都经过求补器就可以了

五、检查中老师问的问题

1.有哪些部件的输出连了总线?

要求说出,并且在电路图上指出

2.寄存器组的输入输出问题,寄存器组怎么输入,怎么输出

3.JO指令的实现原理

4.原理图输入的步骤(总共7步,在ppt上)

- 创建项目

- 建立原理图设计文件

- 目标器件选择

- 项目的编译(由编译器完成)

- 引脚分配(引脚绑定)

- 编程下载

- 生成器件符号图(生成.bsf文件,供上层项目文件使用)

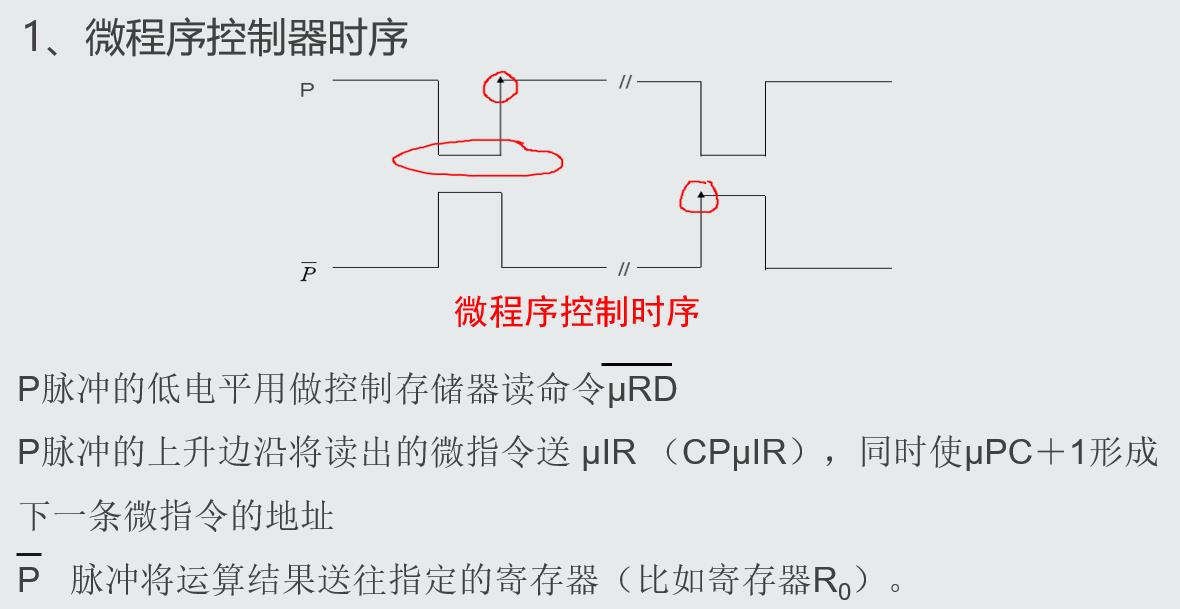

5.脉冲的时序问题

六、后记

计算机组成原理课程设计就这样结束了,因为多数实验老师不让用阵列乘法器,因此这篇文章对后人的参考价值不大。但作为计组课设完整性的记录,我觉得还是应该把这篇文章发出来。在计组课设的过程中,遇到了很多的困难,中途还改了一次图的结构和微指令,但最后还是实现了基本和拓展的功能。在这个过程中,和老师同学们讨论,总结经验,克服了一个又一个的困难,在这里也感谢老师和其它同学对我的帮助。而计组课设的实验过程,也会成为我大学的一段美好的回忆。

以上是关于组成原理课程设计论文的主要内容,如果未能解决你的问题,请参考以下文章