山东大学软件学院计算机组成原理课程设计整机实验

Posted 叶卡捷琳堡

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了山东大学软件学院计算机组成原理课程设计整机实验相关的知识,希望对你有一定的参考价值。

一、实验时间

2021年5月20日,12周

2021年5月27日,13周,整机实验检查,打分

二、实验任务

完成整机实验的拓展功能2:两个正数相乘+带符号的原码一位乘

注意乘法的拓展分为两步

第一步:两个正数的原码一位乘

第二步:带符号数的原码一位乘

三、对实验要求的理解

在拓展要求2中,第一步拓展实现的是正数的原码一位乘,由于对于正数来说,原码和补码是一样的,因此不需要转换

但如果要实现带符号位的原码一位乘,由于负数的补码和原码不一样,因此需要用对二求补器将运算前的数据由补码转为原码,运算后的原码转成补码,并存入内存中

这个拓展的实现有多种思路,有的实验老师要求比较严格,要求所有数据必须全部经过一个ALU,但我们实验老师要求比较松,可以用阵列乘法器实现乘法,因此对于这个功能,我使用了阵列乘法器实现

对于另一种实现方式,比较麻烦,我没有研究,但也有很多人做出来了

由于我采用了比较简单的阵列乘法器实现最终的乘法,对于其它人的参考价值不大,因此本博客到整机实验结束后才最终更新

四、具体实现

4.1 具体实现思路

下面介绍我对乘法的具体实现方法

- 使用LOAD指令取出两个数,存放到寄存器组的R0和R1中

- 从R0和R1分别取出乘法的两个数,经过对二求补器后打入阵列乘法器的A寄存器和B寄存器

- 乘法结果经过16位对2求补器,将结果转换为补码

- 通过2路选择器选择乘法结果16位的高8位输出,保存在R1中

- 通过2路选择器选择乘法结果16位的低8位输出,保存在R0中

- 将R0和R1里保存的结果存储到内存中

使用阵列乘法器相当于将乘法的难度缩减为加法

其中,输入使用了8位对2求补器,乘法结果输出使用了16位对2求补器

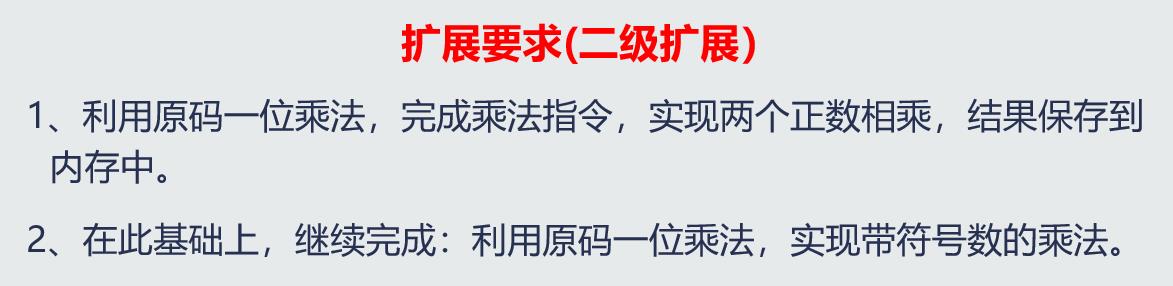

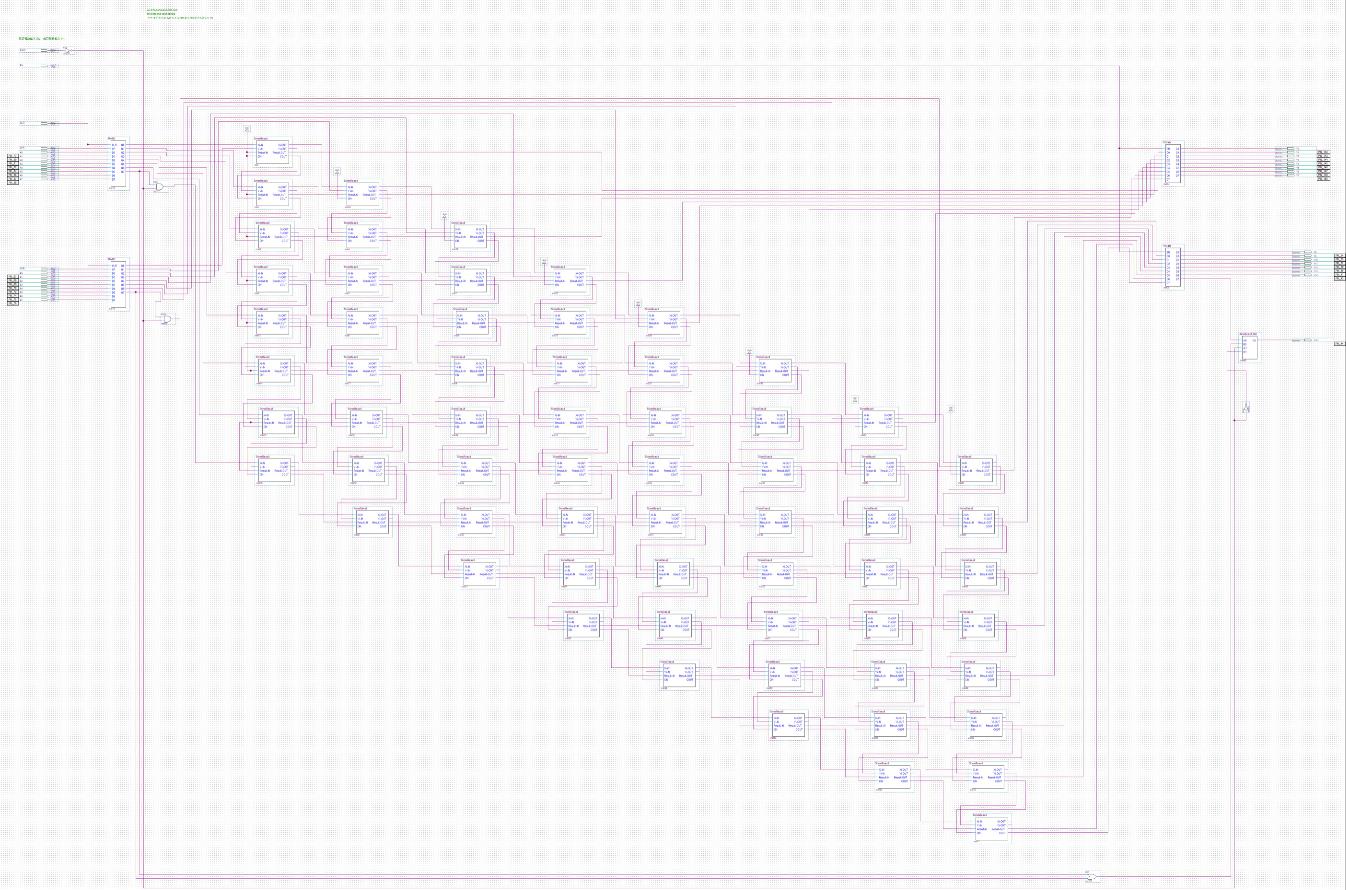

具体的微操作如图

MUL Ri,Rj

乘法指令为双字长,第一字长给定OP和寄存器打入脉冲

第二字长仅给定寄存器打入脉冲

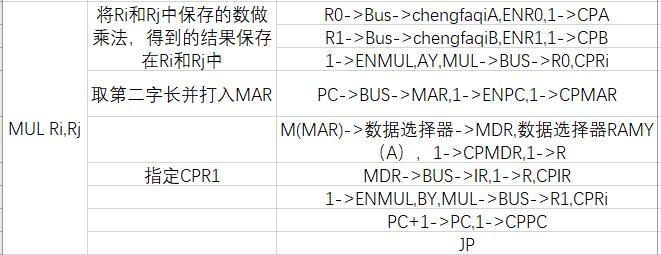

STOREMUL

乘法存数指令,第一字长给定OP+寄存器打入脉冲

第二字长给定乘法结果高8位存数地址

第三字长给定乘法结果低8位存数地址

4.2 对2求补器

8位对2求补器,符号位不变,当符号位为1时,启动求补,符号位为0时,直接输出原数据

对二求补器的工作原理是,总后向前,找到第一个1,这个1不变,前面的全部取反(除符号位以外)

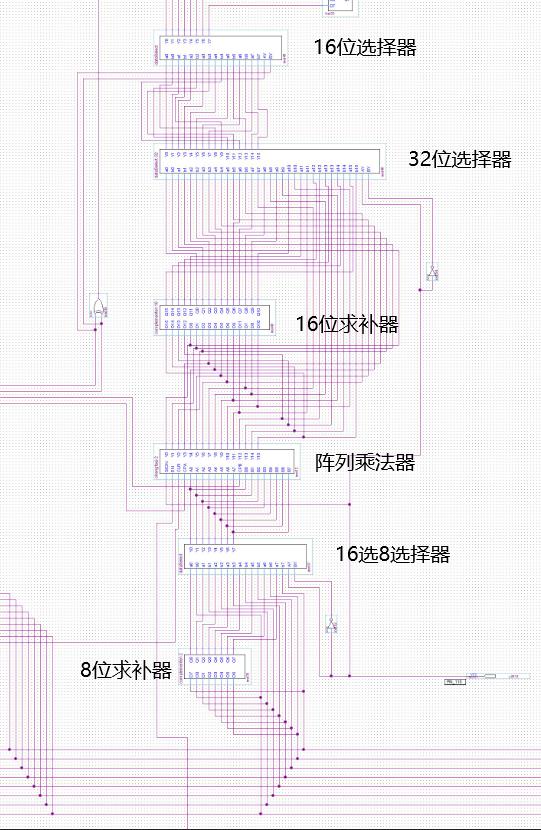

4.3 阵列乘法器

阵列乘法器由于图太大(大于5MB),传不上来,这里只能传一个模糊的图

4.4 乘法器区域图

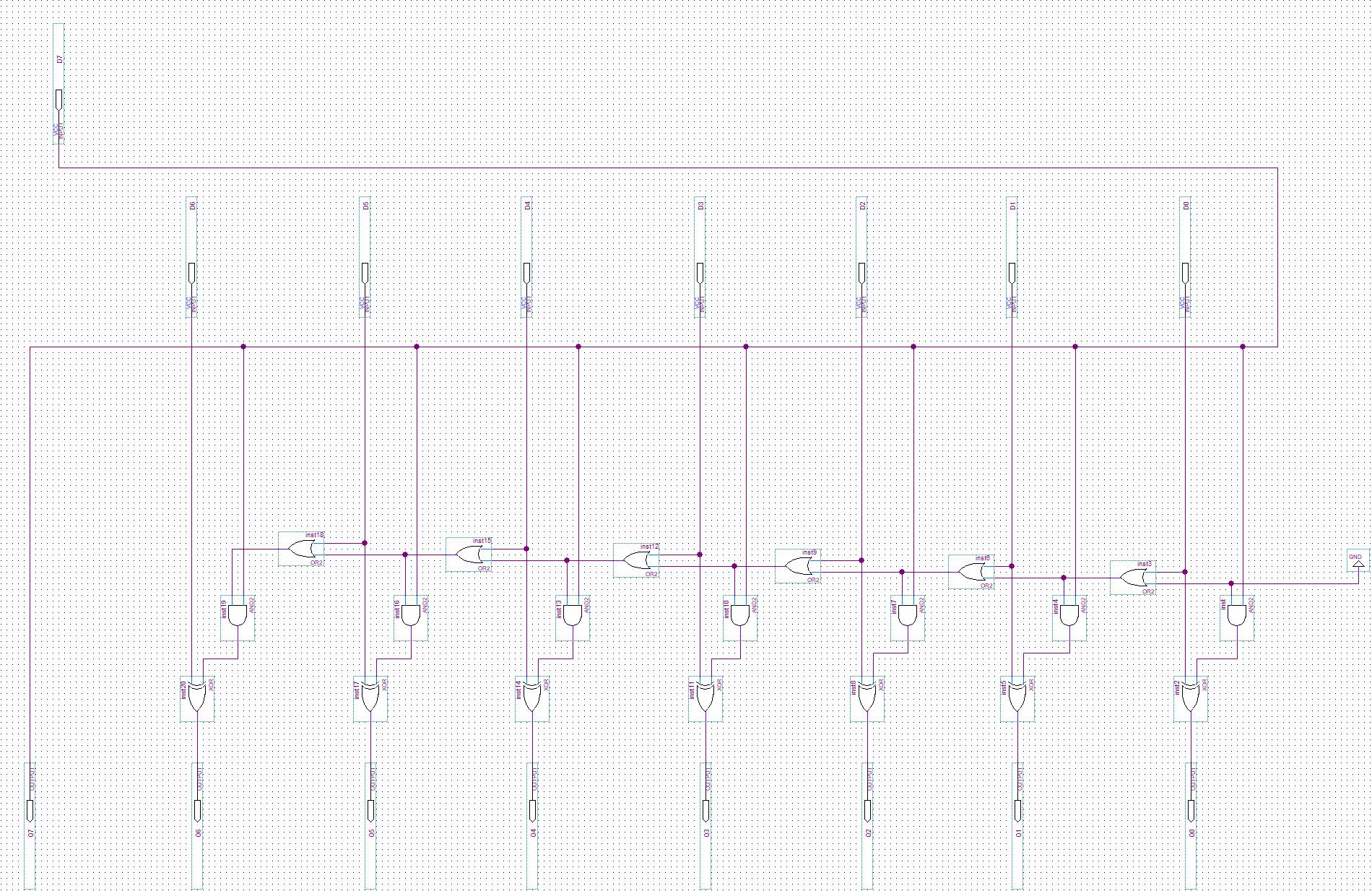

输入使用8位对2求补器将补码转换为原码,输出使用16位对2求补器将乘法结果由原码转换为补码

另外,由于我的阵列乘法器实现的是两个正数相乘(最高位位1时也是正数),因此这里输入用了直送和通过求补器两种方式,输出同样提供了两种方式,但事实上,由于计算机中存储的是有符号补码,当最高位为1时,一定是有符号数,因此不需要这么麻烦。这是由于我开始时没考虑到,后来才意识到。实际上应该做简化处理,不需要这么多选择器,只要让输入输出都经过求补器就可以了

五、检查中老师问的问题

1.有哪些部件的输出连了总线?

要求说出,并且在电路图上指出

2.寄存器组的输入输出问题,寄存器组怎么输入,怎么输出

3.JO指令的实现原理

4.原理图输入的步骤(总共7步,在ppt上)

- 创建项目

- 建立原理图设计文件

- 目标器件选择

- 项目的编译(由编译器完成)

- 引脚分配(引脚绑定)

- 编程下载

- 生成器件符号图(生成.bsf文件,供上层项目文件使用)

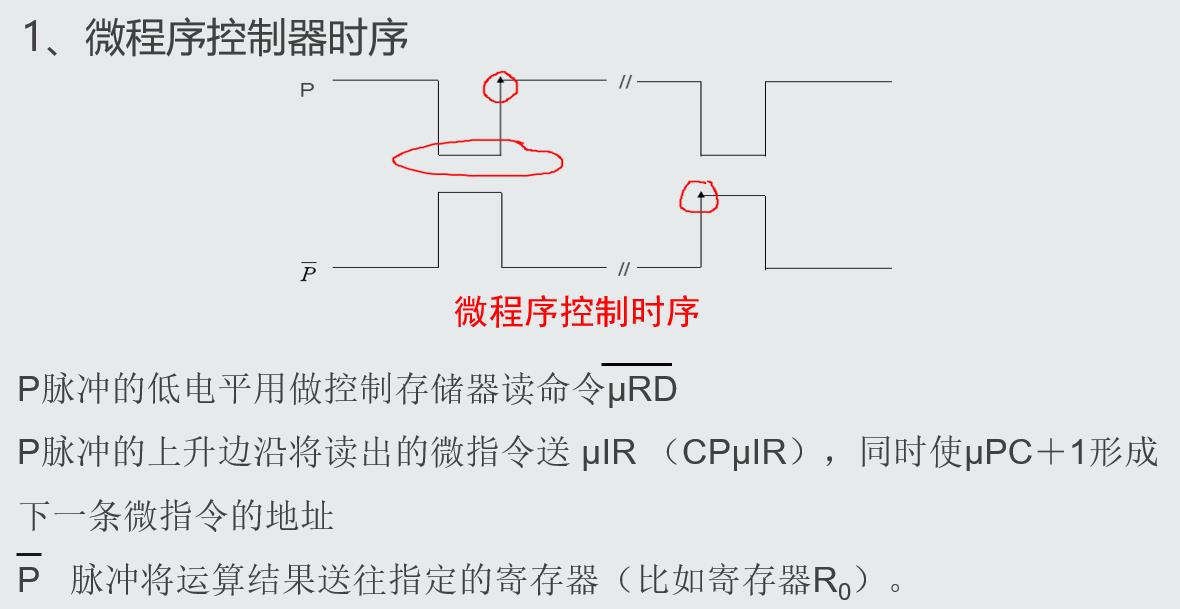

5.脉冲的时序问题

六、后记

计算机组成原理课程设计就这样结束了,因为多数实验老师不让用阵列乘法器,因此这篇文章对后人的参考价值不大。但作为计组课设完整性的记录,我觉得还是应该把这篇文章发出来。在计组课设的过程中,遇到了很多的困难,中途还改了一次图的结构和微指令,但最后还是实现了基本和拓展的功能。在这个过程中,和老师同学们讨论,总结经验,克服了一个又一个的困难,在这里也感谢老师和其它同学对我的帮助。而计组课设的实验过程,也会成为我大学的一段美好的回忆。

以上是关于山东大学软件学院计算机组成原理课程设计整机实验的主要内容,如果未能解决你的问题,请参考以下文章