零基础学FPGA:FPGA时钟架构(Xilinx为例,完整解读)

Posted 千歌叹尽执夏

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了零基础学FPGA:FPGA时钟架构(Xilinx为例,完整解读)相关的知识,希望对你有一定的参考价值。

目录

日常·唠嗑

不知不觉已经离开校园,工作了4个月。上班后,发现自己在学校学习的,其实都是些皮毛,所以一直不敢更新这个专栏(前面几篇文章,如果有错误的地方,笔者在这里期待大家批评指正)。要真正了解FPGA,其实不应该从表面应用开始,也不是一开始像学单片机那样敲代码,而是应该了解,何为FPGA?

何为FPGA,其实应该从FPGA的架构开始了解起,FPGA的基本组成,时钟单元结构等等。平时要上班,周末又想休息,所以也是经常偷懒。😂

这里对于逻辑单元等结构,暂时先不写,等后面抽空了,我再写了,补充到前面来。这里先描述一下FPGA时钟架构,以Xilinx 7系列FPGA为例子,下篇文章写Altera,感兴趣的同学,可以关注下一篇文章。

网上其实有很多文章都对7系列的时钟架构做了概述,这里为什么还要选这个系列再啰嗦一次呢?因为很多文章都是抛开软件讲架构,或者抛开文档讲,软件跟技术文档没有配套起来研读,读者看起来,会有那种云里雾里的感觉,这里将Vivado工具+官方文档配套起来读,希望能帮到大家。

本篇文章,历时半个月,篇幅较长,可以分段耐心看完。

一、时钟资源(及布线)概述

在Xilinx官方文档中(UG472),该章节也叫时钟体系结构概述(Clocking Architecture Overview),时钟路由资源概述(Clock Routing Resources Overview)。

7系列FPGA时钟资源通过专用的全局和区域I/O和时钟资源管理符合复杂和简单的时钟要求。时钟管理块(CMT)提供时钟频率合成、减少偏移和抖动过滤等功能。非时钟资源,如本地布线(路由),不推荐用于时钟功能。

7系列芯片时钟资源划分为全局时钟资源及区域时钟资源,因为翻译可能有误,这里引言官方文档描述,较为准确。

全局时钟资源:

• Global clock trees allow clocking of synchronous elements across the device.

全局时钟树允许同步模块时钟跨越整个FPGA器件。

• I/O and regional clock trees allow clocking of up to three vertically adjacent clock regions.

I/O时钟和区域时钟树允许最多为三个垂直相邻的时钟区域提供时钟。

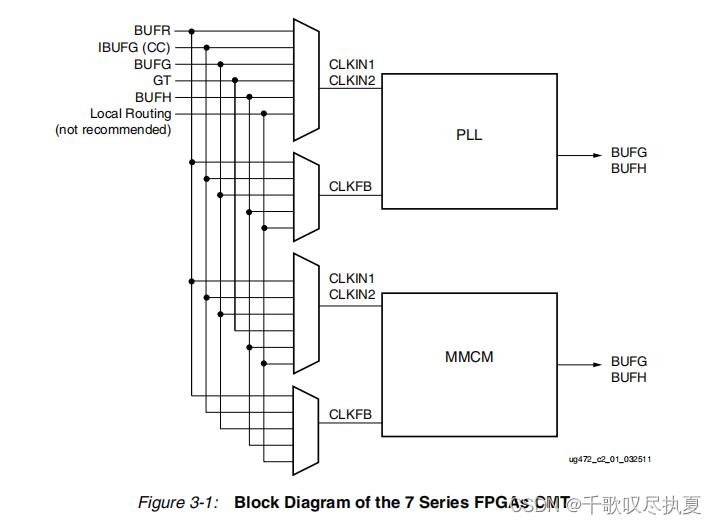

• CMTs, each containing one mixed-mode clock manager (MMCM) and one phase-locked loop (PLL), reside in the CMT column next to the I/O column.

每个CMT包含一个混合模式时钟管理器(MMCM)和一个锁相环(PLL),位于I/O列旁边的CMT列中。

区域时钟资源:

• The number of clock regions varies with device size, from one clock region in the

smallest device to 24 clock regions in the largest one.

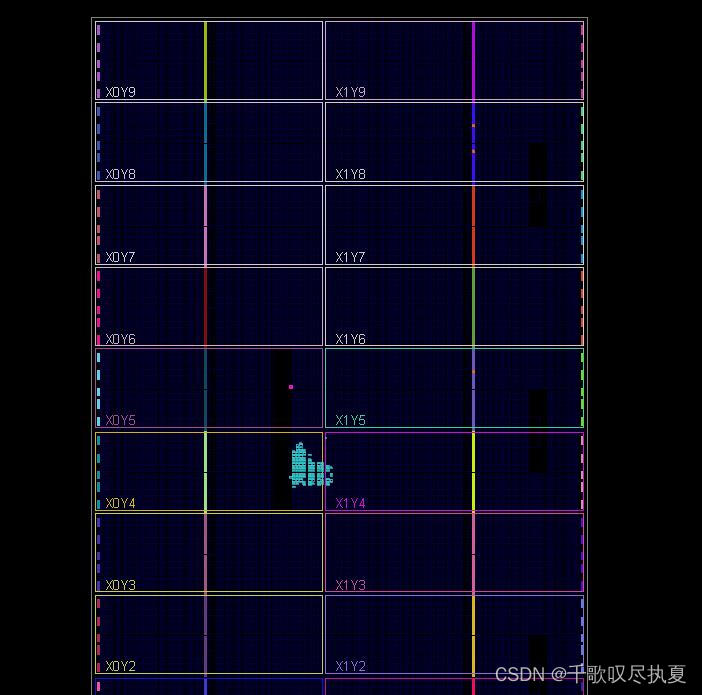

时钟区域的数量随器件大小而变化,从最小器件的一个时钟区域到最大器件中的24个时钟区域。(换句话说就是,不同芯片时钟区域数量不一样,小的芯片时钟区域分布得比较少,具体可以对比图1跟图2)

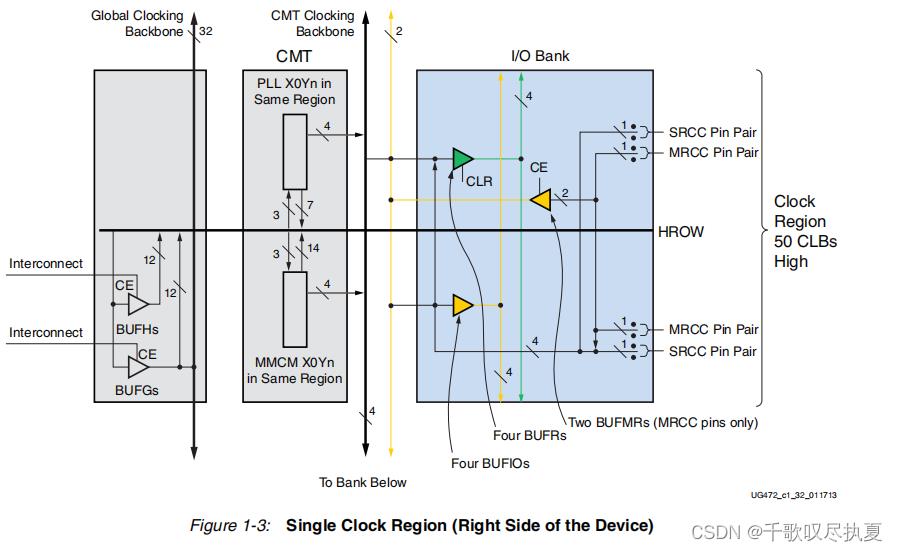

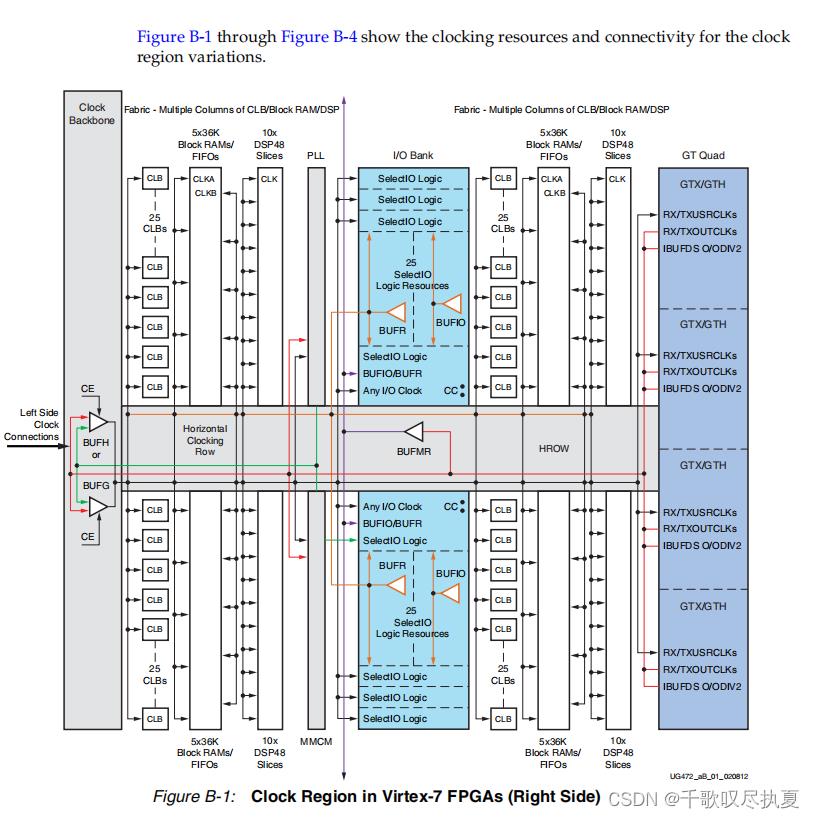

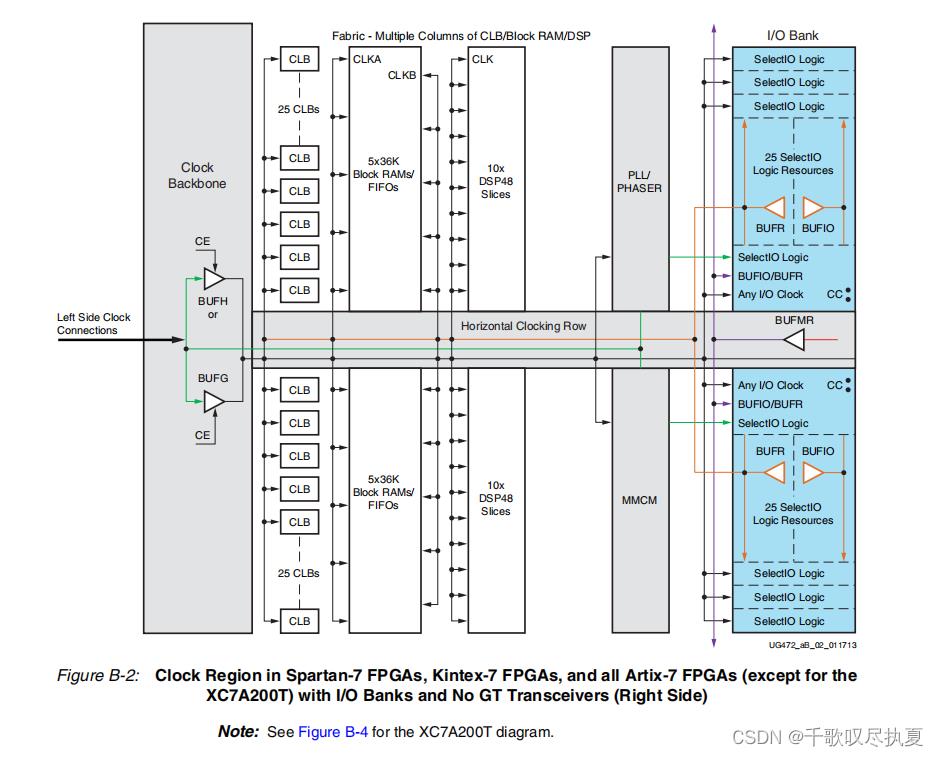

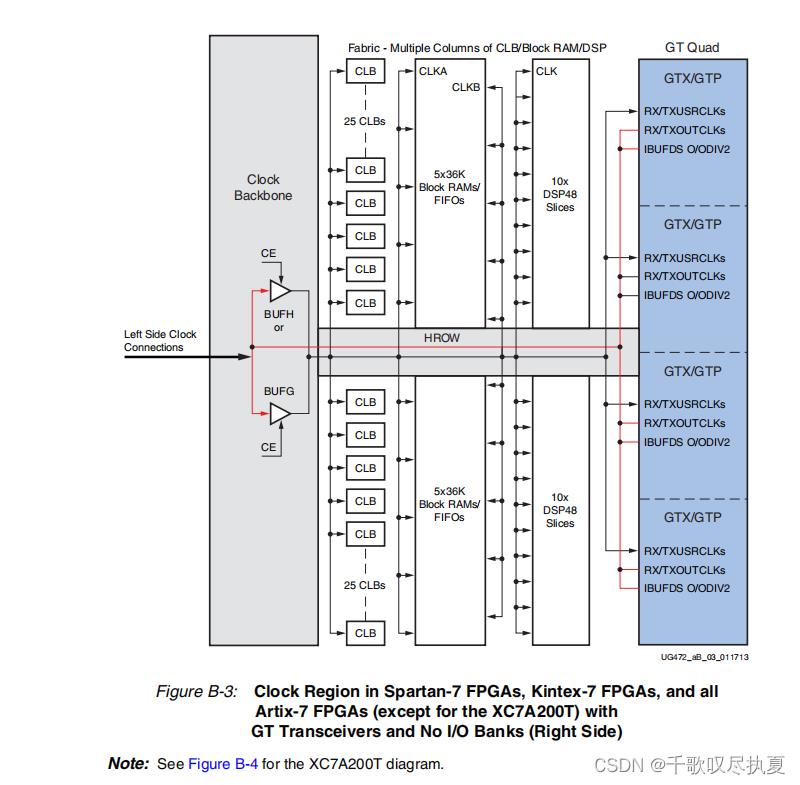

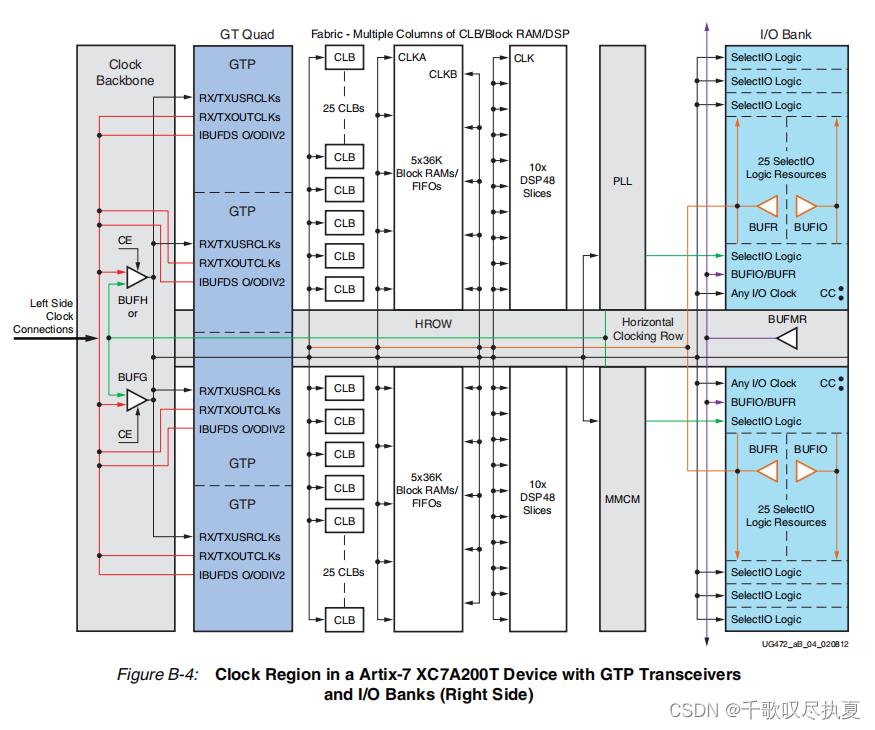

• A clock region includes all synchronous elements (for instance: CLB, I/O, serial transceivers, DSP, block RAM, CMT) in an area spanning 50 CLBs and one I/O bank (50 I/Os), with a horizontal clock row (HROW) in its center.

时钟区域包括50个CLB和一个I/O bank(50个I/O)的区域中的所有同步模块

(例如:CLB、I/O、串行收发器、DSP、块RAM、CMT),其中心有一个水平时钟行(HROW)。

• Each clock region spans 25 CLBs up and 25 CLBs down from the HROW, and horizontally across each side of the device.

每个时钟区域从HROW向上和向下跨越25个CLB,并水平跨越器件的每一侧。

关于Bank:

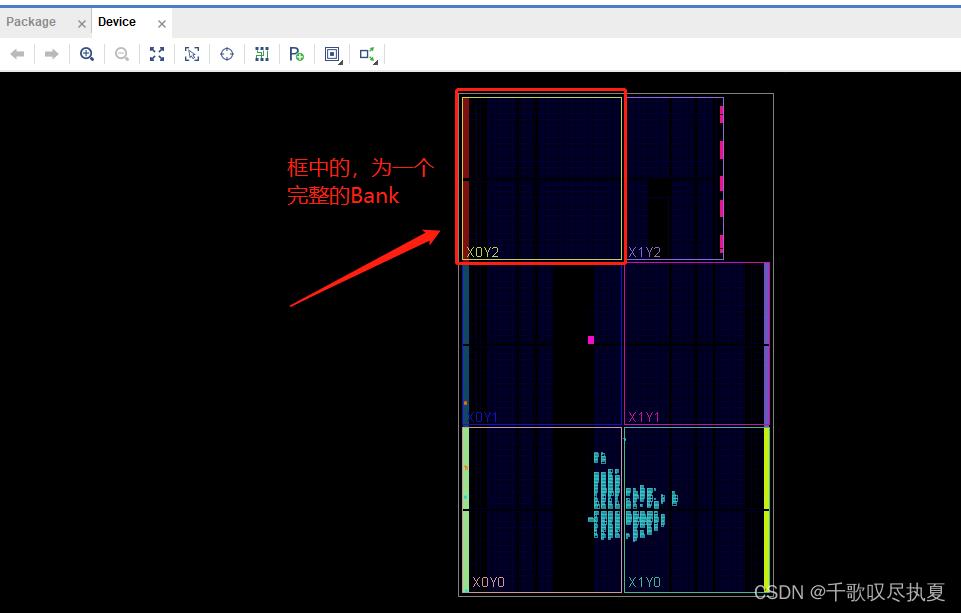

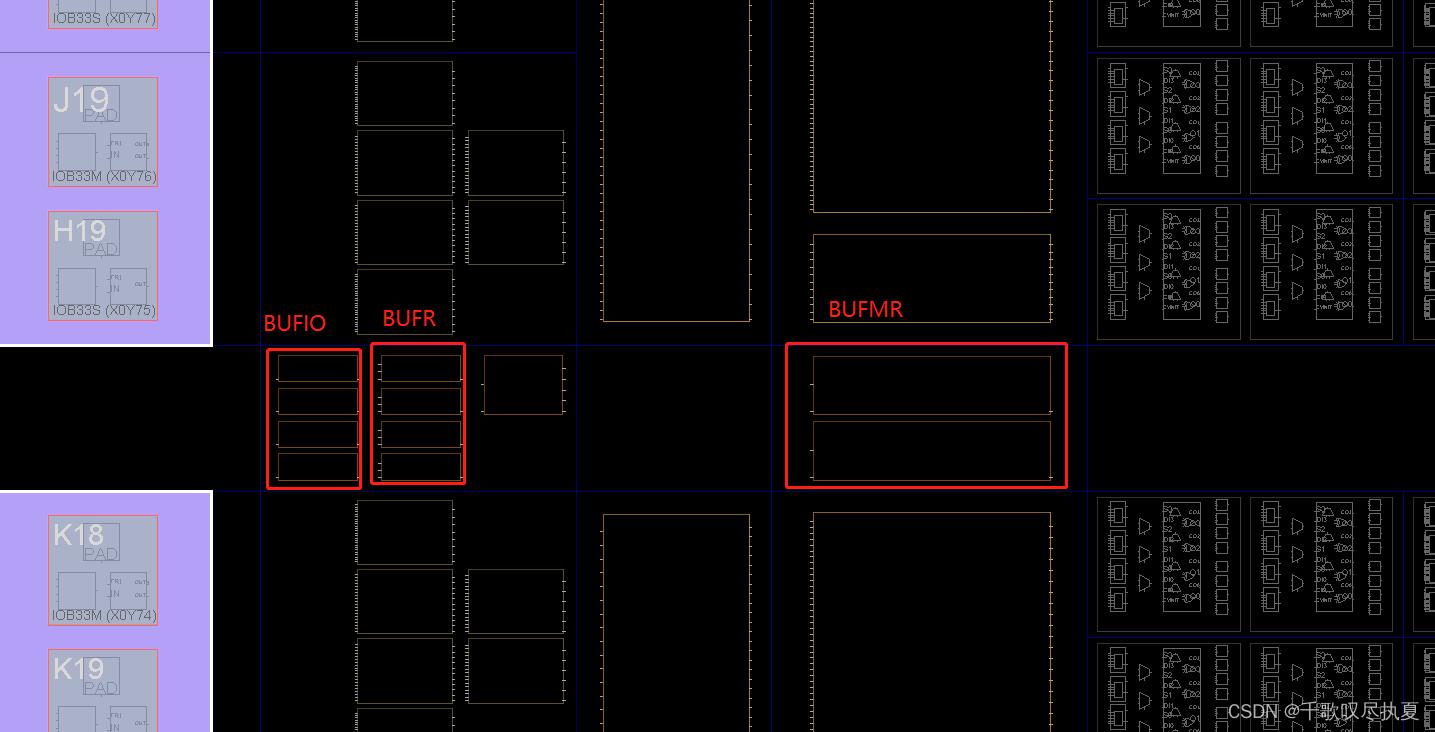

在Vivado通过综合、布局布线后,可以打开一个Device界面(资源界面)(不知道在哪打开的,点一下左侧导航栏的Open Implemented Design),这个工程用的是Artix-7 50T-324封装的芯片,从截图上看有5个Bank,右上角那个是Bank0(配置用的,不算在这5个用户Bank里面)。

在这里讲Bank有点超纲了,应该是放在FPGA整体结构的篇幅讲的,这里因为要理解时钟架构,只能先简单描述一下。(下一章对Bank还会有补充)

图1:

图2:Virtex-7芯片

二、时钟架构-解读

2.1、时钟整体架构

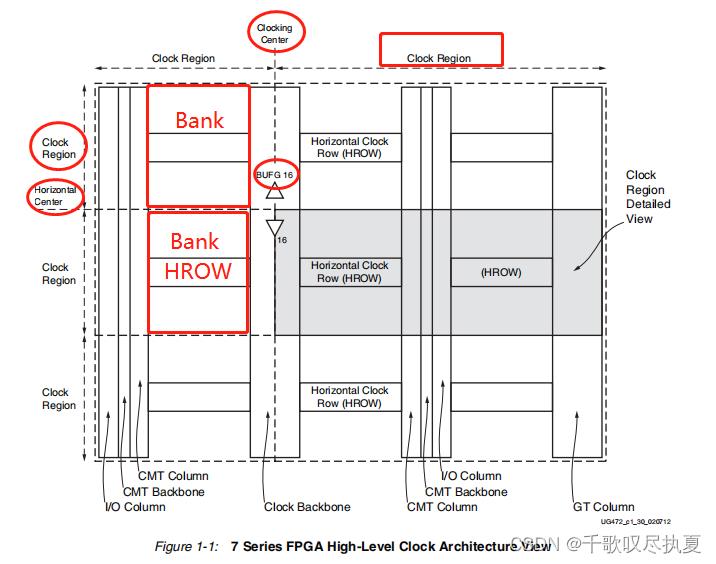

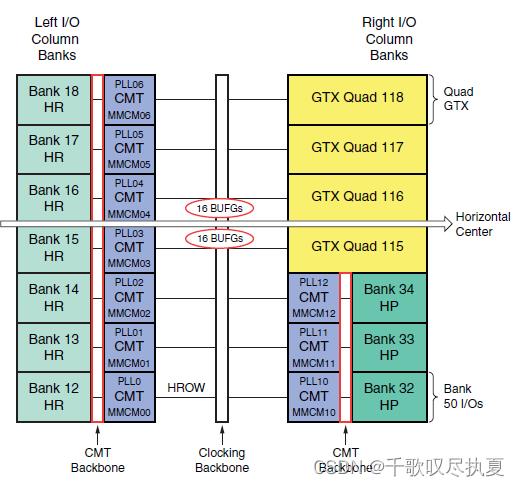

7 系列器件通过使用时钟区域改进了时钟分布。 每个时钟区域最多可以有 12 个全局时钟域。这 12 个全局时钟可以由任何单片器件或 SLR 中可用的 32 个全局时钟缓冲器的组合。 这时钟区域的尺寸固定为 50 个 CLB 高(50 个 IOB)并跨越左侧或器件的右侧。 在 7 系列器件中,时钟主干将器件分成左或右边。 主干不在器件的中心,通过固定尺寸时钟区域,更大的 7 系列器件可以有更多的时钟区域 (下图中的Clock Region) 。7 系列 FPGA供应从 1 到 24 个时钟区域。

垂直时钟中心线(Clocking Center 时钟主干线)将器件划分为相邻的左右区域,而水平中心线(Horizontal Center)将器件划分为顶部和底部侧面。时钟主干中的资源被镜像到水平相邻区域的两侧,从而将某些时钟资源扩展到水平相邻区域。顶部和底部(图中2个Bank的位置)分隔两组全局时钟缓冲器(BUFGs),并对它们的连接方式施加了一些限制。但是,BUFGs不属于时钟区域,可以到达器件上的任何时钟点。所有水平时钟资源包含在时钟区域水平时钟行(HROW)的中心,而垂直的、非区域的时钟资源包含在时钟主干或CMT主干中。

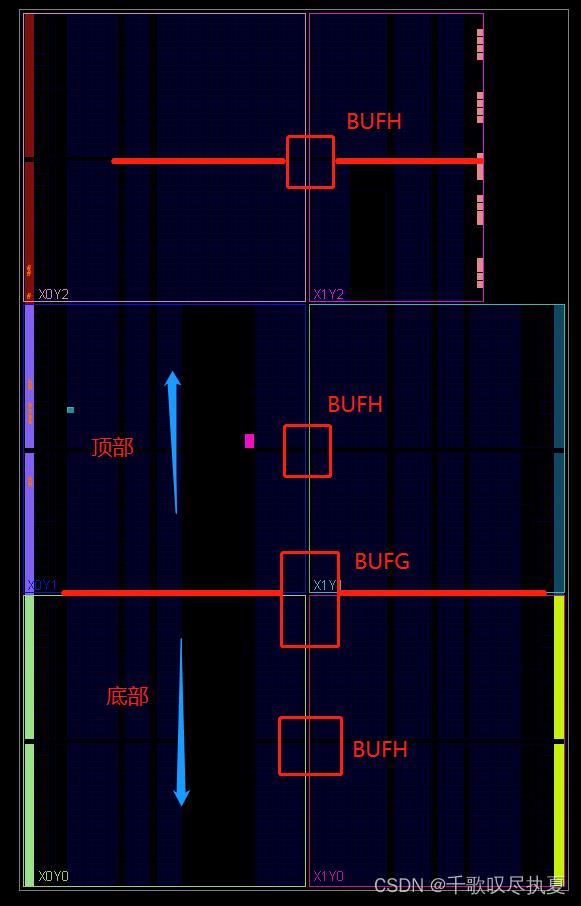

HROW即水平时钟线,也就是的BUFH或BUFG所走的线,由下图我们可以看到,很明显在每个Bank中间被BUFH分割开,这就是HROW,时钟沿着水平中心线向两侧延伸以为其他器件提供时钟。而左右Bank对称的中心线即为“Clock Backbone”,BUFG在一定长程度上水平分别在“Clock Backbone”中间,一般来讲上部分16个BUFG时钟源来自上半部分的所有Bank,下部分16个BUFG时钟源来自下半部分的所有Bank,而他们的输出可以到整个device的任意位置。

上面的原理图如果看不懂,我们可以结合一下软件上,芯片实际的图来看:

xc7a35tfgg484:

2.2、时钟区域-内部架构

2.2.1、区域整体

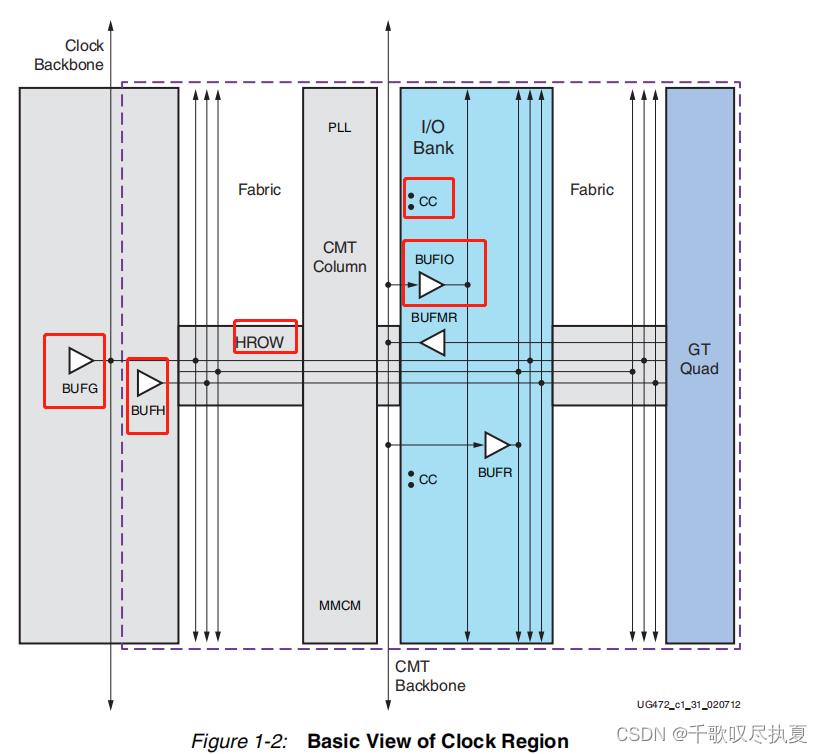

下图(Basic View of Clock Region 时钟区域基本视图 )是时钟区域中可用时钟资源及其基本连通性。

- 全局时钟缓冲器(BUFG)可以通过HROW进入每个区域,即使物理位置不在那里。

- 水平时钟缓冲器 (BUFH) 驱动通过 HROW 到达该地区的每个时钟点。

- BUFG 和 BUFH 共享HROW路径。

- I/O 缓冲器 (BUFIO) 和区域时钟缓冲器 (BUFR) 是位于 I/O Bank内。

- BUFIO 仅驱动 I/O 时钟资源,而BUFR 驱动 I/O 资源和逻辑资源。

- BUFMR 支持多区域链接BUFIO 和 BUFR。 具有时钟功能的输入 (CC) 将外部时钟连接到时钟设备上的资源。某些资源可以通过以下方式连接到上面和下面的区域CMT 骨干。

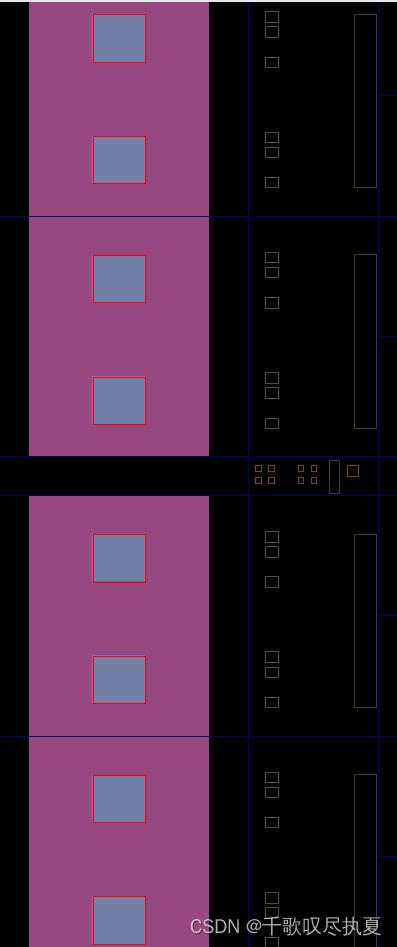

如下图是一个Bank的整体,BUFH可以驱动同一Bank的所有资源,我们可以看出“上”和“下”是对称分布的,BUFH位于Bank的一侧垂直居中,中间的分割线是有12条水平时钟线,与12个BUFH相连。BUFG也是通过连接到BUFH进而通过这12条水平时钟线驱动整个Bank的逻辑资源。每个Bank资源是按照一定的规律进行排列,也就是每列有50个CLB、50个引脚、10个BRAM,它们均匀的分布在水平时钟线两侧。不同型号芯片每个Bank的资源是不一样的,但每列资源确实固定的,只不过行数的多少。

2.2.2、区域细节

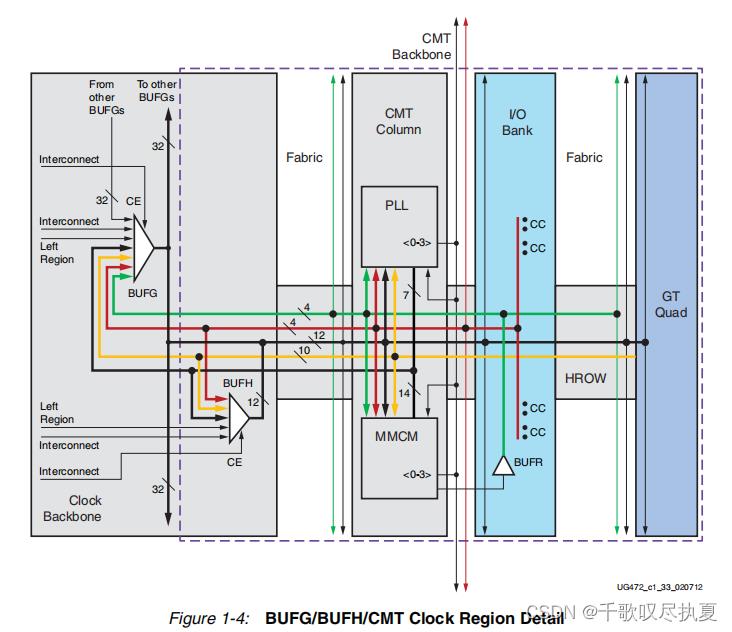

BUFG/BUFH/CMT时钟区域-具体走向图:

官方描述:

Any of the four clock-capable input pins can drive the PLL/MMCM in the CMT and the BUFH. The BUFG is shown as present in the region, but can be located physically somewhere else in the clock backbone. BUFG and BUFH share 12 routing tracks in the HROW and can drive all clocking points in the region. BUFGs can also drive BUFHs (not shown in Figure 1-4). This allows for individual clock enables (CE) on an otherwise global clock distribution.

A GT quad has ten dedicated tracks to drive the CMT and clock buffers in the clock backbone. The BUFRs located in the I/O bank have four tracks driving clocking points in the logic, CMT, and BUFG. CMTs can, with limitations, drive other CMTs in the adjacent regions using the CMT backbone. Similarly, clock-capable pins can drive, with the same limitations, CMTs in adjacent regions.

Clock-capable pins can drive BUFGs anywhere in the same top/bottom side of the device. There are four tracks in the CMT backbone to support connectivity between vertical regions.Clock sources from one region can drive clock buffer resources in its own region as well as in a horizontally adjacent region. CMTs, clock-capable pins, and serial transceivers can drive clocks into the horizontal adjacent region via the BUFH and also connect to the BUFGs in the same top/bottom side of the device.Logic interconnects drive the CE pins of BUFG and BUFH. Logic interconnects can also drive clocks into the same buffers, but care must be taken because the timing is not predictable.

简单解释:

- SRCC和MRCC时钟的输入引脚中的任何一个都可以驱动CMT和BUFH中的PLL/MMCM。

- BUFG显示位于该区域中,但可以实际位于时钟主干的其他位置。

- BUFG和BUFH在HROW中共享12条路由,可以驱动该区域内的所有时钟点。BUFGs也可以驱动BUFHs,允许在其他全局时钟分布上单独启用时钟(CE)。

- 一个GT Quad有十个专用的通道来驱动CMT和时钟缓冲器。

- 位于I/O bank中的BUFRs有四个走线驱动逻辑、CMT和BUFG中的时钟点。CMT可以使用CMT主干网驱动相邻区域中的其他CMT,但有局限性。类似地,时钟输入管脚可以在相同的限制下驱动相邻区域的CMT。

- 时钟输入管脚在器件的同一顶部/底部的任何地方可以驱动BUFG。CMT主干网中有四条走线支持垂直区域之间的连接。

IO Bank内部时钟结构:

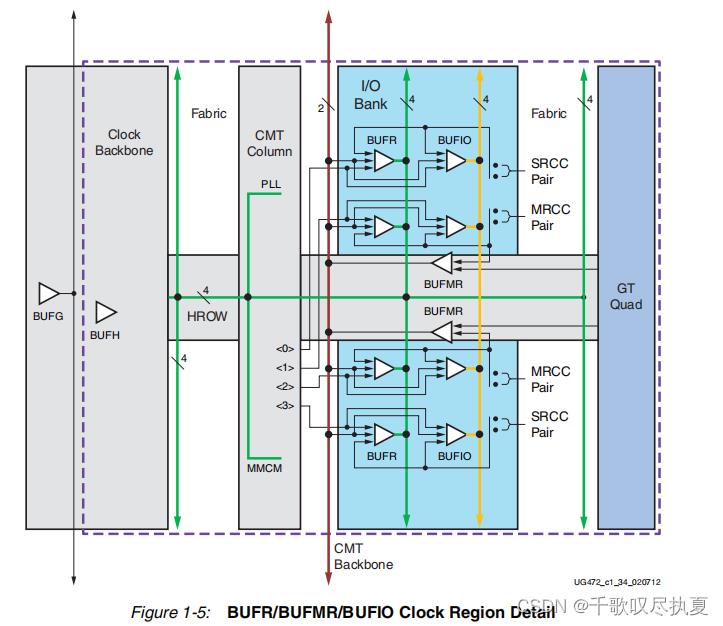

每个I/O bank包含4个BUFios和4个BUFRs。每一个时钟缓冲区都可以由特定的具有时钟功能的输入时钟引脚对驱动,也可以直接由MMCM的特定输出时钟驱动。两个具有时钟功能的输入引脚对,称为MRCC,支持多区域时钟方案。

MRCC引脚对可以驱动特定的BUFMR,而BUFMR又可以驱动相同和相邻区域的BUFIOs和BUFRs,从而促进多区域/Bank接口。同样,GT也可以驱动BUFMRs。MMCM<3:0>输出到BUFRs和BUFIOs有一个专用的高性能差分路径。这个特性也被称为高性能时钟(HPC)。尽管所有7系列设备都具有相同的基本架构,但在系列和系列中的设备之间存在一些架构差异。每个7系列FPGA在设备的左侧边缘至少有一个完整的I/O列。

GT (最右侧,深蓝色那列) 可以是7系列fpga支持的任何一个串行收发器(GTP、GTX或GTH)。带有GT的设备要么在设备的右边缘有一个GT和I/O的混合列(一些Kintex-7设备和一些Artix-7设备),要么在设备的右边缘有一个完整的GT列(一些Kintex-7设备和一些Virtex-7设备),在设备的右侧有一个完整的I/O列。其他Virtex-7设备在左右边缘有完整的GT列,在左右两侧有完整的I/O列。Artix-7 200T设备在顶部和底部的时钟旁边有GTP收发器列。

因此,并非7系列设备中的所有时钟区域都包含前面图中所示的所有块。有关7系列设备的块级架构视图,请参见UG475, 7系列FPGA封装和Pinout规范中的模级库编号概述部分。

7K325T架构图

三、时钟术语-解读(及使用方法)

7系列时钟架构,有很多术语,类似:BUFG、BUGH、BUFMR、BUFIO、CC等等,这些术语如果不加以描述,可能很多读者会一脸疑惑,这是个啥?

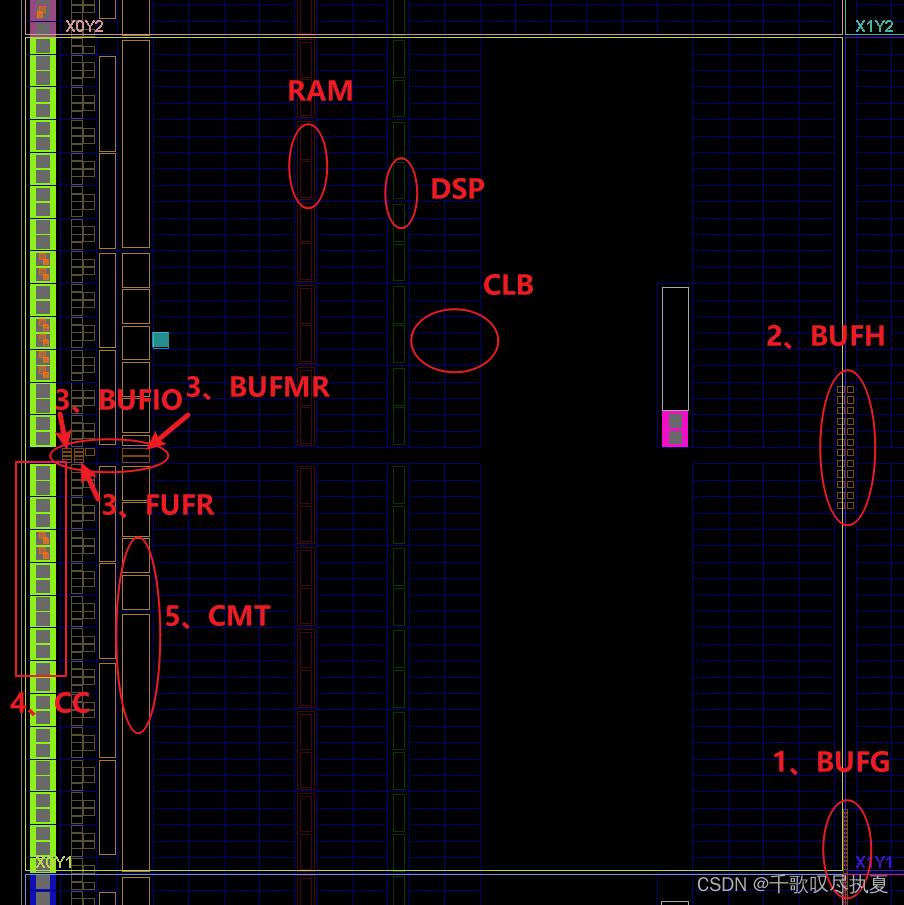

下面是一张完整的Bank图,各种时钟资源的位置,其中RAM,DSP,CLB不是时钟资源,看到了顺手标一下给大家看。

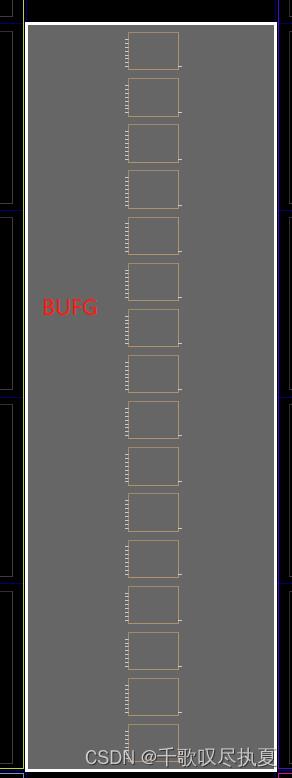

3.1、BUFG

BUFG 即全局缓冲,它的输入是IBUFG的输出,BUFG的输出到达FPGA内部的IOB、CLB、Block Select RAM的时钟延迟和抖动最小。输入为固定管脚,输出为H型全铜全局高速网络,这样抖动和到任意触发器的延时差最小,这个也就是FPGA做同步设计可以不需要做后仿真的原因。(每个芯片都有32个BUFG)

IBUFG 即输入全局缓冲,是与专用全局时钟输入管脚相连接的首级全局缓冲。所有从全局时钟管脚输入的信号必须经过IBUFG单元,否则在布局布线时会报错。IBUFG支持AGP,CTT,GTL,GTLP,HSTL,LVCMOS,LVDCI,LVPECL,LVTTL,PCI,PCIX,,SSTL等多种格式的IO标准。

-

IBUFG + BUFG的使用方法:

-

IBUFG后面连接BUFG的方法是最基本的全局时钟资源的使用方法,由于IBUFG组合BUFG相当于BUFGP,所以在这种使用方法也称为BUFGP方法。

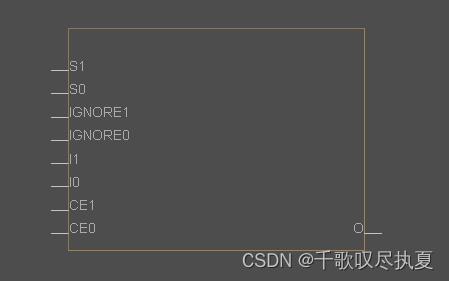

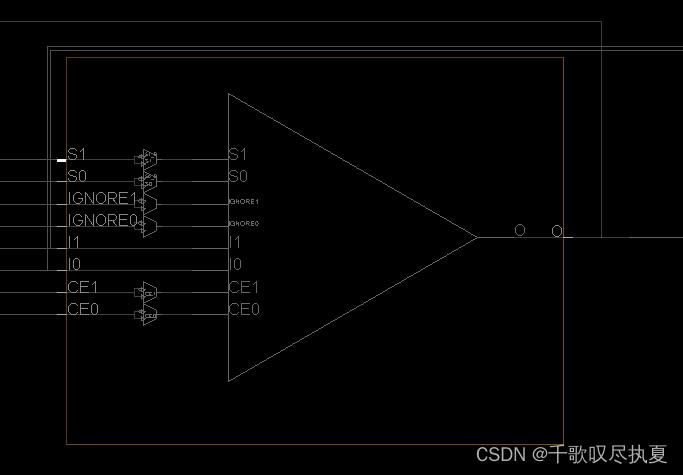

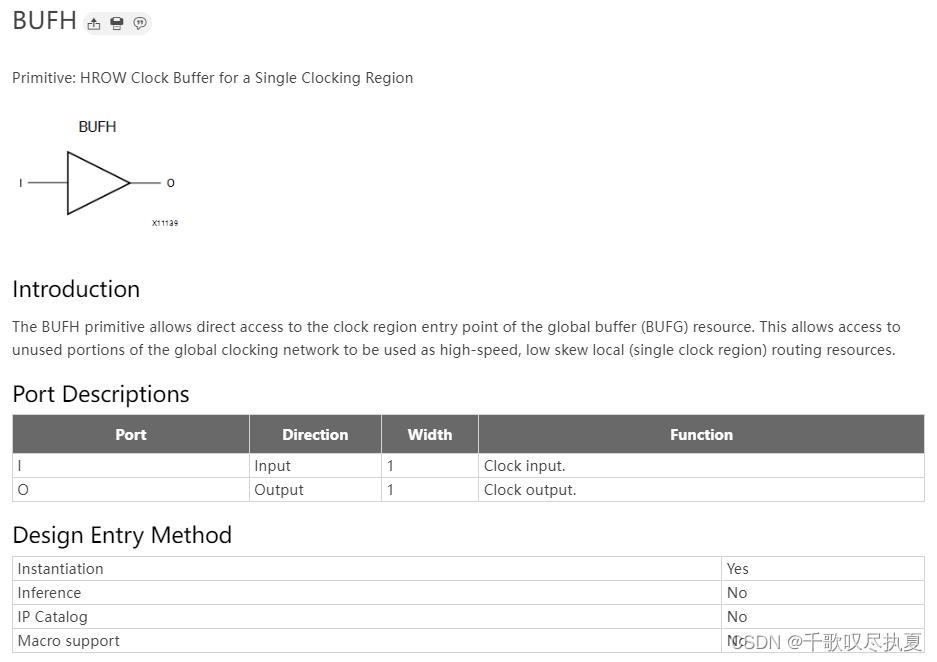

3.2、BUFH

BUFH即为水平时钟缓冲器,它相当于一个功能受限的BUFG,其输出时钟只能通过HROW在左右相邻的时钟区域内工作。

他在芯片中的位置,大家可以看前面的全局图。

原语描述:单个时钟区域的HROW时钟缓冲区

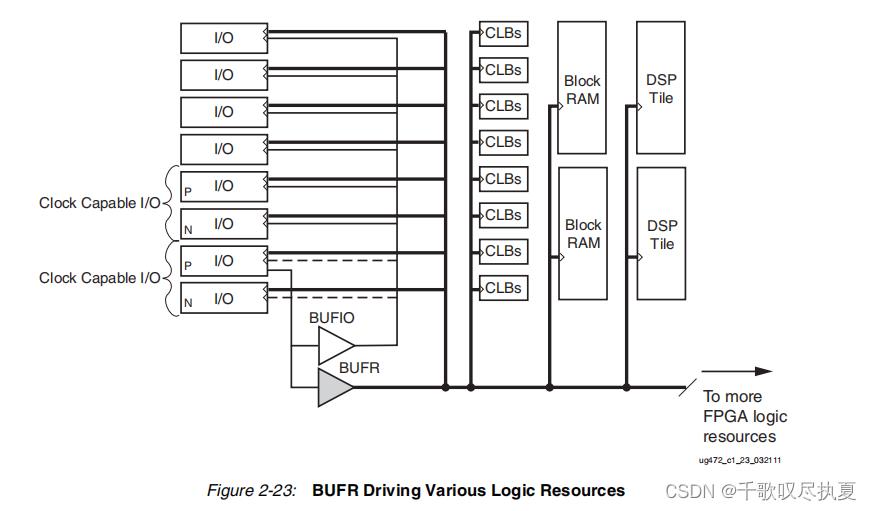

3.3、BUFIO/BUFR/BUFMR

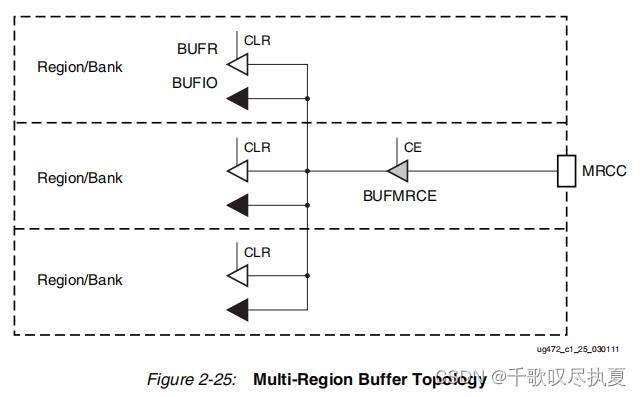

BUFIO即为IO时钟缓冲器,其输出时钟只能作用在一个时钟区域的IO寄存器处,无法在FPGA内部逻辑使用。BUFIO、BUFR都位于I/O BANK,所以它们是与引脚相关的区域时钟缓冲器,可有助于实现时钟源的同步采集,串并之间的转换等等。每个有引脚的BANK都有四个BUFIO和BUFR、两个BUFMRCE。

BUFIO也是区域时钟缓冲器,它的作用是用来驱动I/O BANK里面的ILOGIC和OLOGIC。BUFR区域时钟缓冲器,与BUFIO不同在于可以驱动BUFG可以驱动的同一时钟区域中的任何时钟点。

BUFR使用模型:BUFR非常适合需要时钟域交叉或串行到并行转换的源同步应用程序。与BUFIOs不同的是,BUFR能够对FPGA(而不是IOB)中的逻辑资源进行计时。BUFR设计示例如图所示。(这张图在UG472-54页)

BUFMR是多区域时钟缓冲器,之所以只有两个是对应MRCC,MRCC就两个,所以BUFMR多了也没多啥用。它的作用就是扩展时钟区域,可以将某BANK的时钟引入到上下相邻的BANK中去,如下图所示,这里将MRCC直连到了BUFMR,但在实际应用情况下,MRCC需要先进过IOBUF,才可以连接到BUFMR。

下图是细节图,如果要看芯片中的位置,可以看上文的全局图。

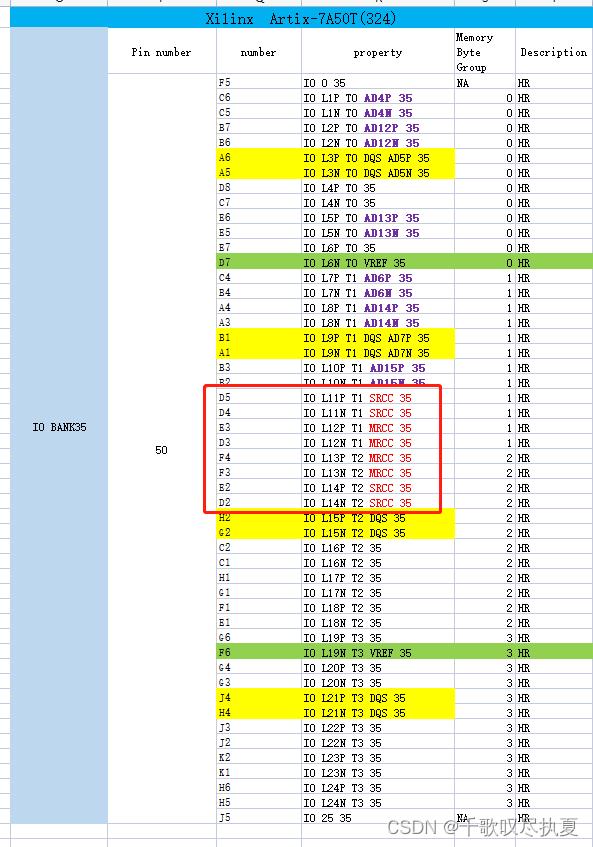

3.4、CC

CC即为外部时钟输入管脚,它是 “Clock-Capable” 即时钟功能的缩写,表示具有时钟功能的引脚,换句话说,并不是所有的引脚都可以接时钟的,有只有通过特定的引脚才能将外部时钟信号引入FPGA内部的时钟资源,这个引脚有两种,分别称之为MRCC(Multi-region clock-capable I/O)和SRCC(Single-region clock-capable I/O)。Multi-region译为多区域,Single-region译为单区域,而者的直观区别在于MRCC可以连接到BUFMR上,但SR不可以,BUFMR具有扩展功能,可以将本BANK时钟引入到其它BANK上,所以称可以连接到BUFMR的CC为MRCC。

CC在内部可以连接到BUFG、BUFR、BUFIO、BUFH、MMCM、PLL等,看具体的应用具体连接。下图所示为更为细致的CC管脚连接图。

每个BANK有50个引脚,其中有4对CC管脚,其中2对SRCC,2对MRCC。SRCC作为区域时钟使用时,只能连接本时钟区域的BUFR和BUFIO。而MRCC则还可以通过BUFMR作用在上下相邻的时钟区域。它们都是差分的,如果接单端时钟则需接到“P”上,对应的“N”引脚不可用。

关于CC及BUFIO的关系,如果还不是很明白,可以看一下上面,章节3.3的 Figure 2-23: BUFR Driving Various Logic Resources。

下图为Artix-7一个完整的Bank(因为7A50T在很多开发板上都用的,所以这里以此举例)

cc-pad:

3.5、CMT

- CMT Backbone:对于相邻时钟区域的时钟布线,可以不使用珍贵的全局时钟网络,而使用每个时钟区域都包含的CMT Backbone通道。

- CMT Column:每个时钟区域都包含一个CMT,一个CMT由一个MMCM和一个PLL组成。

每个7系列FPGA最多有24个CMTs,每个CMT由一个MMCM和一个PLL组成。MMCMs和PLL用作频率合成器,用于非常宽的频率范围,用作外部或内部时钟的抖动滤波器,以及低偏移时钟。PLL包含MMCM功能的一个子集。7系列FPGA时钟输入连接允许多个资源向MMCM和PLL提供参考时钟。

7系列FPGA MMCMs具有任意方向的无限精细相移能力,可用于动态相移模式。MMCMs在反馈路径或一个输出路径中也有一个小数计数器,使得频率合成能力能够进一步细化。

LogiCORE™ IP时钟向导可用于帮助利用MMCMs和PLL在7系列FPGA设计中创建时钟网络。图形用户界面用于采集时钟网络参数。计时向导选择适当的CMT资源,并以最佳方式配置CMT资源和关联的时钟路由资源。

MMCM、PLL的功能可以总结为3点:

- 频率综合。

- 去抖动。

- 去偏斜。

3.6、时钟资源的驱动关系

四、其他概念-补充说明

-

FPGA的全局时钟是什么?

FPGA的全局时钟应该是从晶振分出来的,最原始的频率。其他需要的各种频率都是在这个基础上利用PLL或者其他分频手段得到的。

对于一个设计项目来说,全局时钟(或同步时钟)是最简单和最可预测的时钟。在PLD/FPGA设计中最好的时钟方案是:由专用的全局时钟输入引脚驱动的单个主时钟去钟控设计项目中的每一个触发器。只要可能就应尽量在设计项目中采用全局时钟。PLD/FPGA都具有专门的全局时钟引脚,它直接连到器件中的每一个寄存器。这种全局时钟提供器件中最短的时钟到输出的延时。 -

CCLK是什么?

FPGA同步配置时钟。如果配置模式为主模式,则该时钟由FPGA器件生成,并输出;如果配置模式为从模式,则该时钟由外部提供;当所配置的数据存放在PROM中,即通过PROM来配置器件时,必须选择CCLK时钟;

USER CLOCK:用户定义的配置时钟信号,该配置时钟目前很少采用;

JTAG CLOCK:JTAG模式的配置时钟,该时钟提供给内部的JTAG控制逻辑。

默认值为:CCLK -

CCLK是怎么产生的:

CCLK的产生根据配置模式不同而不同,如果设置为Master模式,则由内部的震荡电路产生,作为外部ROM的工作时钟,默认为6MHZ,可通过配置选项设置;如果设置为Slave模式,则由计算机(或其他下载设备)提供,作为芯片内部下载电路的工作时钟;在JTAG模式情况下,CCLK不输出,此时芯片内部下载电路时钟由内部震荡电路提供,TCK仅用作边界扫描相关电路时钟。

补充记张图,增加大家对7系列时钟架构的理解:

五、参考文献

官方文档:

7 Series FPGAs Clocking Resources User Guide (UG472)

CSDN博客:

1、https://blog.csdn.net/z123canghai/article/details/121308631

2、https://blog.csdn.net/gslscyx/article/details/114602573

3、http://blog.chinaunix.net/uid-7547035-id-60220.html

知乎文章:

1、https://zhuanlan.zhihu.com/p/117290284

六、总结

囫囵吞枣,洋洋洒洒写了半个月,借鉴了多位前辈的文章,以及官方文档,在这里表示感谢。如果有侵权的地方,可以私信我,马上删除。读者有不懂的地方,也可以跟我一起探讨讨论,邮箱:bumianzhe@126.com.

[从零开始学习FPGA编程-53]:高阶篇 - 基于IP核的FPGA开发-PLL锁相环IP核的原理与配置(Xilinx)

作者主页(文火冰糖的硅基工坊):文火冰糖(王文兵)的博客_文火冰糖的硅基工坊_CSDN博客

本文网址:

目录

以上是关于零基础学FPGA:FPGA时钟架构(Xilinx为例,完整解读)的主要内容,如果未能解决你的问题,请参考以下文章

xilinx fpga中块ram的使用——简单双端口ram的使用

[从零开始学习FPGA编程-53]:高阶篇 - 基于IP核的FPGA开发-PLL锁相环IP核的原理与配置(Xilinx)