数字电路题 :请判断下列各门电路的输出状态

Posted

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了数字电路题 :请判断下列各门电路的输出状态相关的知识,希望对你有一定的参考价值。

74系列TTL电路,左上第一图,因输入低电平经过10K电阻,3脚输入因电流输出原因为高电平,或非门输出Y1为低电平 右上第二图,同理3脚输入高电平,或非门输出Y2低电平左中第三图3脚与非门输出有低出高为高电平,5脚输出全高出低为低电平,经过或非门有高出低输出Y3为低电平

74HC系列COMS路 右中第四图6脚接CMOS输入以10K电阻接地,据CMOS电路特性,输入电流零。可认为接地,或非门输出Y4为高电平

最后一电路6脚低电平,Y5输出高电平 参考技术A 按照从上到下 从左到右的原则 解答一些 答案仅供参考74系列的与非门y1输出高电平,y2输出高电平,y3输出高电平,y4输出高电平,y5输出高电平,高电平(2。4伏 以上)和低电平(0。8伏以下)。

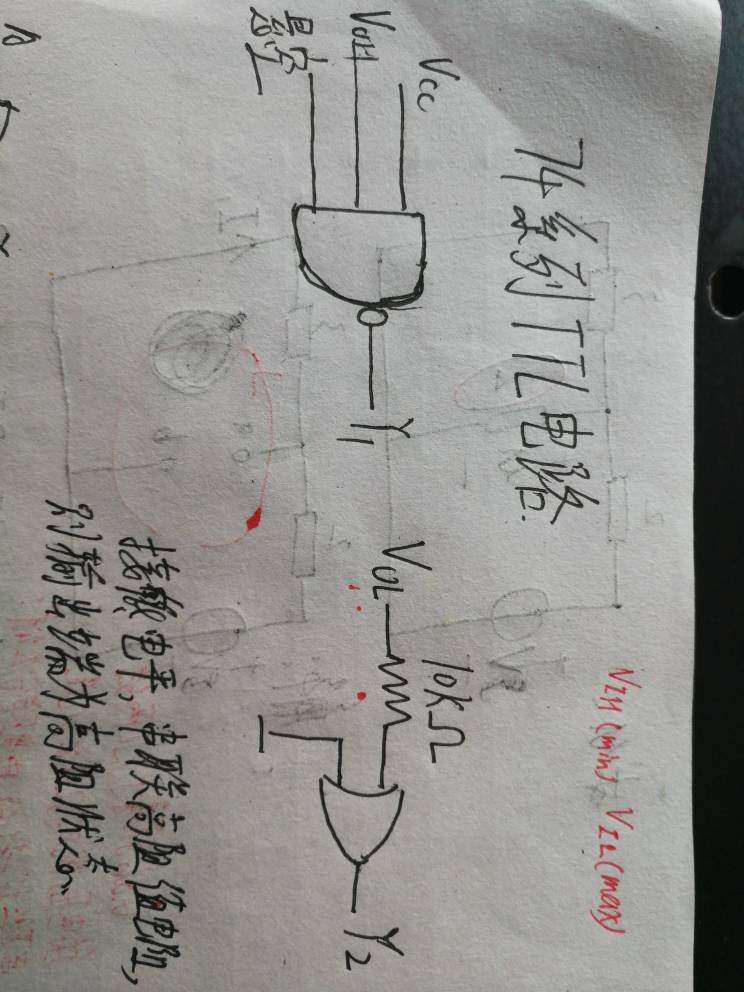

如图,请教这两种门电路输出状态怎么判断,谢谢

74系列TTL电路

Y2由于其两个输入均为低电平,所以输出Y2=AB=00=0 参考技术A 左图为三输入与非门,由于是TTL电路故输入端悬空即为逻辑1,其余两输入端亦为逻辑1,按照与非门的逻辑规则Y1输出应为逻辑0,右图为两输入或门,图中一输入端串入10K电阻,由于阻值较大可能其上压降将导致或门输入抬升为逻辑1,按或门逻辑规则故输出Y2亦为逻辑1。本回答被提问者采纳 参考技术B 74系列TTL电路

以上是关于数字电路题 :请判断下列各门电路的输出状态的主要内容,如果未能解决你的问题,请参考以下文章