数字电路逻辑设计笔记:chap5集成触发器

Posted 临风而眠

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了数字电路逻辑设计笔记:chap5集成触发器相关的知识,希望对你有一定的参考价值。

数字电路逻辑设计笔记(5):chap5 集成触发器

本章关注的是触发器的功能

如同门是组合逻辑电路的基本单元一样,触发器是时序逻辑电路的基本单元

组合逻辑电路的输出仅仅取决于当时的输入

时序逻辑电路的输出不仅仅取决于当时的输入,还与过去的状态有关系,时序电路有记忆功能

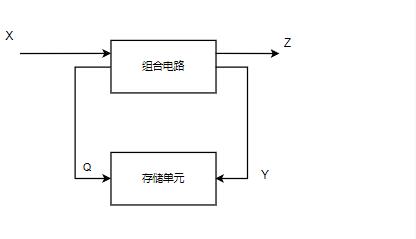

时序逻辑电路相当于组合电路加存储单元

X:外部输入 Q:内部输入

Z: 外部输出 Y : 内部输出

文章目录

时序逻辑电路简述

-

时序逻辑的基础:触发器

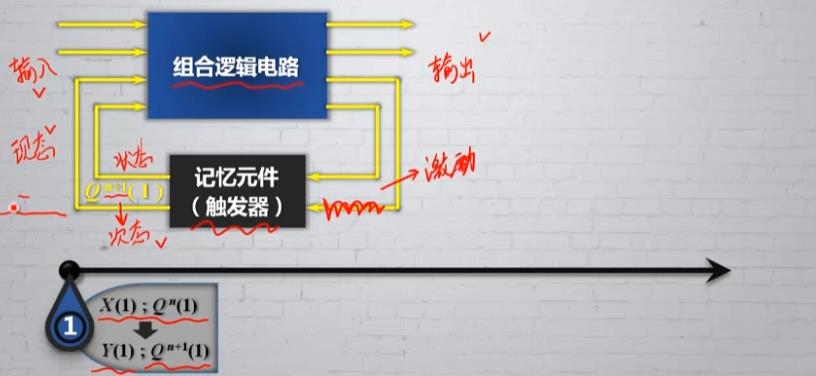

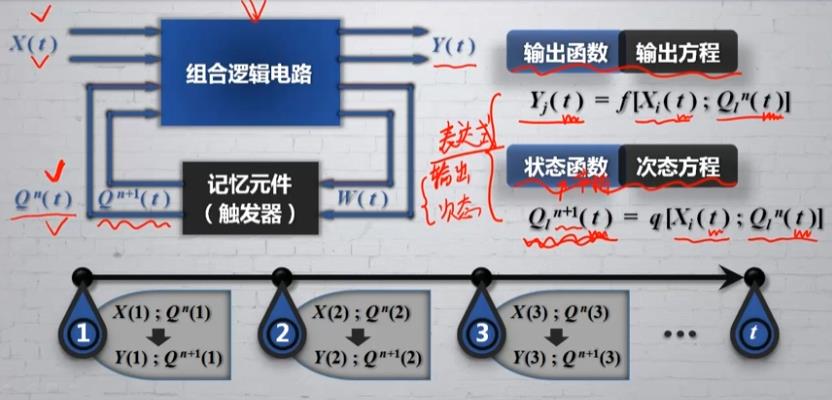

时序逻辑电路的结构和工作特点

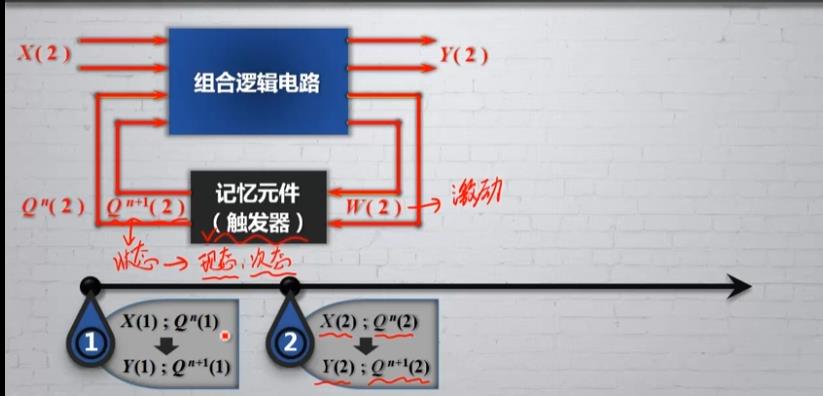

1时刻的输入和1时刻的状态(现态)决定了1时刻的输出和2时刻的状态,在1时刻来看,2时刻的状态称为次态

2时刻的输入和2时刻的状态(现态)决定了2时刻的输出和3时刻的状态(次态)

时序逻辑电路的分类

-

根据电路的工作方式(电路中触发器的工作时刻是否统一),可分为

- 同步时序逻辑电路

- 异步时序逻辑电路

-

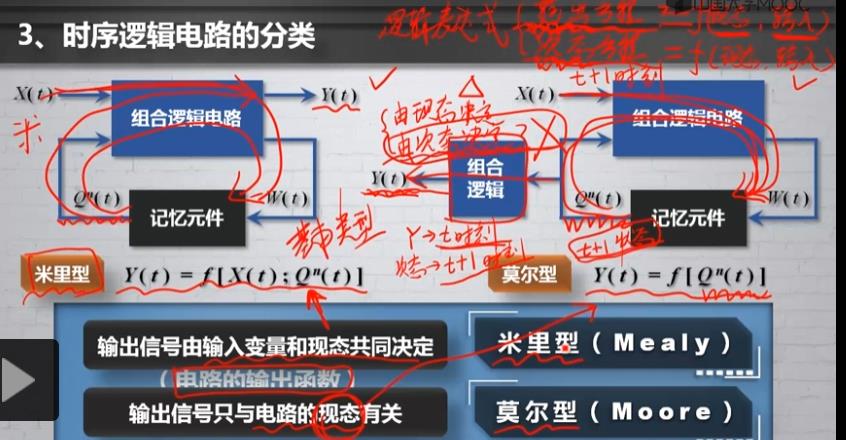

根据电路输出信号的决定关系(电路的输出函数),可分为

- 米里型(Mealy)

- 莫尔型(Moore)

-

逻辑功能划分

- 计数器

- 寄存器

- 特定信号发生器

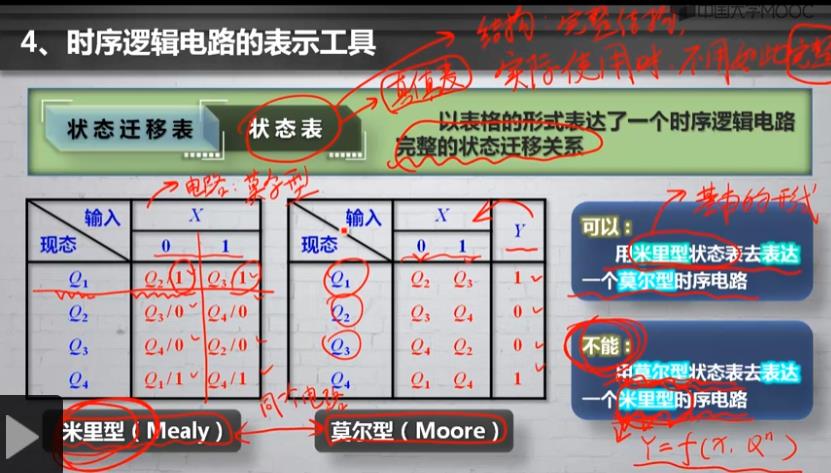

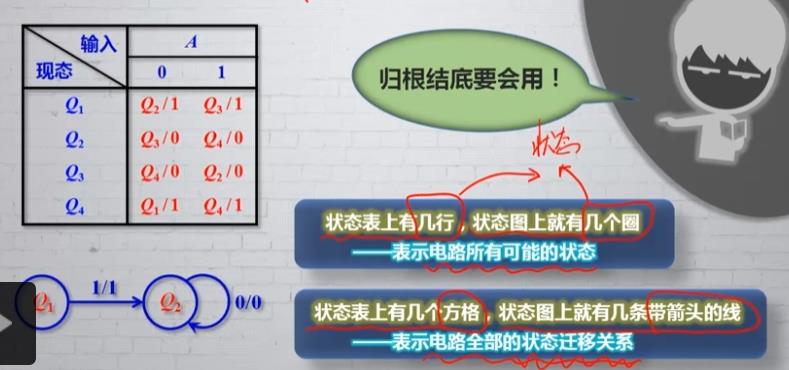

时序逻辑电路的表示工具–状态表和状态图

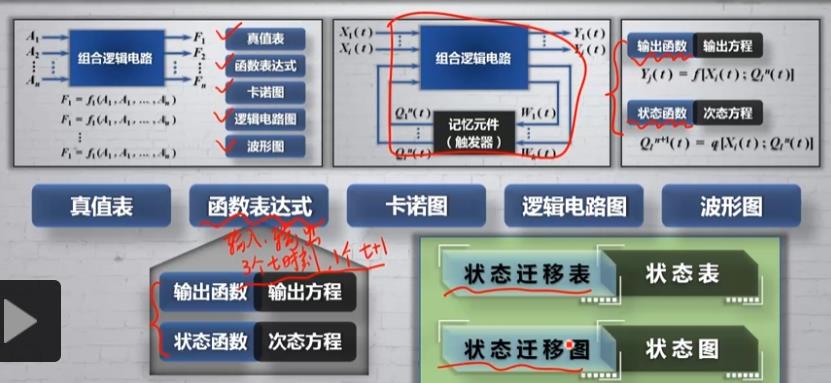

组合逻辑电路中有五大工具:

组合逻辑中也有那5个工具+2个新工具

其中函数表达式更加复杂

-

状态表

-

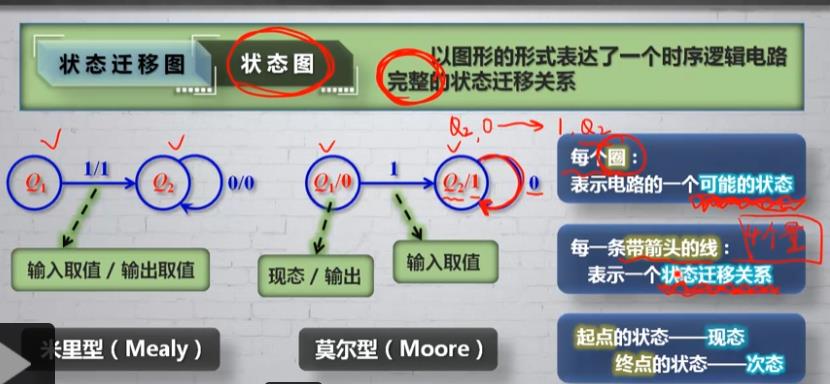

状态图

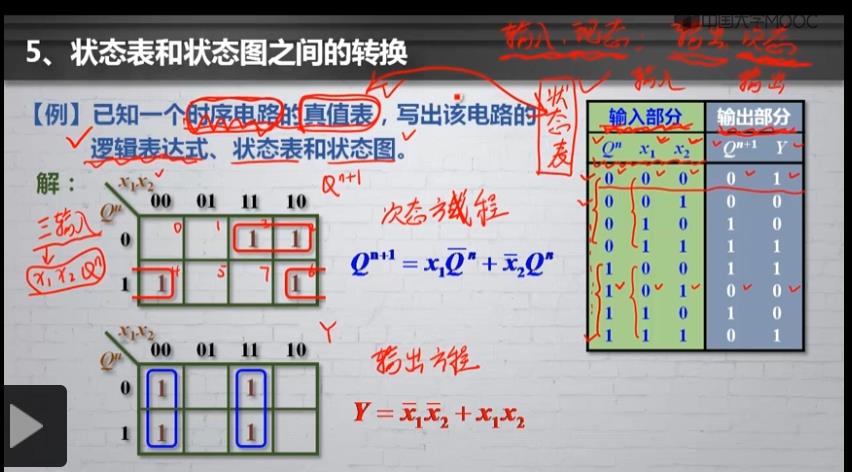

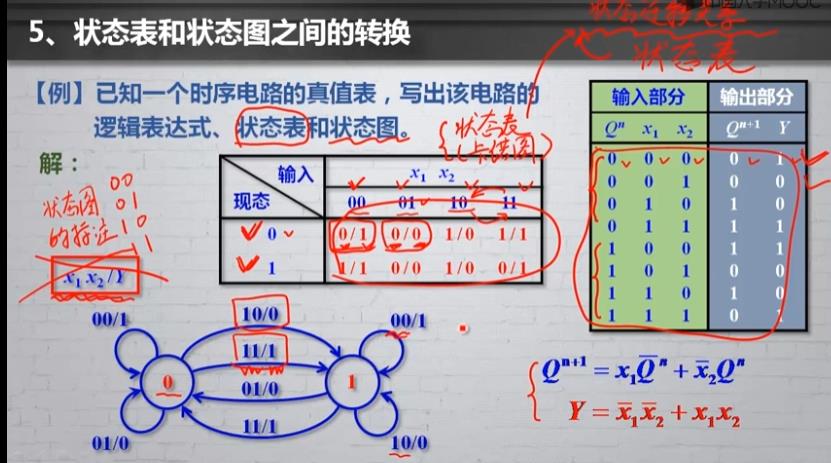

状态表和状态图的转换

几种工具之间的转换

-

例

状态图标注可防止阅读时的混淆

触发器概述

触发器是构成时序逻辑电路的基本单元。是具有记忆功能,能存储1位二进制信息的逻辑电路。

触发器的输入与输出

-

触发器的特点

-

状态说明

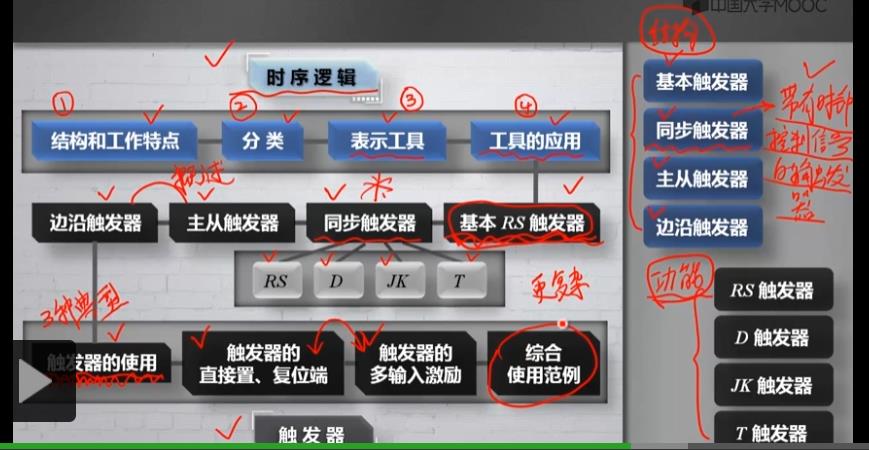

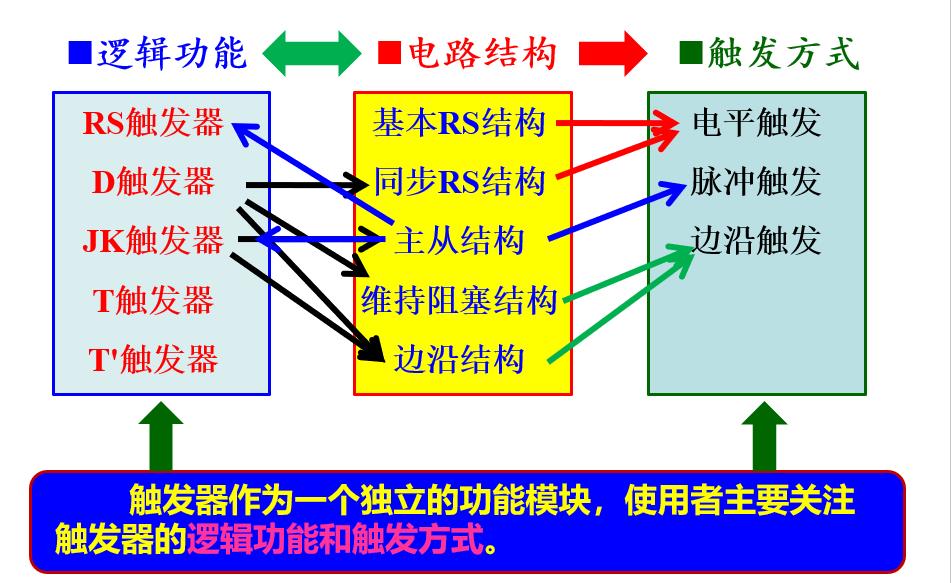

触发器的分类

触发器知识结构

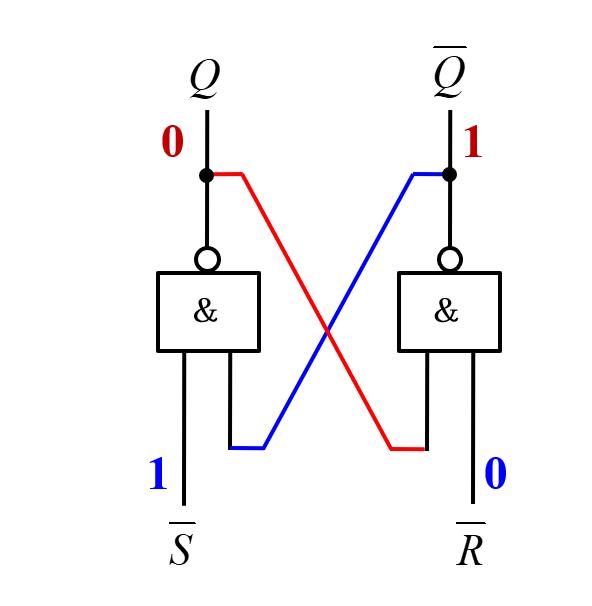

§5.1 基本RS触发器(RSFF )

FF:flip-flop

一.电路结构和工作原理

注意:

与门、与非门中起决定性作用的是0

活门、或非门中起决定性作用的是1

-

电路结构:

-

功能表

-

约束条件

R ‾ \\overline{R} R和 S ‾ \\overline{S} S至少有一个为1

-

几种状态

-

无效态

-

“1”态

-

“0”态

-

-

符号

圆圈和非号就是强调低电平有效

圆圈和非号同时出现不是抵消,就是强调低电平有效

出现任意一个都是强调低电平有效

都不出现才表示高电平有效

二.基本RS触发器的功能描述

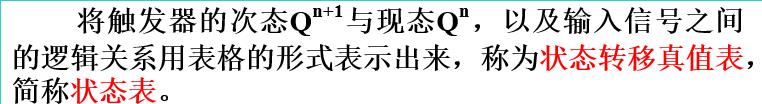

1.状态转移真值表

-

基本RS触发器的状态表

电路的次态可以理解为初态和输入信号的函数

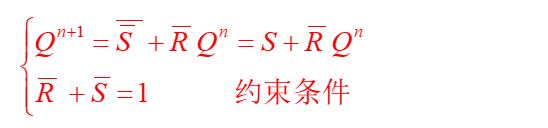

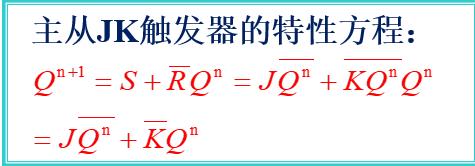

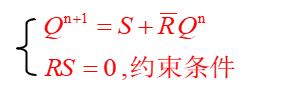

2.特性方程

描述触发器或逻辑功能的函数表达式称为特性方程,又称状态方程或次态方程。

R:reset 清零

S: set 置一

R有效输出为0 R是清零端

S有效输出为1 S是置一端

-

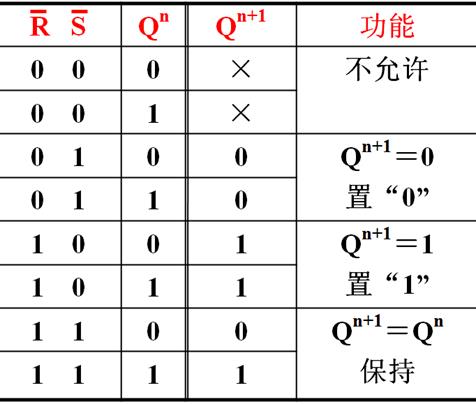

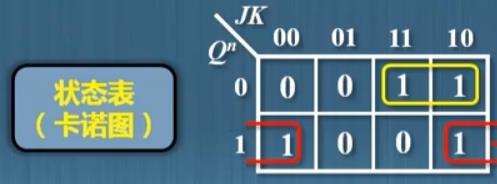

次态 Q n + 1 Q^{n+1} Qn+1的卡诺图

-

基本RS触发器的特性方程

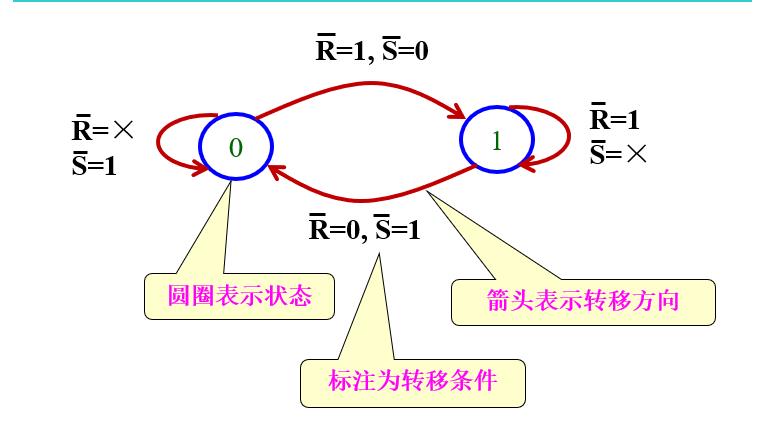

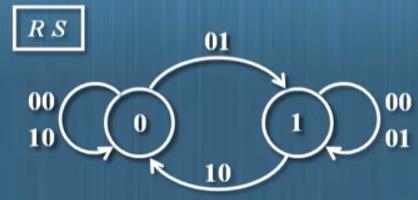

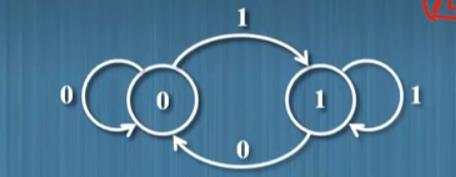

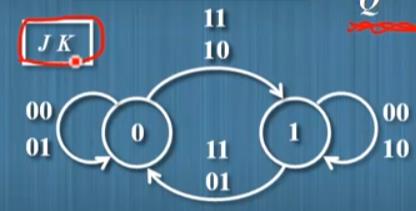

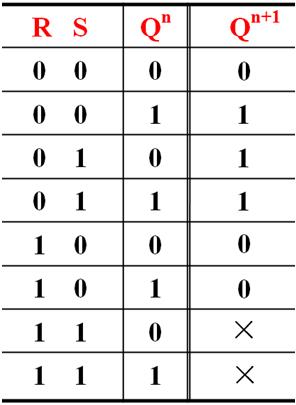

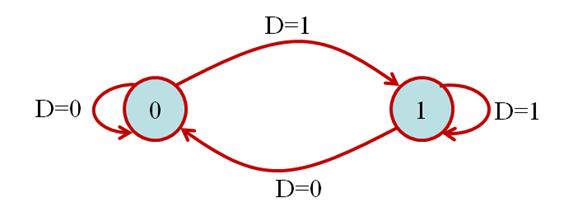

3.状态转换图

-

描述触发器的状态转换关系及转换条件的图形称为状态转换图,简称状态图

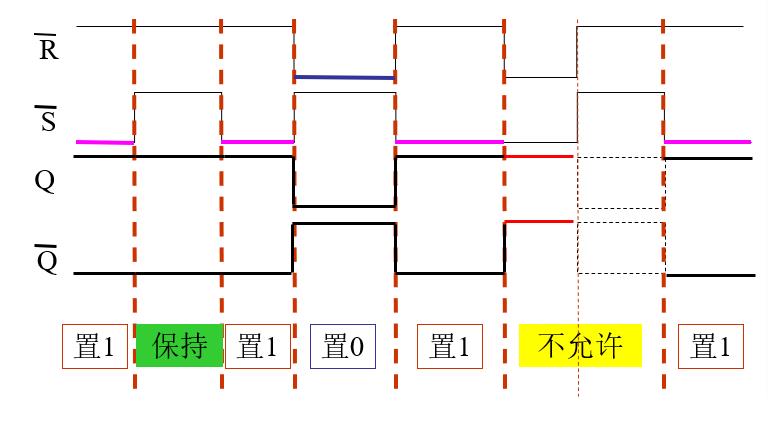

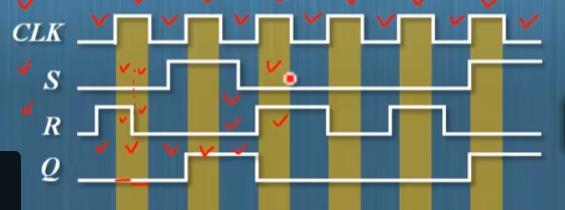

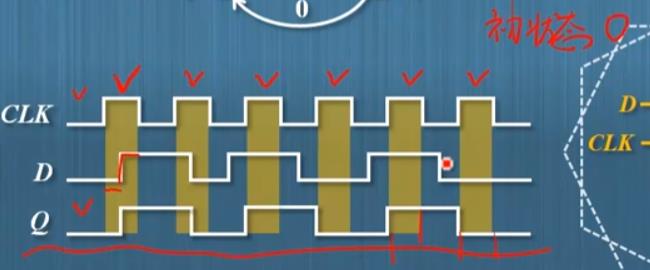

4.波形图

工作波形图又称为时序图,是描述触发器输出状态随时间和输入信号变化规律的图形

从 0 0 变成 1 1的状态,不确定,要看门的延迟时间

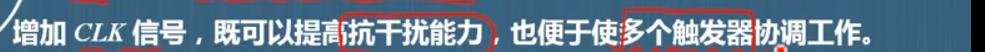

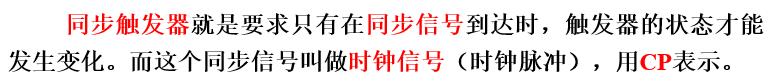

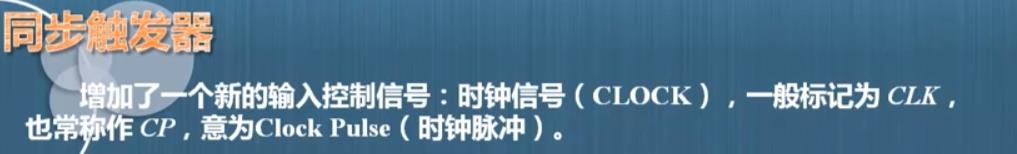

§5.2 同步(钟控)触发器

★ 锁存器

CP: clock plus

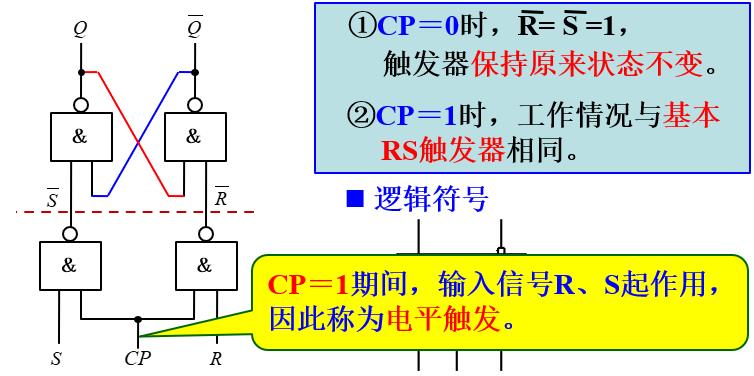

一.同步(钟控)RS触发器–RS锁存器(Latch)

置0置1触发器

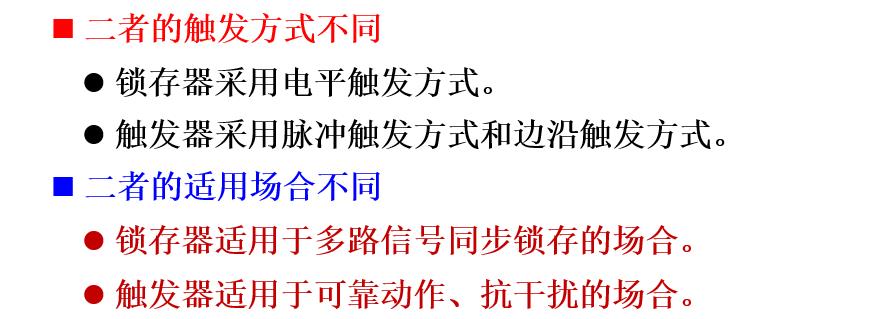

触发器和锁存器稍微有一点区别

触发器靠脉冲

锁存器靠电平

- 电路结构和工作原理

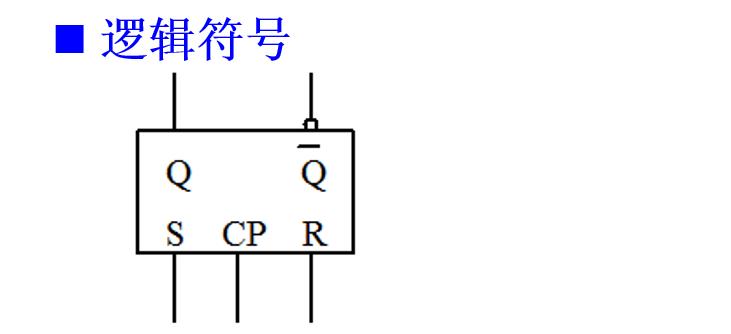

- 逻辑符号

-

功能表

-

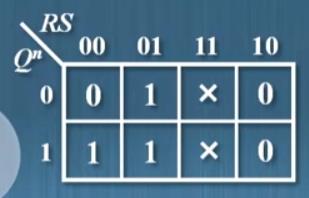

状态表/卡诺图

-

特征方程

-

状态图

-

波形图

设一个初状态,一般设为0

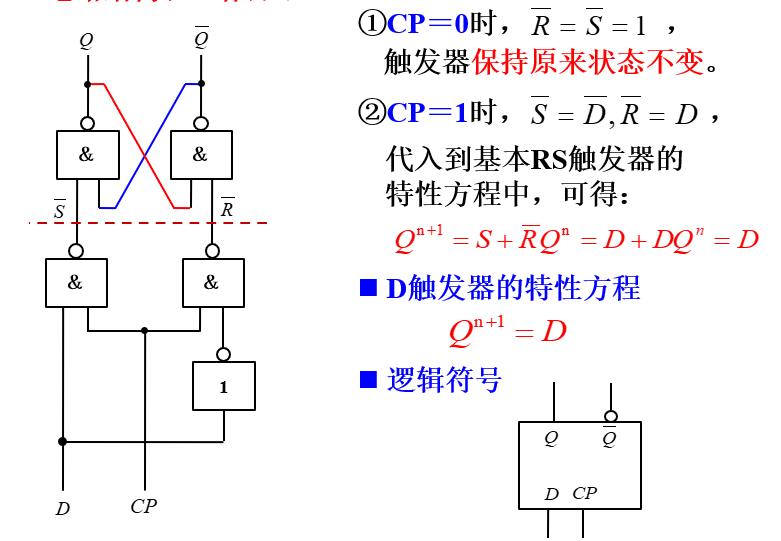

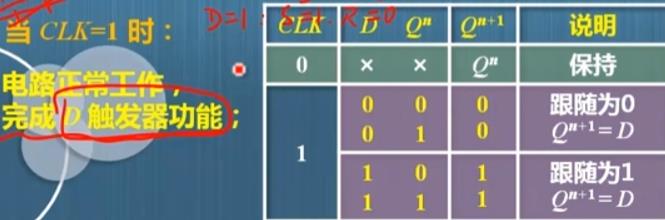

二.同步(钟控) D触发器–D锁存器

跟随触发器

- 电路结构和工作原理

-

功能表

次态跟随激励D变化

-

状态图

输入激励是什么,就跟随成为什么

-

波形图

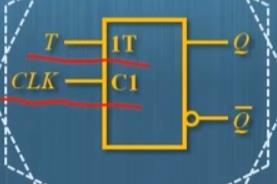

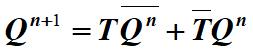

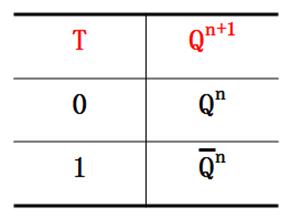

三.同步T触发器

-

逻辑电路图

-

工作原理

-

功能表

-

逻辑符号

此处T触发器的T激励是高有效

-

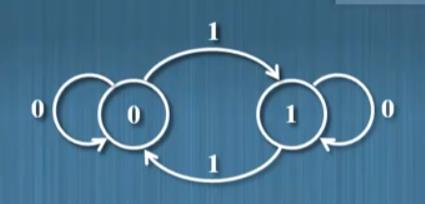

状态图

-

特征方程

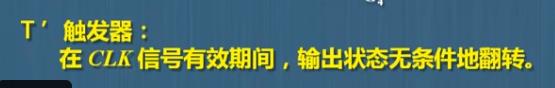

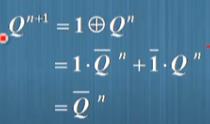

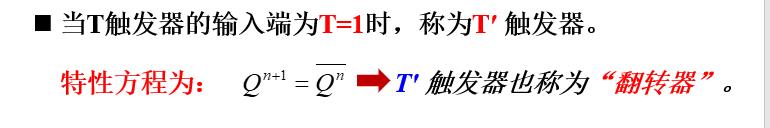

T’触发器

(必翻触发器)

是T触发器的简单应用变形

- 令T始终为1

-

-

逻辑电路图

-

特征方程

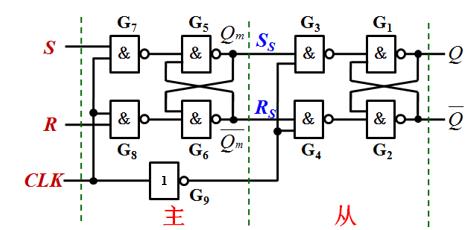

§5.3 主从触发器

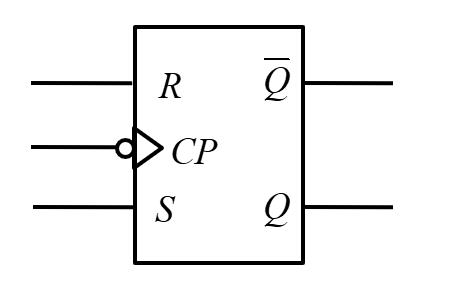

一.主从RS触发器

1.电路结构和工作原理

-

逻辑电路图

-

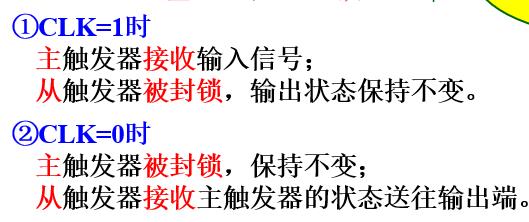

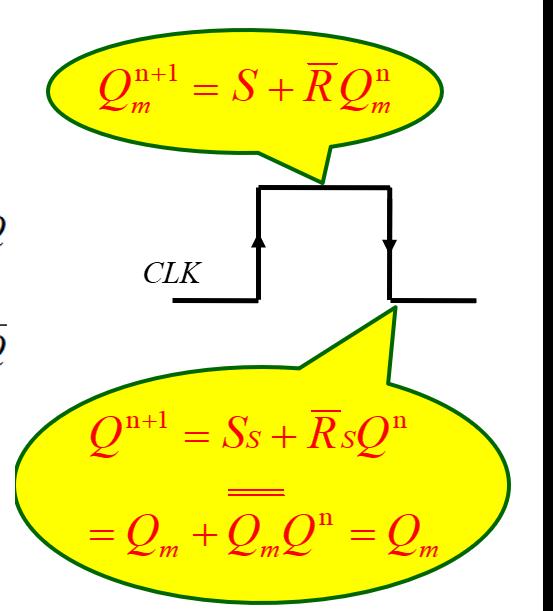

工作原理

-

逻辑符号

-

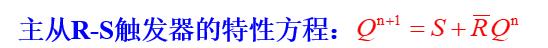

特征方程

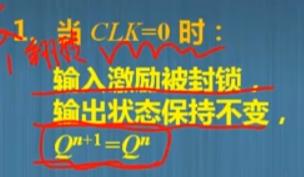

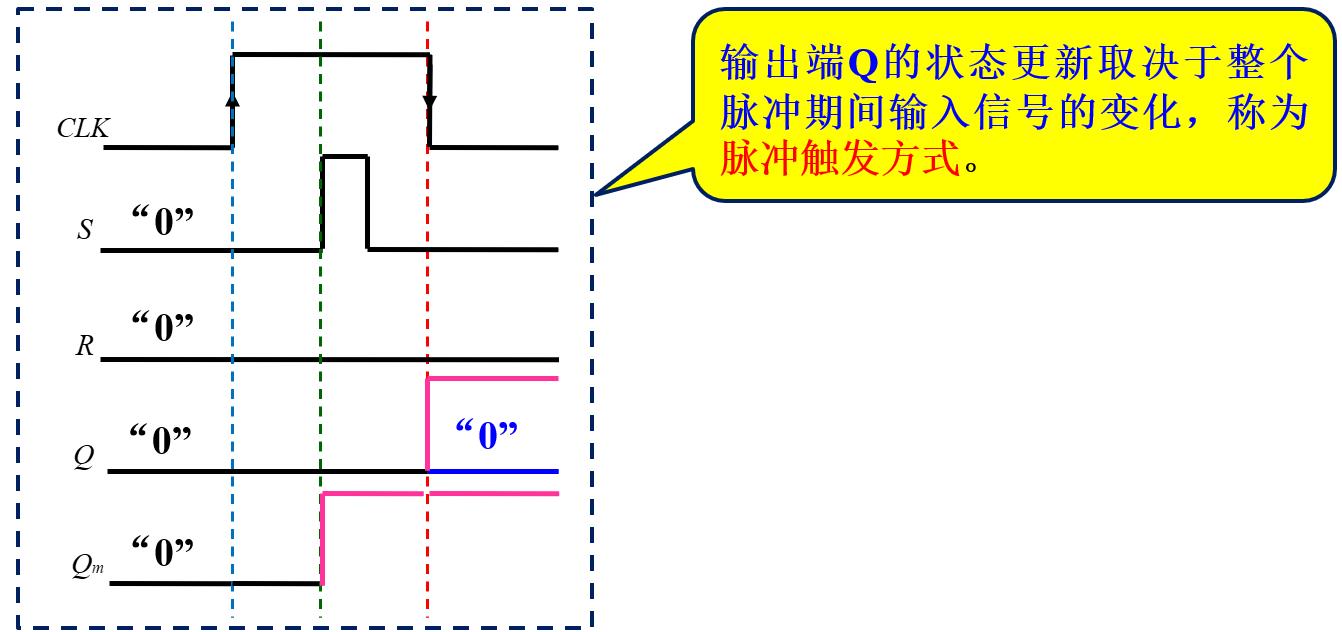

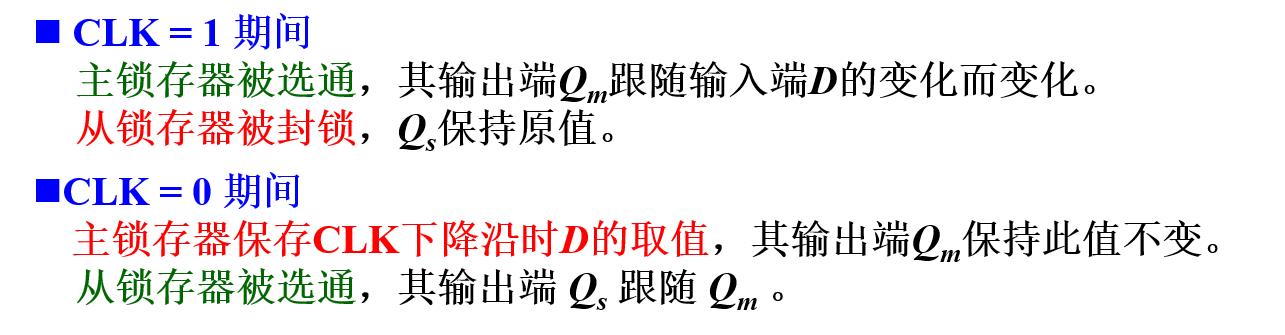

2.主从RS触发器的动作特点

CLK=1期间,主触发器的状态 Q m Q_m Qm随输入信号 R , S R,S R,S的变化而变化;而输出端Q的状态更新发生在下降沿到来的时刻,但输出的状态不一定按此刻输入信号的状态来确定

-

脉冲触发方式

-

主从RS触发器的特点

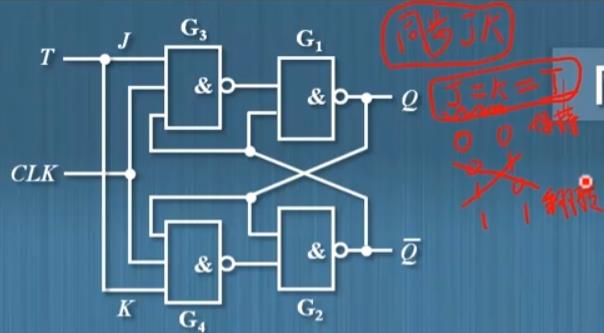

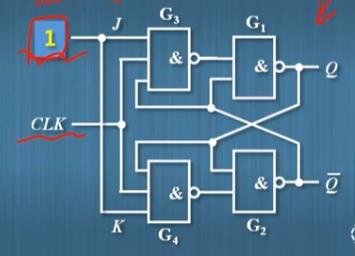

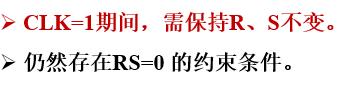

二.主从JK触发器

电路结构和工作原理

-

逻辑电路图

由于两根返回线的存在,保证了等效的R与等效的S不可能出现同时为1的状态(因为两根返回线肯定有一个是0)

这个讲的超好:B站新手小牛

-

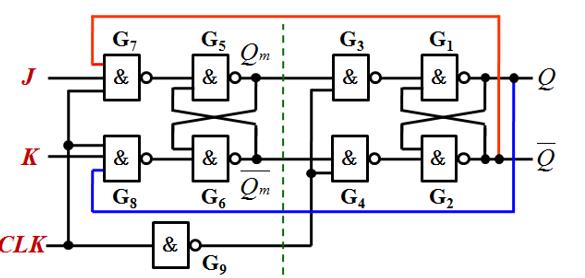

逻辑符号

-

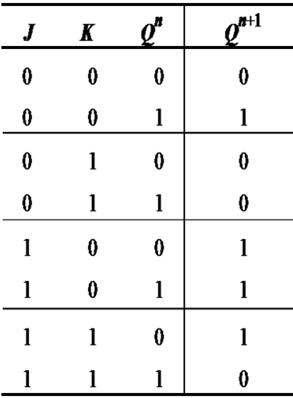

状态表(卡诺图)

-

特征方程

-

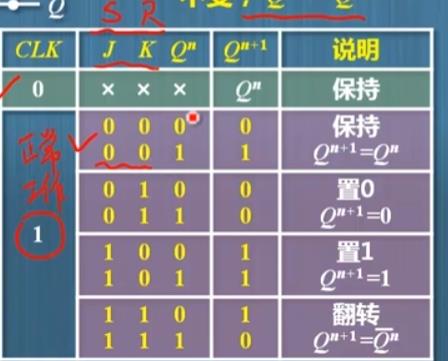

JK触发器功能表

- J端 置1端(置位端)

- K端 置0端(复位端)

-

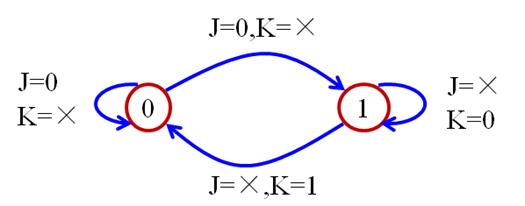

状态图(8个箭头!)

-

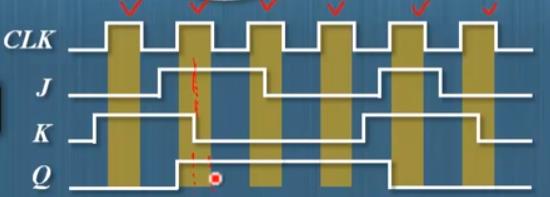

波形图

设初状态为0

-

JK触发器,00不变,11翻转;01,10 同 J

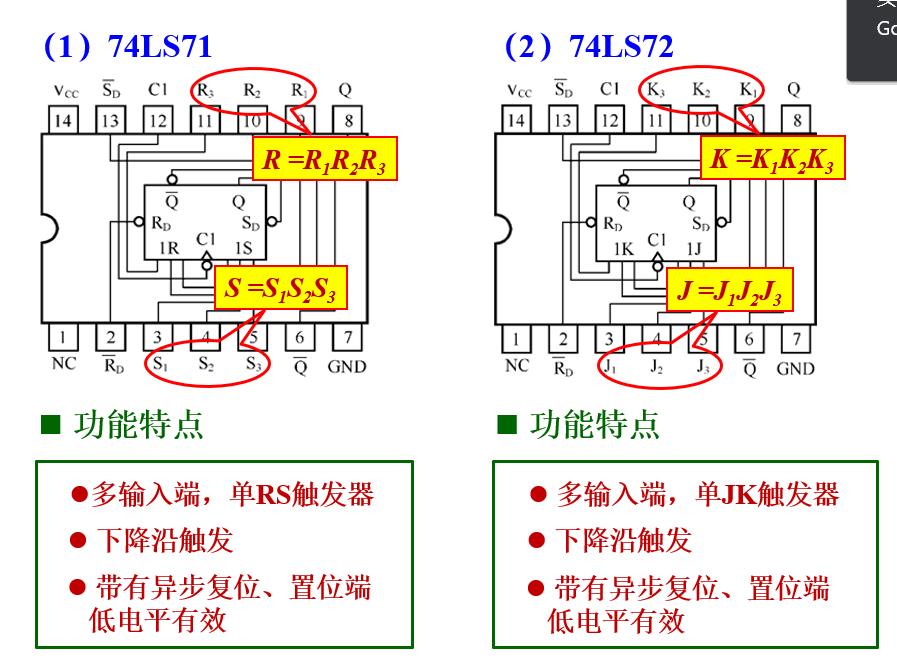

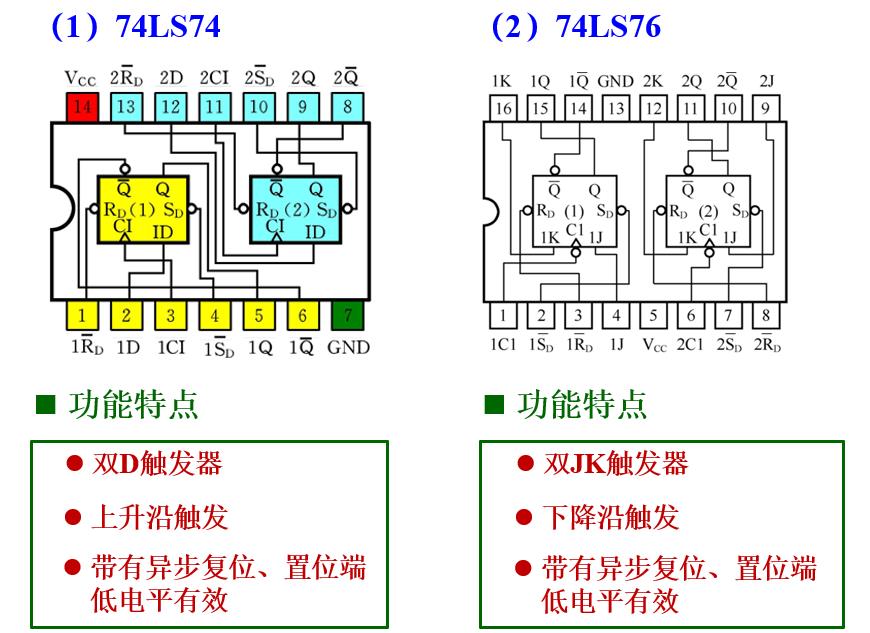

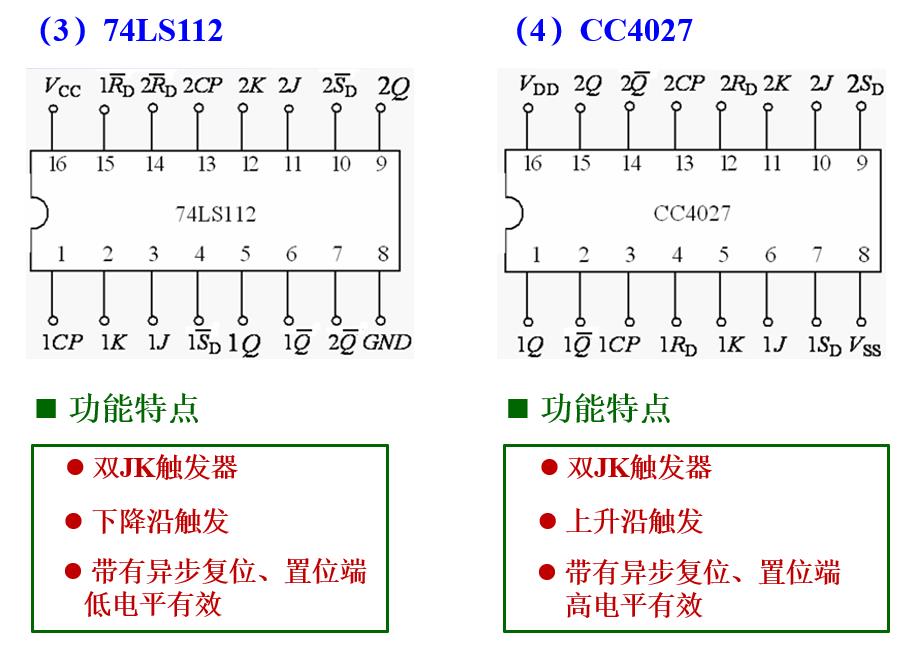

三、集成主从触发器简介

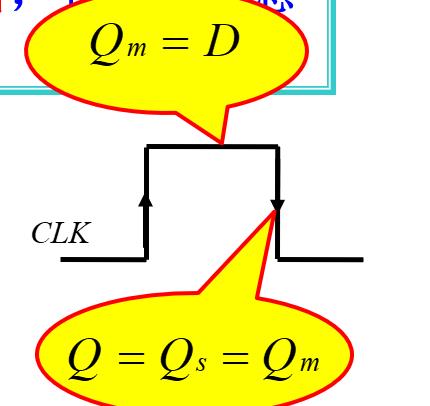

§5.4 边沿触发器(flip-flop)

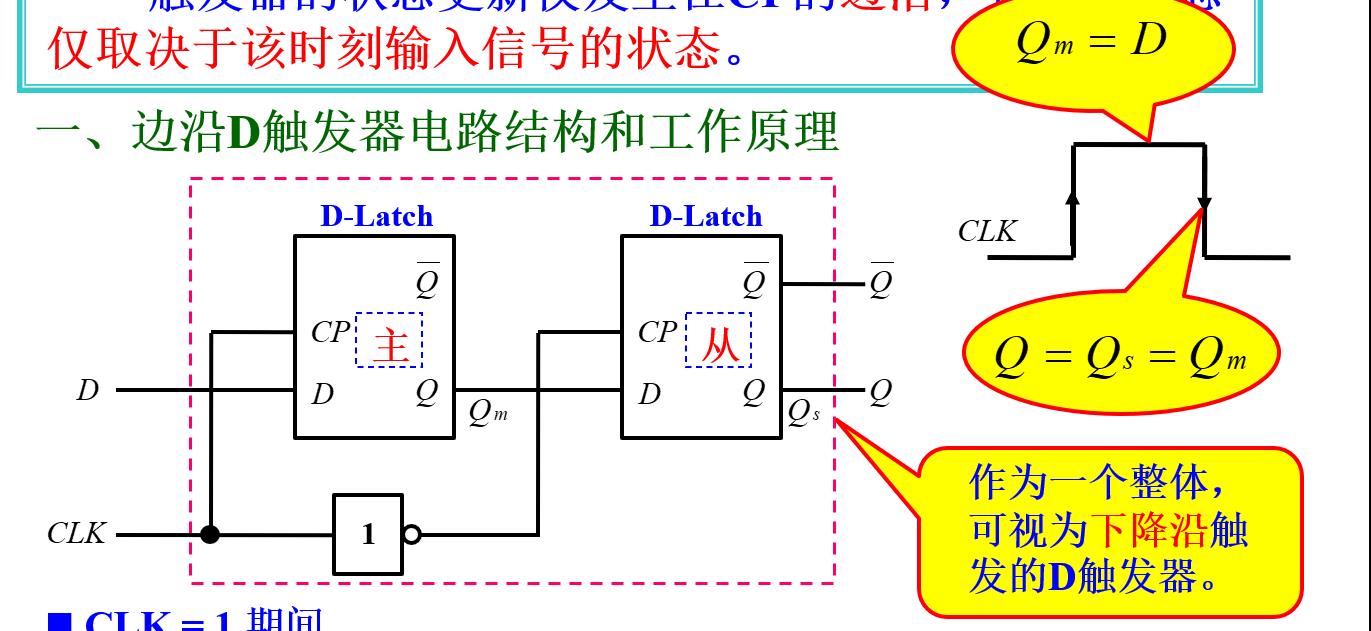

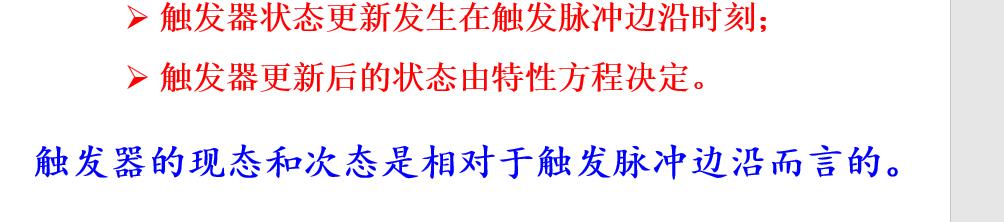

触发器的状态更新仅发生在CP的边沿,且输出状态仅取决于该时刻输入信号的状态

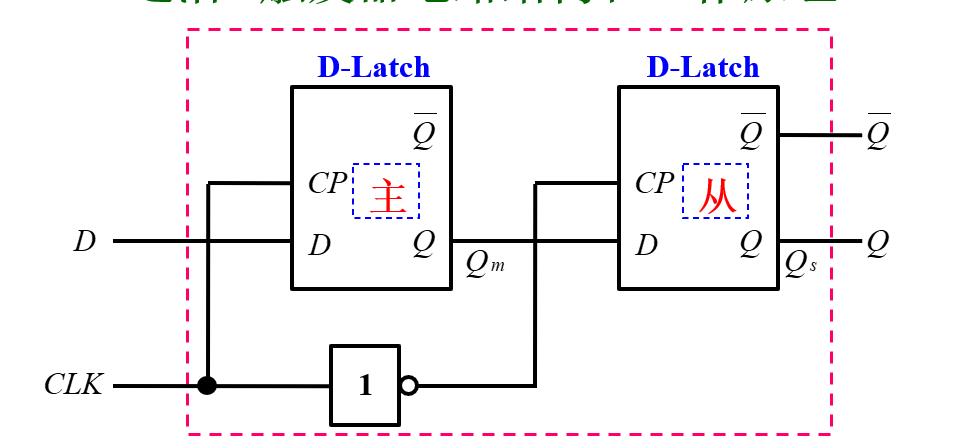

一.边沿D触发器电路结构和工作原理

-

逻辑电路图

-

工作原理

-

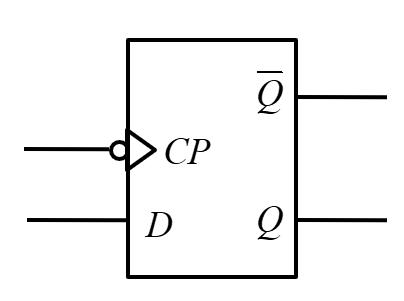

逻辑符号

有圈表示下降沿触发

有圈表示下降沿触发

二.集成边沿触发器简介

§5.5 触发器逻辑功能与描述方法汇总

一.RS触发器

-

特性方程

-

状态表

-

状态转换图

二.JK触发器

形象记忆:J像1 ,置1

口诀:JK触发器,00不变,11翻转;01,10 同 J

-

特征方程

-

状态表

-

状态转换图

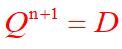

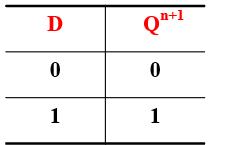

三.D触发器

-

特性方程

-

状态表

-

状态转换图

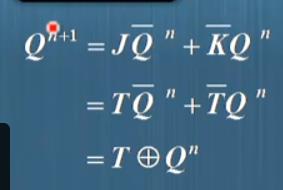

四.T触发器

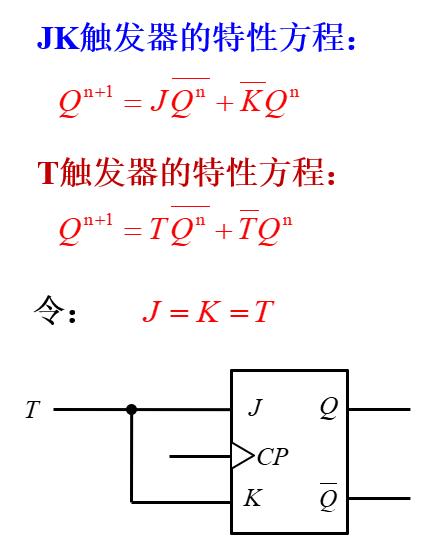

将JK触发器的J和K相连作为T输入端就构成了T触发器

-

特征方程

-

状态表

-

状态转换图

T’触发器

§5.6 不同类型触发器之间的转换

一.D触发器->其他

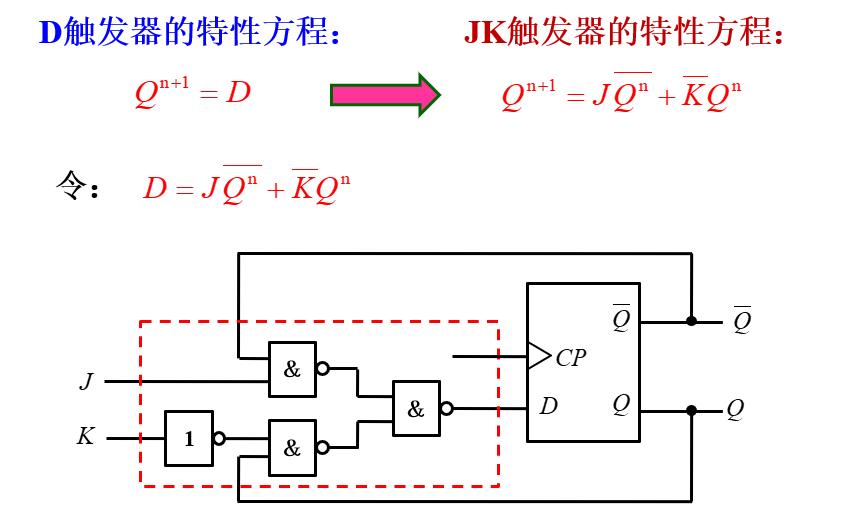

1.D->JK

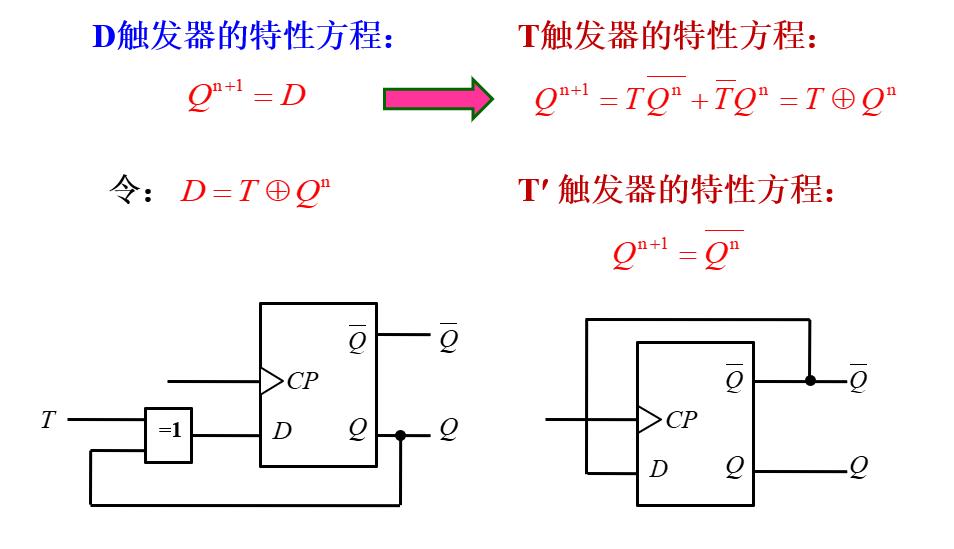

2.D->T/T’

二.JK触发器->其他

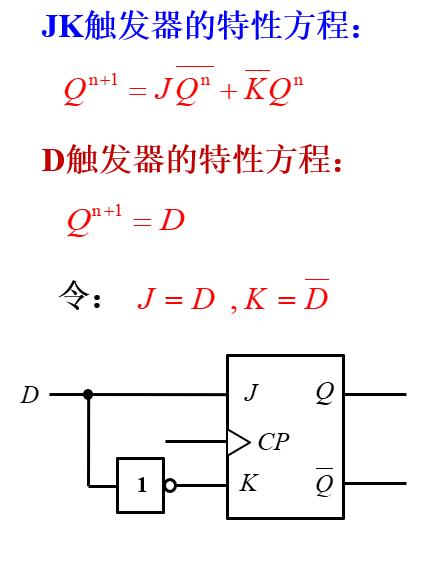

1.JK->D

2.JK->T

§5.7 触发器总结

-

电路结构、逻辑功能、触发方式的关系

-

锁存器与触发器的区别

-

触发器的动作特点归纳

以上是关于数字电路逻辑设计笔记:chap5集成触发器的主要内容,如果未能解决你的问题,请参考以下文章