可调延时网络基于FPGA的可调延时网络系统verilog开发

Posted fpga和matlab

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了可调延时网络基于FPGA的可调延时网络系统verilog开发相关的知识,希望对你有一定的参考价值。

1.软件版本

ISE14.7

2.系统原理

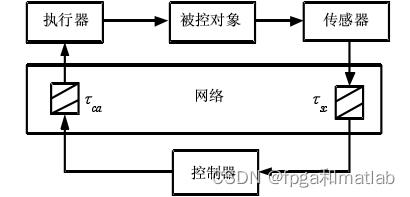

“网络控制系统”一般有两种理解,一种是对网络的控制(Control of Network);另一种是通过网络传输信息的控制系统(Control through Network)。这两种系统都离不开控制和网络,但侧重点不同。前者是指对网络路由、网络数据流量等的调度与控制,是对网络自身的控制,可以利用运筹学和控制理论的方法来实现;后者是指控制系统的各节点(传感器、控制器、执行器等)之间的数据不是传统的点对点式的,而是通过网络来传输的,是一种分布式控制系统,可通过建立其数学模型用控制理论的方法进行研究。图1给出了网络控制系统的结构。本文主要研究的内容正是后者,即:网络控制系统。

图1 网络控制器结构图

在网络控制系统中,通常采用分布式控制方式。分布式控制的结构形式很多,其中一种典型结构形式为基于现场总线的网络控制系统。在这种结构形式中,整个系统通过网络总线形成闭合回路,因此在环路中就存在着由通信延迟带来的时延。当时延远小于采样周期时,其影响可忽略不计;当时间延迟相对采样周期不能忽略时,系统的分析和设计就必须考虑时延的影响。在传感器、执行器和控制器通过网络交换数据时,就产生

以上是关于可调延时网络基于FPGA的可调延时网络系统verilog开发的主要内容,如果未能解决你的问题,请参考以下文章

FPGA开发板自身产生一路信号,差分两路完全一样的方波,但其中一路延时10ns,请问如何设计程序?