学fpga(在线verilog编程)

Posted 费晓行

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了学fpga(在线verilog编程)相关的知识,希望对你有一定的参考价值。

【 声明:版权所有,欢迎转载,请勿用于商业用途。 联系信箱:feixiaoxing @163.com】

很多编程不方便的同学,可以利用在线工具进行编程。比如现在,https://hdlbits.01xz.net/wiki/Main_Page这个网站就非常不错,适合暂时还没有安装quartus、vivado的同学。我们以一个简单的计数器说明如何使用这个网站,

1、打开计数器的关联网页

https://hdlbits.01xz.net/wiki/Count15

2、从截图中可以看出,网站已经准备好了接口

3、补充完整方框中的代码,注意不要修改接口

module top_module (

input clk,

input reset, // Synchronous active-high reset

output [3:0] q);

always@(posedge clk or posedge reset)

if(reset)

q <= 4'b0000;

else if (q == 4'b1111)

q <= 4'b0000;

else

q <= q +1;

endmodul

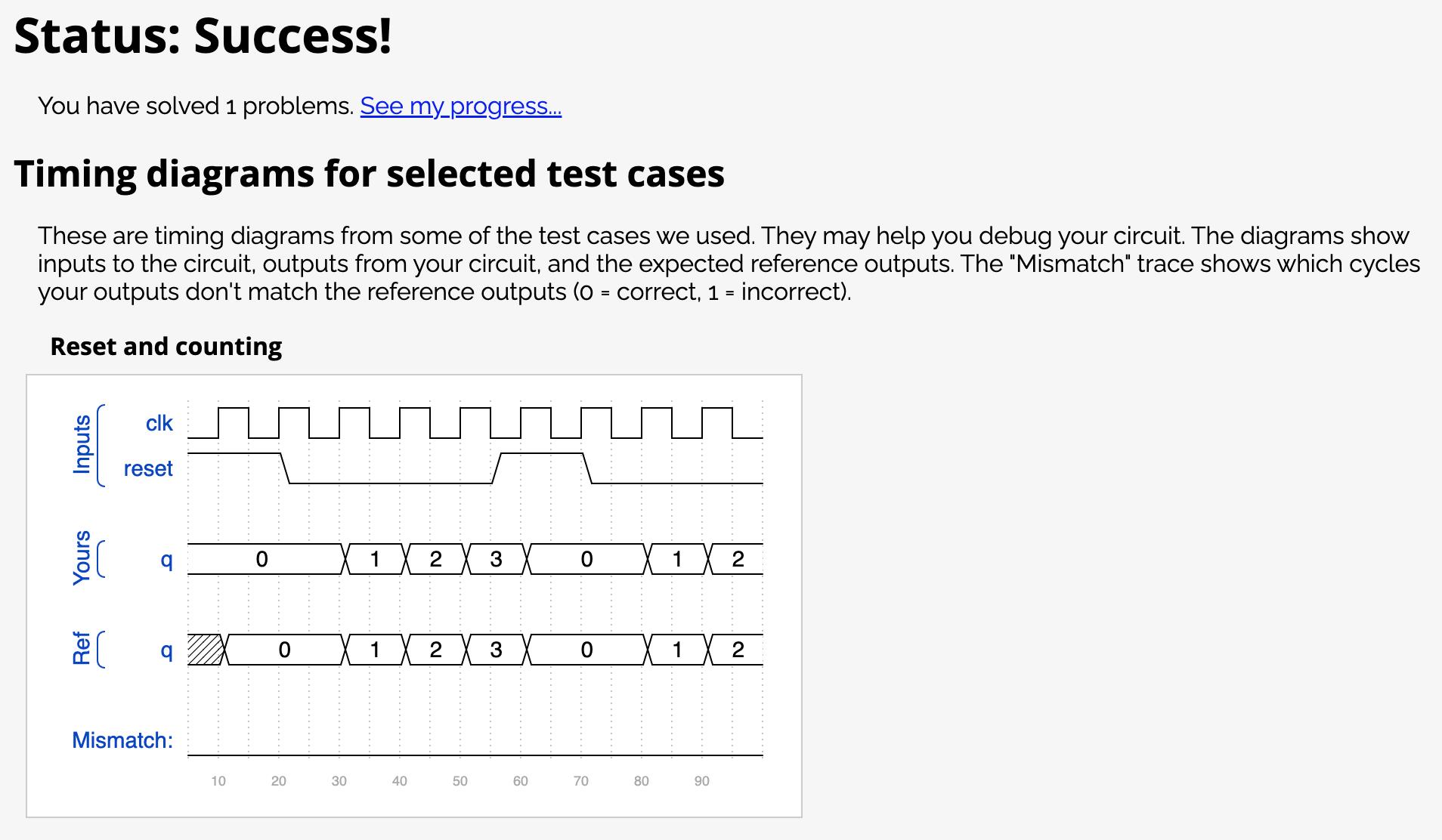

4、单击submit,等待编译和测试,

5、分析错误

通过对比分析,发现题目不要求在reset的时候,对q进行置位操作。所以这里的代码要重新修改。

6、重新修改代码,并且提交

module top_module (

input clk,

input reset, // Synchronous active-high reset

output [3:0] q);

always@(posedge clk)

if(reset)

q <= 4'b0000;

else if (q == 4'b1111)

q <= 4'b0000;

else

q <= q +1;

endmodule

7、确认结果是否ok,判断时序图是否ok

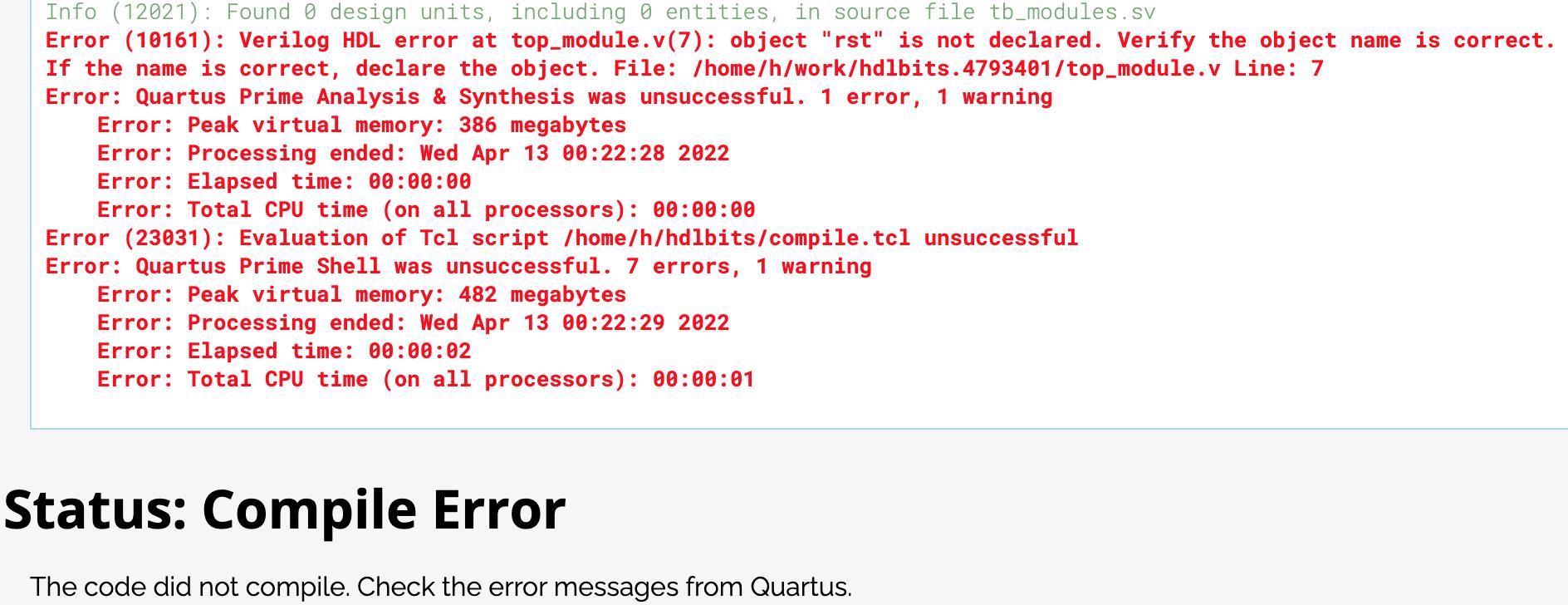

8、其他错误,比如编译错误

如果代码编写的过程中出现了编译错误,系统也会及时给出提示。比如我们故意把reset修改成rst,

因为代码本身长度很短,所以找到错误还是很快。只要多多练习,语法方面的错误很快就能解决。不过这种code->testcase->波形图的思想还是蛮好的。

以上是关于学fpga(在线verilog编程)的主要内容,如果未能解决你的问题,请参考以下文章