verilog 有啥用?

Posted

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了verilog 有啥用?相关的知识,希望对你有一定的参考价值。

学Verilog已经3年了,从模拟到综合感觉学的不错,也有一定的实践经验。但由于我一直在学校,不太知道这个语言在社会上有什么用。因为Verilog主要是做芯片设计,而国内能做芯片生产的厂家和公司应该很少吧~求各位大大解答,小弟感激不尽~

我知道下载到FPGA里可以,但是下载到FPGA里又有什么用呢?

用途我是知道的,我想知道实际工作中有什么用。。。有点小拗口。

就是我知道它可以拿来干什么,但是干完之后出来的结果我不知道拿来干什么。

就像FPGA烧写,烧到FPGA里之后可以用于验证,做实验等等。但这是为了什么。。。不知道我表达清楚了没有。谢谢之前的几位,可能我没有表达清楚。

这个流程我是懂得,但这个流程的最终结果是什么?

verilog里面** 表示这是多少次幂。

verilog里面的算术:

1.加(+):2个操作数相加

2.减(-):2个操作数相减或取1个操作数的负数(二进制补码表示)

3.乘(*):2个操作数相乘

4.除(/):2个操作数相除

5.求幂(**):2个操作数求幂,前一个操作数为底数,后一个操作数为指数

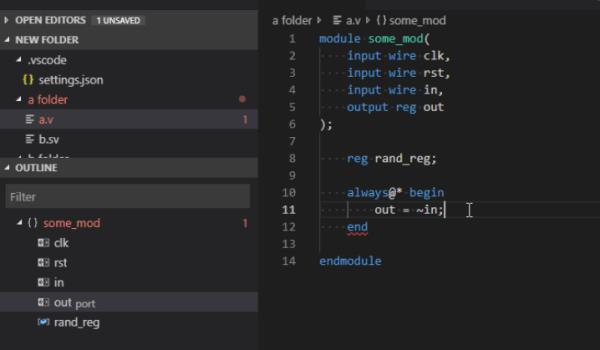

在Verilog中,可以声明两种不同的过程:always过程和initial过程。过程可以是包含时序的过程描述,而不包含时序的过程还可以表达组合逻辑。always过程从关键字always开始,可以连续多次运行,当过程的最后一行代码执行完成后,再次从第一行代码开始执行。如果没有使用系统任务$finish,always过程将不断循环执行。initial过程从关键字initial开始,它只能执行一次。

扩展资料:

Verilog能够在多种抽象级别对数字逻辑系统进行描述:既可以在晶体管级、逻辑门级进行描述,也可以在寄存器传输级对电路信号在寄存器之间的传输情况进行描述。

除了对电路的逻辑功能进行描述,Verilog代码还能够被用于逻辑仿真、逻辑综合,其中后者可以把寄存器传输级的Verilog代码转换为逻辑门级的网表,从而方便在现场可编程逻辑门阵列上实现硬件电路,或者让硬件厂商制造具体的专用集成电路。设计人员还可以利用Verilog的扩展部分Verilog-AMS进行模拟电路和混合信号集成电路的设计。

Verilog代码中用来定义语言结构名称的字符称为标识符,包括变量名、端口名、模块名等等。标识符可以由字母、数字、下划线以及美元符($)来表示。但是标识符的第一个字符只能是字母、数字或者下划线,不能为美元符,这是因为以美元符开始的标识符和系统任务的保留字冲突。

参考资料来源:百度百科——Verilog HDL

参考技术A 不一定要会DSP,verilog是一种硬件语言,可以用来编写FPGA程序,FPGA是一种可编程芯片,在工业应用中它主要体现在开发周期短,可以迅速推向市场,相比开发专用芯片要快的多,但缺点是价格贵。在学生的学习应用方面,只要是用它做控制模块,来开发一些小系统本回答被提问者采纳 参考技术B 学3年了还困惑吗.......我得理解是verilog一开始是功能描述语言.就是把这个芯片所实现的功能记录下来.后来发展成为了芯片设计语言.也就是通过软件.把verilog转化成实际电路.这也是为什么有的verilog可以综合.有的不能综合的原因.你得有一定的风格才能识别成电路.下载到fpga里的是综合后产生的电路图.不是verilog本身.这样说你应该明白了吧. 参考技术C 半定制设计由你的idear变成真正的与门或门非门这些东西的语言。当然重要了啊。你去做几个小项目就行,甚至不用流片,将代码下载到FPGA就行。 参考技术D 呵呵 这个具体要看你要实现什么功能,其实他只是个语言,可以说是工具罢了,具体要实现什么都是我们自己要进行构思的 然后用VERILOG表达出来

dowhile(0) 有啥用? [复制]

【中文标题】dowhile(0) 有啥用? [复制]【英文标题】:What is the use of dowhile(0)? [duplicate]dowhile(0) 有什么用? [复制] 【发布时间】:2012-03-08 04:27:38 【问题描述】:可能重复:Why are there sometimes meaningless do/while and if/else statements in C/C++ macros?What's the use of do while(0) when we define a macro?how does do while(0) work in macro?

我想知道do ... while(0)(... 作为其他代码的占位符)的用途是什么,据我所知,它与使用... 完全相同。

您可以在官方 CPython 源代码中找到这样的代码。例如,Py_DECREF 宏:

#define Py_DECREF(op) \

do \

if (_Py_DEC_REFTOTAL _Py_REF_DEBUG_COMMA \

--((PyObject*)(op))->ob_refcnt != 0) \

_Py_CHECK_REFCNT(op) \

else \

_Py_Dealloc((PyObject *)(op)); \

while (0)

【问题讨论】:

一般来说,它允许您使用break 或continue 跳过剩余的代码,而无需使用goto 或return(完全从函数返回)。在您的示例中,目的非常不同 - 它强制用户使用 ; 跟随宏的使用,而不会引起任何编译器警告。

【参考方案1】:

它使编译器需要;,所以宏看起来像一个函数调用:

Py_DECREF(x); // ok

Py_DECREF(x) // error

【讨论】:

以上是关于verilog 有啥用?的主要内容,如果未能解决你的问题,请参考以下文章