端口为开漏式和推免式的硬件电路设计有啥区别,

Posted

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了端口为开漏式和推免式的硬件电路设计有啥区别,相关的知识,希望对你有一定的参考价值。

端口为开漏式和推免式的硬件电路设计有什么区别,如果硬件电路是按照推免式设计,而软件里面的配置却为开漏式,对该端口有什么影响。如果该端口是用来通信用的,会不会影响通信的稳定性,会有什么影响!希望可以详细点的解释。

开漏式的端口无法拉高,驱动能力有限,所以必须外加上拉电阻拉高。而推挽式端口能够由自身拉高或拉低通讯端口的话,你看看驱动能力方面有没有要求。

希望能够帮到你 参考技术A 开漏式必须外接上拉电阻才能工作(一般接个4.7K的上拉电阻即可)。。。而推挽式则不需要。。。

但是开漏式的好处是:外接的高电平电压由你选定。。而不是像推挽式一样高电平固定的

另外一个好处是可以级联输出。 参考技术B 哇,好专业术语

开漏输出

http://blog.chinaunix.net/uid-23065002-id-3885199.html

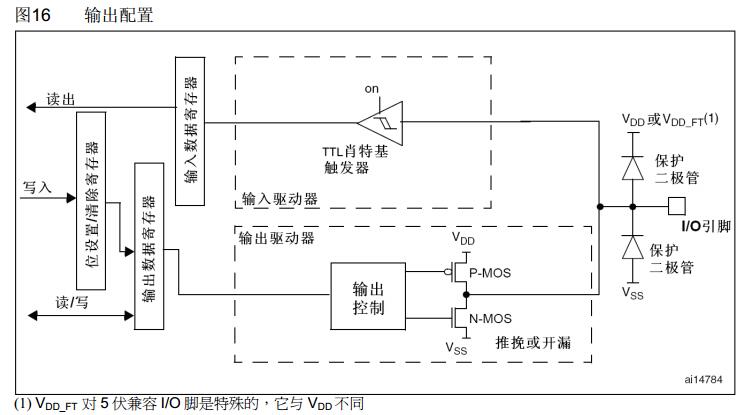

STM32配置为开漏输出(上图)时:输出0,N-MOS导通,IO引脚是低电平;输出1,N-MOS不导通,IO引脚是高阻态(P-MOS从不被激活)。

所以配置为开漏模式时要想IO引脚输出0和1,必须外加上拉电阻。

51单片机P0口开漏:http://www.zybang.com/question/e95bd1ec31e8f1f5cc74ef40c2e66f9d.html

1、可以将多个开漏输出的Pin,连接到一条线上。形成 “与逻辑” 关系。

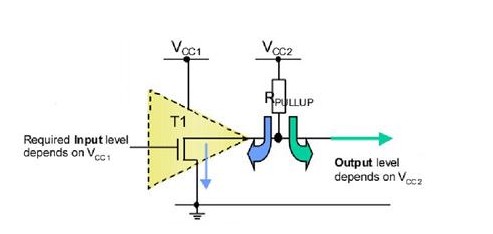

2、可以利用改变上拉电源的电压,改变传输电平。如图2, IC的逻辑电平由电源Vcc1决定,而输出高电平则由Vcc2(上拉电阻的电源电压)决定。这样我们就可以用低电平逻辑控制输出高电平逻辑了(这样你就可以进行任意电平的转换)。(例如加上上拉电阻就可以提供TTL/CMOS电平输出等。)

以上是关于端口为开漏式和推免式的硬件电路设计有啥区别,的主要内容,如果未能解决你的问题,请参考以下文章

TLE5012B 硬件电路设计4线SPI通信,驱动完美兼容4线SPI不用改MOSI开漏推挽输出