SerDes接口——架构与电路

Posted 沧海一升

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了SerDes接口——架构与电路相关的知识,希望对你有一定的参考价值。

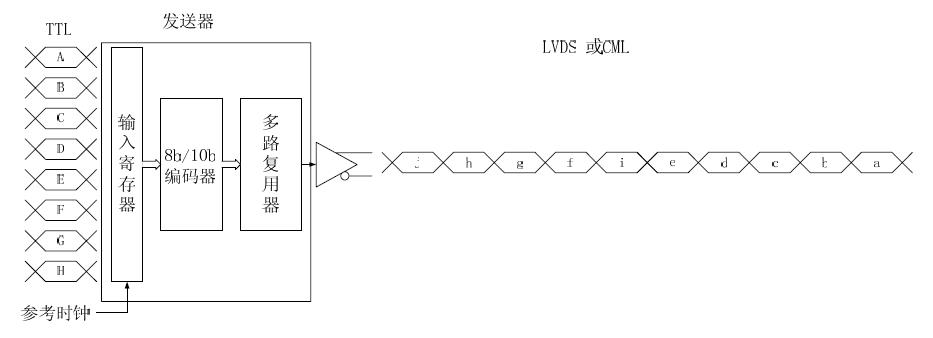

随着通信技术的飞速发展,高速串行互连以其结构简单,不需要传输同步时钟,相比并行传输有更高数据传输效率的优点,成为现代通信和数据传输的重要组成部分。随着对数据传输速率要求的不断提高,SERDES应运而生。它是一种时分多路复用(TDM)、点对点的通信技术,即在发送端多路低速并行信号被转换成高速串行信号,经过传输媒体(光缆或铜线),最后在接收端高速串行信号重新转换成低速并行信号。

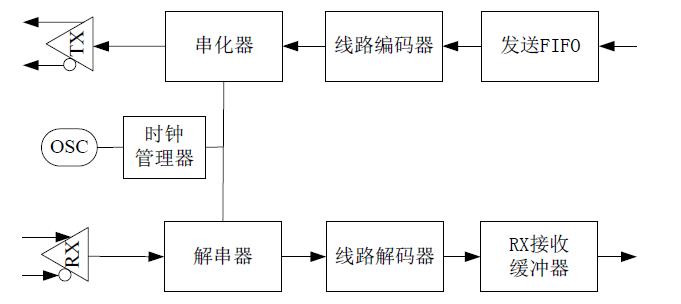

SERDES(Serializer and Deserializer)接口作为高速串行通信的重要组成部分,对其芯片的研究和设计一直是一个热点。SERDES接口由串行器(SER)和解串器(DES)两部分组成,串行器由并串转换电路、发射器组成,结构比较简单,而解串器由接收器、串并转换电路和时钟与数据恢复电路CDR(Clock and Data Recovery)组成,接VI中串行器的功能是将低速的并行信号转换成为高速低压差分信号LVDS(Low Voltage Differential Signaling),然后串化并发送出去,而解串器的功能是接收高速串行LVDS信号并正确地转换为低速并行信号。在基本的SERDES模块中,SERDES内部的时钟频率必须要大于外部参考时钟的频率。

其采用的一些技术也突破了传统并行I/O 接口的数据传输瓶颈,比如,(一)采用差分信号传输代替单端信号传输,从而增强了抗噪声、抗干扰能力;(二)采用时钟和数据恢复技术代替同时传输数据和时钟,从而解决了限制数据传输速率的信号时钟偏移问题;(三)采用了多路复用技术(TDM),增加了系统传输带宽,给PCB 版图布线带来了极大的方便。

一、SerDes 接口常用构架

SerDes芯片广泛的应用于通信系统的信号传输中,但是大多数通信系统设计者在选择SerDes芯片时,往往只是考虑芯片的功耗和速度,而忽略了SerDes芯片的工作机制和原理。SerDes芯片的内部构架看似不相关,其实构架的不同决定了整个系统在设计时许多重要参数的不同,例如系统的拓扑结构,底层协议,数据格式,以及延迟,时钟等要求都是需要考虑的。这些因素对系统的开销,性能具有重要的作用。

现在主要由四种SerDes结构,分别是并行时钟SerDes,嵌入时钟SerDes,位交错SerDes以及8b/10b SerDes,下面分别介绍这四种SerDes结构。

1、并行时钟SerDes

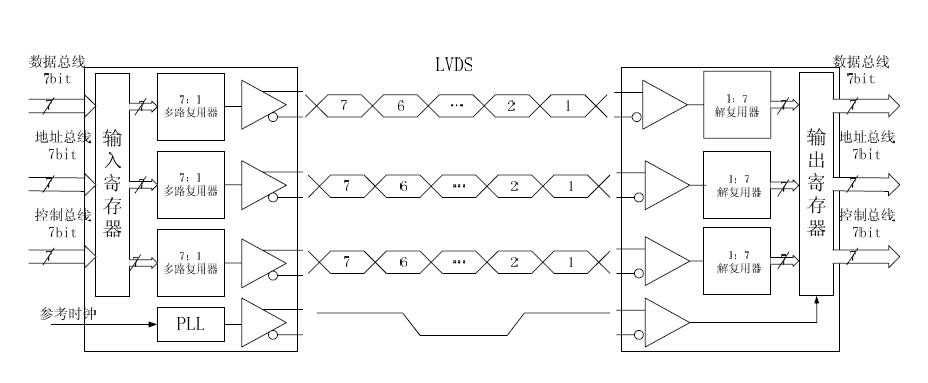

并行时钟SerDes常常用于串行化“数据-地址-控制”并行总线,例如PCI,UTOPIA,处理器总线,控制总线等。这种SerDes架构不再用一个多路复用器去解决整个总线,而是利用一组多路复用器(N~1位)去串行化并行数据,每个多路复用器分别串行化一部分总线。串行数据连同一个附加的时钟信号并行到达接收端,接收器用这个时钟信号锁存并恢复数据。

这里有多对时钟/数据对,因此要确保对与对之间的偏移最小,这样才能保证解串的正确性。尽管有多对串行线,但是并行时钟SerDes仍旧拥有更小功耗,更少的数据线,更大的驱动能力,更低的噪声等优点。并行时钟SerDes提供了一种性价比高的解决方案。

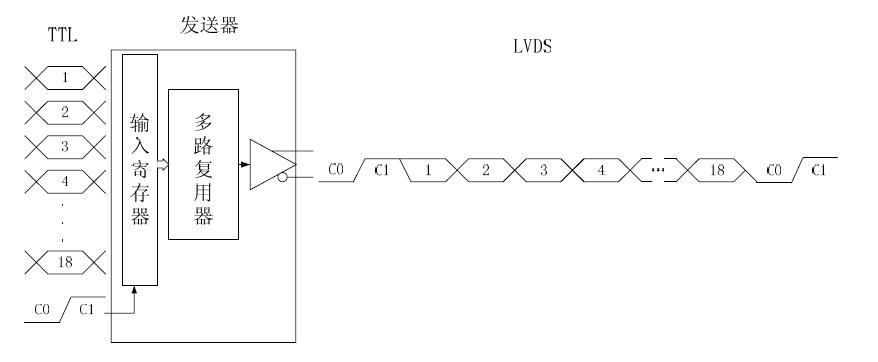

2、嵌入时钟SerDes

嵌入时钟 SerDes将数据总线和时钟转换为一个串行差分对进行传输。两个时钟位(一低一高)嵌入进数据流中,作为每个时钟周期的数据帧结构的起始位和结束位,并在串行数据流中产生周期性的时钟上升沿。

上电之后,接收器自动搜索周期性的时钟上升沿。由于数据位的值随时间改变,同时时钟位不变,所以接收器能够唯一定位时钟沿及同步时钟沿。一旦锁定,接收器就从串行流中恢复数据(不管数据为何种形式)。这种自动同步的能力通常称为“锁定随机数据(lock to random data)”,它不需要系统的外部干预。由于接收器是被锁定为接收的嵌入时钟,没有外部的参考时钟,则对时钟的抖动要求是相当宽松的(对接收器和发送器都是同样的)。相比于其他结构的SerDes 芯片,嵌入时钟SerDes 的结构比较简单,在系统级的应用也不复杂。

3、位交错SerDes

位交错 SerDes 复用低速的SONET/SDH 或8b/10b 串行数据流,通过交差比特位转换为更快速的串行数据流。在接收端,接收器解复用比特流转换为低速的码流。由于高速特性以及低抖动的要求,位交错SerDes 要求非常精确的外部时钟。

位交错 SerDes 芯片常用于电信传输设备上,例如分插复用器,准光学转换器等以加强SONET/SDH 数据流通过电缆或光纤传输到核心网的能力。

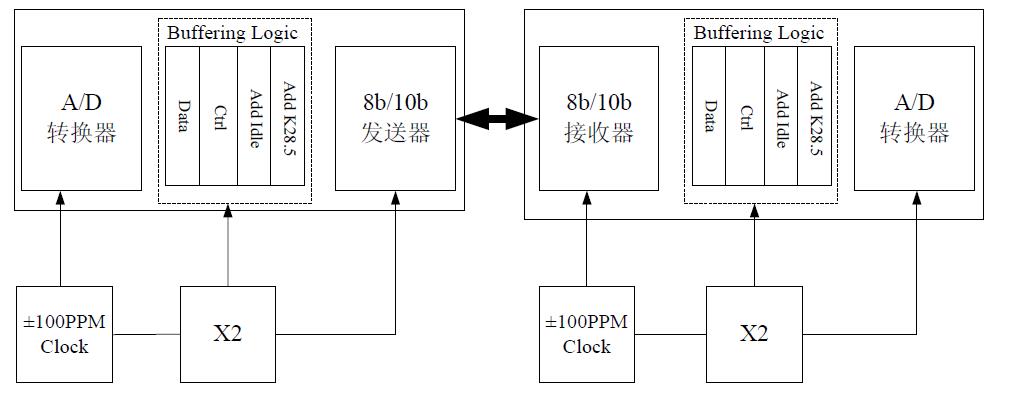

4、8b/10b SerDes

8b/10b SerDes将并行数据映射为10 比特码,再串行传输出去。8b/10b 的编码方式要求满足一个时钟的双沿传输和达到直流平衡。为了定位10 比特码的边沿,发送器通过发送一种特殊的comma 字符来标记数据流的帧头,这种特殊的comma 字符永远不会出现在普通的数据中,这样在接收端,利用Comma 检测器来检测串行码流中的特殊Comma 字符,将串行码流划分成字边界正确的10bit 8b/10b 编码,送到解码器进行解码,得到和发送端相同的字节信息。8b/10b SerDes 对外部时钟的抖动要求较高。

8b/10b SerDes 适合传送字节数据,许多标准都运用8b/10b 编码技术,例如以太网,光纤通道,InfiniBand 等,传输速率涉及1.0625Gbps、1.25Gbps、2.5Gbps、3.125Gbps 等。在相同的应用中,8b/10b SerDes 的系统相对较复杂,额外的非字节的控制信息必须用带buffer 缓冲,再以字节的格式发送。

二、8b/10b SerDes典型结构

下面我们就重点探讨8b/10b SerDes的内部结构。

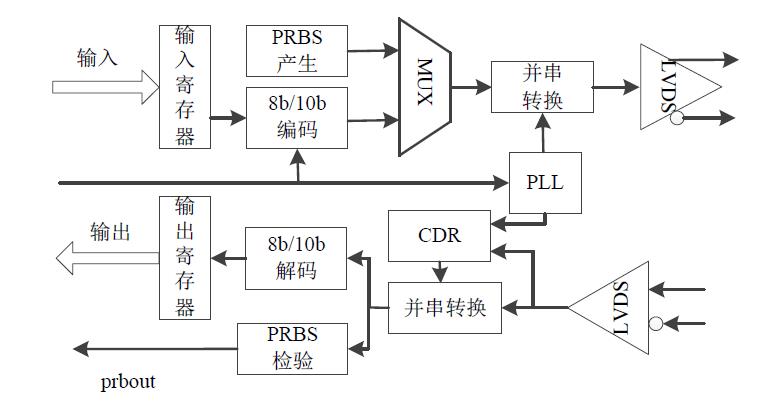

1、锁相环

SerDes作为一种高速串行传输的接口,它需要高质量低抖动的时钟,而且在将并行数据转换为串行数据时,需要将并行数据的时钟频率提高10倍或20倍,产生高速串行数据的时钟。因此,我们有必要设计高质量的锁相环和频率合成器,来保证提供的时钟具有高质量、高频率、低抖动。

锁相环总的来说是一个负反馈跟踪控制系统,它完成了对压控振荡器(VCO)所产生频率的控制和稳定。通过这样一个系统,压控振荡器产生的时钟就可以稳定的作为其他系统的时钟进行使用。锁相环最重要的一个应用就是产生稳定的时钟。

2、时钟数据恢复电路

CDR主要功能是接收输入高速串行信号并判断信号的相位,从中提取出时钟信息。

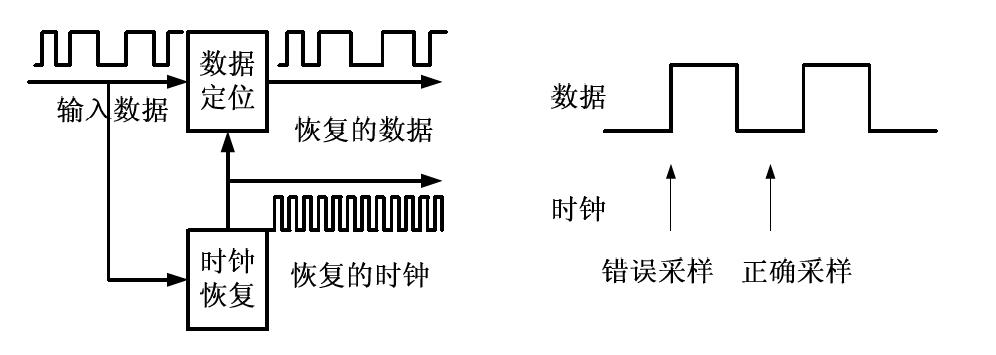

实际的系统中,当高速信号在PCB 板级电路或者线缆中传输时,由于路径距离和寄生电容等因素影响,信号从发送端到达接收端的时候,已经产生了随机的延迟,再加上传输过程中所引入的抖动和发送端和接收端同步时钟固有的频率偏差,将会使接收端采样时钟的相位与接收数据

的相位发生了偏差。在高速条件下,数据的码元周期都比较小,一旦相位偏差超过一定的范围,就会发生采样错误。为了能够正确的对输入数据进行采样,满足系统传输误码率的指标要求,CDR 模块必须能够根据本地时钟和输入数据的相位差来正确的调整本地采样时钟的相位,以保证采样时钟的相位能够位于输入数据码元的中间位置。

下图描述了一个简化的时钟和数据恢复电路的原理,时钟恢复电路检测输入数据的跳变沿并调整本地采样时钟的相位。数据恢复电路利用调相后的时钟对相位飘移的输入数据进行采样输出。理想情况下,时钟采样时刻应该位于数据的中间位置,假若时钟采样时刻位于数据跳变沿位置,则容易产生采样错误。

3、LVDS 收发器

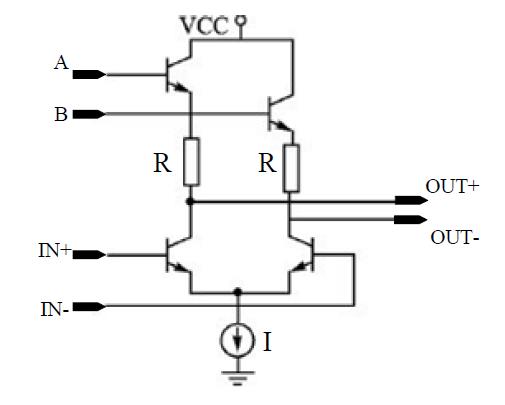

LVDS(Low Voltage Differential Signal) 信号标准是高速串行通信中常用的接口标准之,是一种小振幅差分信号技术,其电路如下:

LVDS使用非常低的幅度信号(100~450mV) ,通过一对平行的PCB 走线或平衡电缆传输数据。在两条平行的差分信号线上流经的电流方向相反,噪声信号同时耦合到两条线上,而接收端只关心两信号的差值,于是噪声被抵消。由于两条信号线周围的电磁场也互相抵消,故差分信号传输比单线信号传输电磁辐射小得多,从而提高了传输效率并降低了功耗。

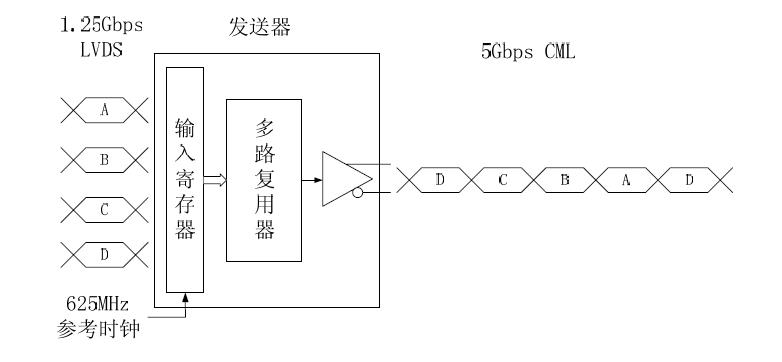

此外,除了LVDS接口标准,现在少数厂商生产的SerDes芯片中还运用了CML(Current Mode Logic)接口标准。虽然CML接口缺少严格的技术规范标准,但是它的应用越来越广泛。由于CML的电路结构是所有高速数据接口形式中最简单的一种,且它的数据传输率可以达到2.5 Gbps甚至更高,较之CMOS电路,CML电路可以在较低的电源电压条件下实现低摆幅、高频率的工作状态。

4、8B/10B 编码器

8B/10B 编码方式是1983 年由IBM 的A.X.Widmer 所提出,其根据规定的映射机制将原来的8 比特数据转化成特定的10 比特数据。8B/10B 编码器通过均衡映射后的数据流中0 和1 的数量来获得直流平衡的码字,而这些直流平衡的码字可以为后面的时钟恢复电路提供满足要求的状态翻转次数。

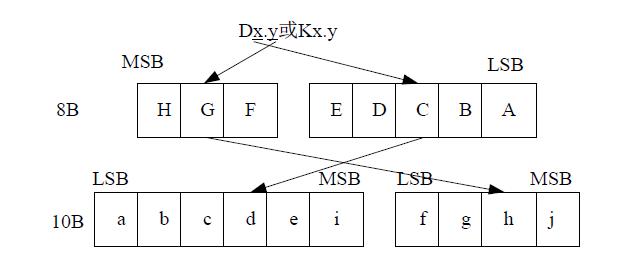

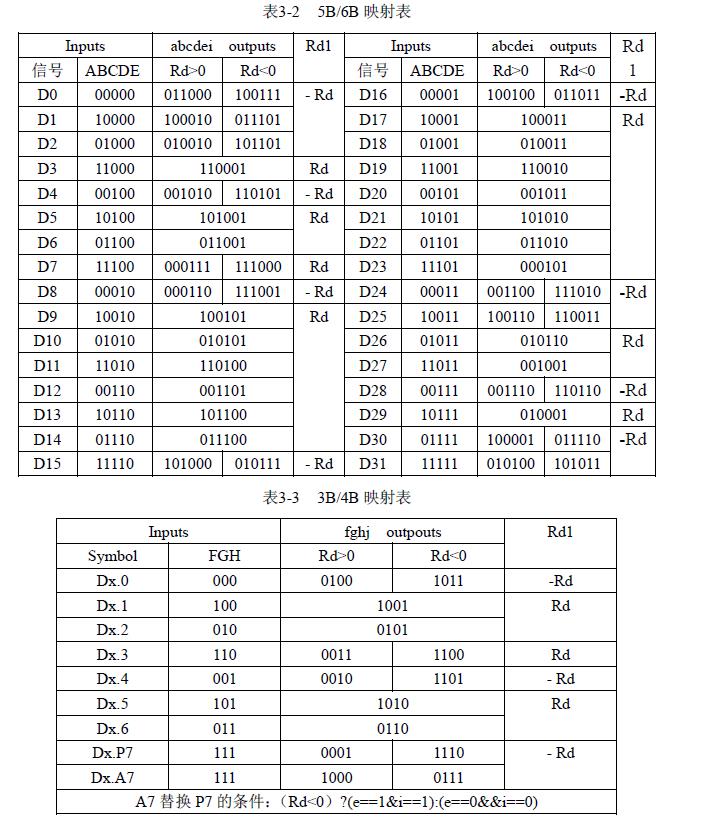

8B/10B 编码原理是将一组连续的8 位字节数据分解为2 组数据:一组为3 比特,另一组为5 比特。分别对2 组数据进行编码获得4 比特和6 比特数据,然后组成10 比特数据。我们利用Dx.y 表示256 个数据字符,利用Kx.y 表示12 个特殊控制字符。

下图表示出了具体的映射关系,Dx.y 中x 用高3 位二进制表示,y 用低5 位二进制表示,8 比特并行数据中的高三位HGF 被编码成jhgf,低5 位EDCBA 被编码成iedcba,两组数组成编码后的10 位并行数据abcdeifghj。

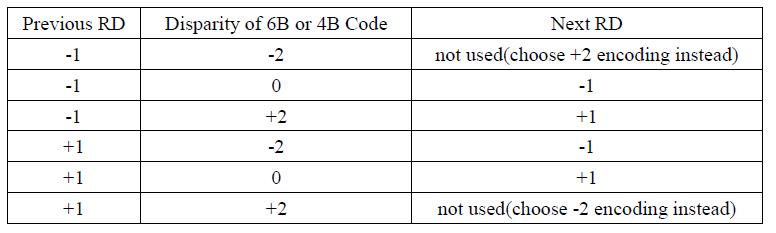

同时为了保证数据流的DC 平衡,在编码过程中还需要表示不平衡度的极性偏差值RD(Running Disparity)。所有有效的8B/10B 码字中0 和1 的数量差只有3中情况:0、+2、-2。当码字中1 的个数比0 的个数多两个时RD 值为1,,当0 的个数和1 的个数相等时RD 值为0,而当0 的个数比1 的个数多两个时RD 值为-1。

为了维持数据流中的直流平衡性,码字机制要求每个码字的RD 值须与前一个码字的RD 值互为相反值,所以在对当前码字进行编码时需要参考前一个码字的RD 值来进行编码,下表所示为下一时刻的RD 值与之前的RD 值和当前码字的RD值的关系:

因为协议规定RD 的初始值为-1,所以在编码过程中RD 只会出现+1 和-1 两种情况,从而需要编码的字符会根据2 种不同RD 值产生两种不同的编码结果,并且将编码后更新的RD 用于下一个码字的编码。

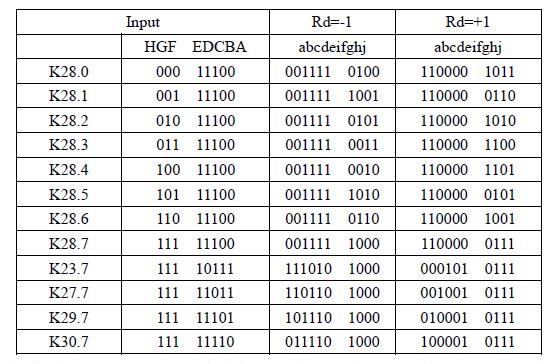

用于编码的映射机制规定了268 种有效字节的对应方式,其中包括针对256 个数据字符编码机制和12 个特殊控制字符的编码机制。如下表:

上表的3B/4B 模块中出现Dx.7 的情况时需要特殊处理,此时如果Dx.7 和5B/6B 模块中的Dx 组合在一起被编码时需要避免产生连续5 个0 或1 的情况。如果碰到连续5 个0 或1 的情况则认为是表征字符边界的comma 信号。

控制码字Kx.y 的映射关系,8B/10B 标准使用12 个特殊的控制码字。在控制码字中,K28.5、K28.7 为表征字符边界的comma 序列。

在接收端的8B/10B 解码模块实现的功能是编码的逆过程,需要将编码后的10bit 数据根据映射表映射成8bit 的原始数据,同时还需要实现错误字符的检测功能。

serdes接口原理

更新:2018年11月18日 第一次建立。以后补上。。。

随着fpga的速度越来越快,稍微高端一点的fpga都有serdes接口,到底这个接口是干什么的?如下:

以上是关于SerDes接口——架构与电路的主要内容,如果未能解决你的问题,请参考以下文章