随机存取存储器SRAM

Posted 天“码”行空

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了随机存取存储器SRAM相关的知识,希望对你有一定的参考价值。

前面,我们根据半导体存储(主存储器)的工作方式分为两类:一类是随机存储器(RAM),另外一类是只读存储器(ROM)。

这一讲,我们重点来学习随机存取存储器。随机存取存储器主要用来存放的程序,各种输入输出数据,中间运算结果,堆栈等。我们说随机存取存储器有两个特点,其一是它可以随机的读写,其二是断电后内容会消失。根据制造工艺的不同,RAM可分为双击型半导体RAM和和金属氧化物半导体(MOS)RAM。用MOS器件构成的RAM可分为静态读写存储器SRAM和动态读写存储器DRAM。

SRAM的存储元是双稳态电路,双稳态电路有什么特点呢?双稳态存储器有两个稳定状态,可用来存储一位二进制信息。只要不断电,内容不消失。DRAM的存储元是电容,电容会漏电,所有时间长了不稳定,需要刷新(定时将存储单元中信息读出在写入),这是由系统自动完成的。

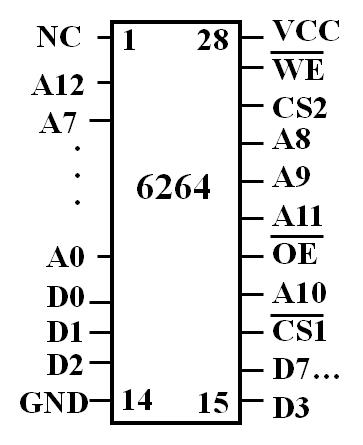

6264存储芯片

6264芯片是一个8K×8b的CMOS SRAM芯片,其共有28条引出线,包括13条地址信号线,8条数据信号线,及4条控制信号线。

(1)A0~A12 : 13位地址信号线。一个存储芯片上的地址线的多少决定该芯片的存储单元数量。这是因为编码的原因。一根地址线可以表示0,1两个地址数,两根地址线可以表示00,01,10,11四个地址数,三根地址线就可以表示000,001,010,011,100,101,110,111八个地址数,那么13跟地址线就可以表示2^13个地址数,相当于有这么多个内存单元。2^13=8192=8K,从而保证芯片上8K个单元每个单元有唯一的地址,即芯片上13个地址线上的信号经过芯片的内部译码,可以决定选中6264芯片上8K个存储单元的哪一个。对于选中哪一个,这是系统的事情,对程序员是透明的。那么CPU要能够寻址6264上某个内存单元,说明该地址信号线一定要与CPU的地址总线连接起来,至于这么连,等会再说。

(2)D0~D7:8根双向数据线。为什么是双向的,可读可写嘛。比如说,CPU通过地址总线寻址到某一内存单元,要读取该内存单元的值,那么该内存单元的值(8位二进制数)通过数据线送到CPU。我们刚才已经默认了,8位,为什么是8位?然后数据线是8根。难道这是巧合吗?不是,正是8根数据线说明一个存储单元可存放8位二进制数。使用这8位数据线与CPU数据总线相连,读出和写入的数据通过该数据线传送。

(3)#CS1,CS2:片选信号线。当CS1为低电平,CS2为高电平(#CS1=0, CS2=1)时,该芯片被选中,CPU才能对其读写。原则:所有片选信号同时有效才有效。片选信号,其实就是选芯片的。对此我们做如下解释:我们知道一个6264芯片是8K字节(从0000----8191)。但是如果说,我需要一个32K的内存空间,那么显然一个6264肯定不够。至少需要4个6264芯片。每个都是从0000----8191,那么如何区别是第一个芯片上0015号内存单元,还是第二个芯片上的0015号内存单元,还是第三个或者第四个呢?就好比一个小区有10栋楼,你的朋友告诉你他家住5楼,那么你应该这么知道他家具体是哪呢?所以,你必须问他是哪栋楼。那么同样的道理,这么多芯片如果我跟每一个芯片标个号,比如上述4个芯片分别是00,01,10,11你就能确定是哪一个芯片了。那么如何确定是哪一个6264被选中呢?这里,我们会发现一个问题,就是对于CPU而言,已有13跟地址总线被占据,那么还剩下7根地址总线。这7根地址总线,每根都有0,1两个数可以对其进行编码,确定一种编码,对应一个芯片。既然输入是不确定的,我们可以利用译码电路,并且对其输出固定。这样输出只要连上片选信号,就可以了。那么我们知道一个片选信号#CS1,只有低电平有效,所以让它接译码电路的输出端。故#CS1=0,使得译码电路输出为0,输入根据译码电路的设计不同而不同,而输入的值与6264的序号对应,从而实现片选。

(4)#OE:输出允许信号。只有当#OE=0时,CPU才能从芯片中读出数据。写时,可以允许#OE=1。

(5)#WE:写允许信号。低电平有效。

(6)VCC为5v电源,GND接地,NC空端。

6264存储芯片的工作工程

对6264芯片的存取操作包括数据的写入和读出。

写入

什么叫写入?所谓写入,就是将数据放入指定的存储单元中。

它的过程是怎样的呢?

首先,你要知道数据放在哪个存储单元中?这要通过地址线确定。也就是说把要写入单元的地址送到芯片的地址线A0~A12上。这个单元存放的是一个字节,8位二进制数。只要将写入的数据送到数据线即可。还没完,这么多6264芯片,选哪个呢?所以要使#CS1,CS2同时有效。同时再在#WE端加上有效的低电平,#OE端任意。

读取

什么是读取呢?读就是读取某一内存单元的数据。

首先,你要知道读取哪个存储单元中的数据?这要通过地址线确定。也就是说把要读取单元的地址送到6264芯片的地址线A0~A12上。这个单元存放的是一个字节,8位二进制数。只要将要取出的数据送到数据线即可。还没完,这么多6264芯片,选哪个呢?所以要使#CS1,CS2同时有效。同时再在#OE端加上有效的低电平,#WE端为1。

6264芯片的应用

在对SRAM芯片的外部引脚功能和工作时序有一定了解后,需要进一步掌握的是如何与系统连接。将一个存储器芯片接到总线上,除了部分控制信号和数据信号线的连接外,主要是如何保证该芯片在整个内存中占据的地址范围能够满足用户的需要。前面已经知道,芯片的片选信号由高位地址信号和控制信号的译码产生,事实上正是高位地址信号决定了芯片在整个内存中占据的地址范围。

(1)地址译码

先举一个例子来说明译码的概念。假设把存储器看成一个居民小区,那么构成存储器的存储芯片就是小区里一座一座的居民楼(楼号01---30),而存储单元就是楼内各个居住单元(单元号101---825)。如果某户居民住10号楼510单元,就可记为10-510。要访问10-510住户,首先要找到楼号10,这就是片选译码(选择一个存储芯片);然后在找510单元,这就是片内寻址(选择一个存储单元)。片内寻址由存储芯片内部完成,使用者无需考虑。使用者要考虑的只是如何根据地址找到具体的住宅楼(芯片)。

因此,所谓译码,就是将一组输入信号转换为一个确定的输出。在存储器技术中,译码就是将高位地址信号通过一组电路(译码器)转换为一个确定的输出信号(通常为低电平),并将其连接到存储器芯片的片选端,使芯片被选中,从而使系统能够对该芯片上单元进行读写操作。选择哪个6264存储器芯片,可以由我们决定,但是对于具体的存储单元,这个对程序员是透明的。

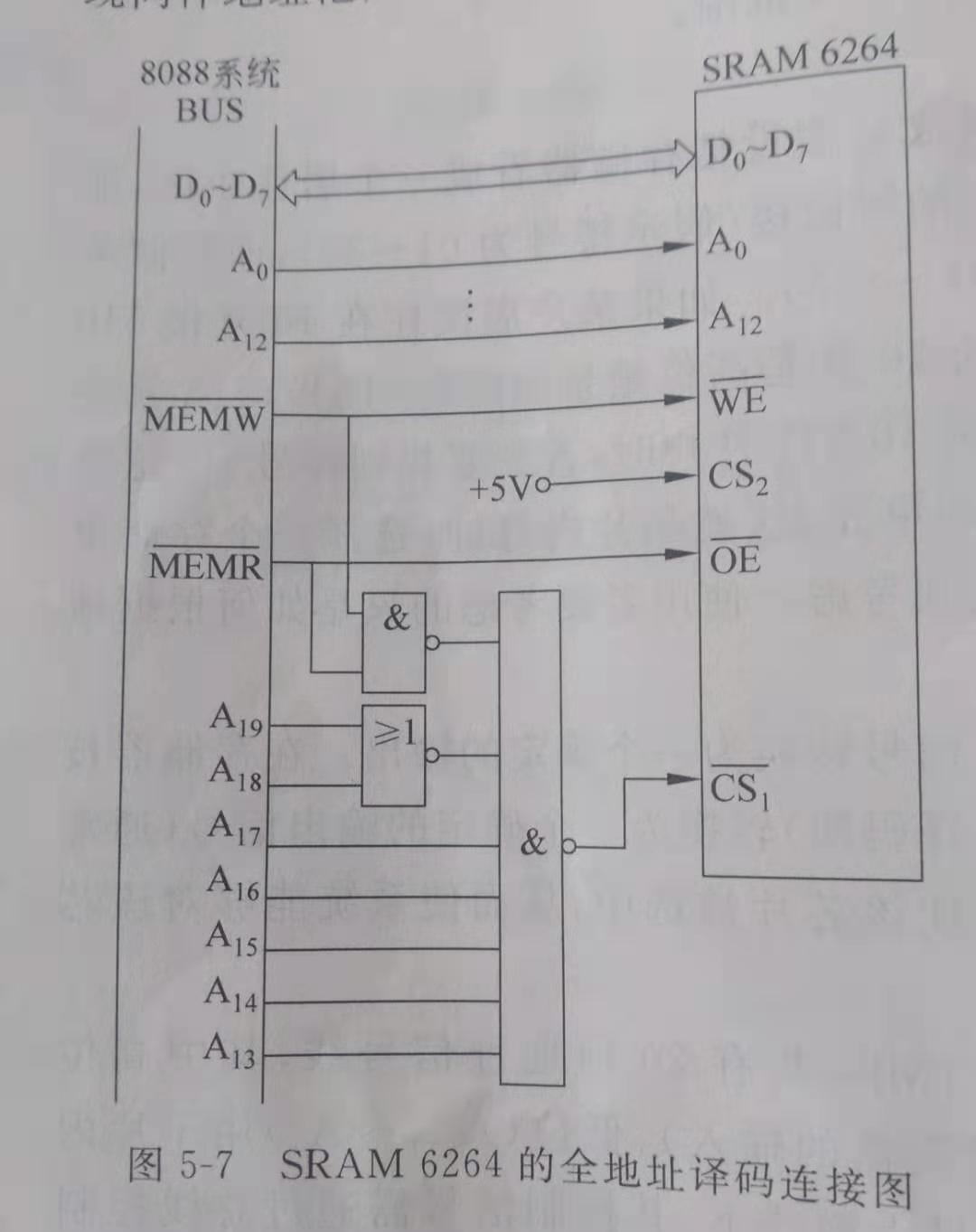

注意:在微机系统中,CPU通常工作在最大模式下,其控制信号需要通过总线控制器与系统控制总线连接。因此对存储器的读写,不是要求最小模式下的读写控制信号#RD和#WR有效,而是要求总线控制信号#MEMR和#MEMW有效。

(2)地址译码方式

存储器的地址译码方式可以分为两种:全地址译码和部分地址译码。

a.全地址译码方式。所谓全地址译码方式就是说构成存储器时要用到全部20位地址总线,即所有的高位地址信号全部用来作为译码器的输入,低位地址信号接存储器芯片的地址输入线,从而使得存储器芯片上的每一个单元在整个内存空间中具有唯一的地址。

如图所示是一片SRAM6264与8086的连接图。可以看出当A19~A13为0011111时,译码器输出低电平,使SRAM的片选端#CS1有效,该芯片被选中。该芯片的存储单元的范围是3E000H~3FFFFH(低13位可以是全为0或者全为1之间的任何一个值)。

译码电路的构成不是唯一的,可以是基本逻辑门电路构成的译码器或专门译码器进行译码。图中用的是基本逻辑门电路。

再如上图,利用了一个74LS138,因为#G2A,#G2B要低电平使能,所以A19和A18只能是0,0;A17,A16只能是1,1,要使#Y7为0,那么A15,A14,A13都必须为1。所以A19~A13为0011111。如果对基本逻辑门电路进行修改,则6264的地址范围会发生变化。由此可以看出,使用不同的译码电路可以将存储器芯片映射到内存空间的任意一个范围中。

b.部分地址译码方式。顾名思义,就是地址总线的一部分地址信号线与存储器连接,通常使用高位地址信号的一部分作为片选译码信号。

上图是一个部分地址译码的例子,可以看出,该6264连接的系统高位地址可能有好几种情况。A19~A13:1010111,1011111,1110111,1111111。即该6264芯片被映射到以下4个内存空间中:AE000H~AFFFFH, BE000H~BFFFFH, EE000H~EFFFFH, FE000H~FFFFFH。该存储器芯片占据了4个8KB的内存地址空间,而6264只有8KB个内存空间。为什么会这样?原因就在于高位地址译码并没有利用地址总线上的全部地址信号,而是利用其中的一部分。这种只用部分地址线参加译码而产生地址重复区的译码方式就是部分地址译码的含义。按这种地址译码方式,芯片占用的这4个8KB的区域绝不可再分配给其它芯片,否则会造成总线竞争而使微机无法正常工作。另外对6264进行存取时,可以使用以上4个地址范围的任意一个。

部分地址译码使地址出现重叠区,而重叠区的部分必须空着不准使用,这就破坏了地址空间的连续性,也减少了总的可用存储地址空间。

以上是关于随机存取存储器SRAM的主要内容,如果未能解决你的问题,请参考以下文章