Lattice CrosslinkNx LIFCL-40应用连载6:搭建HDMI(DVI)发送系统

Posted _Hello_Panda_

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了Lattice CrosslinkNx LIFCL-40应用连载6:搭建HDMI(DVI)发送系统相关的知识,希望对你有一定的参考价值。

作者:Hello,Panda

一、目标

利用LICFL-40 FPGA接口的高速LVDS差分对实现HDMI显示测试视频,分辨率为1920×1080,帧率为30Hz,显示生成的RGB格式标准彩条测试图像。

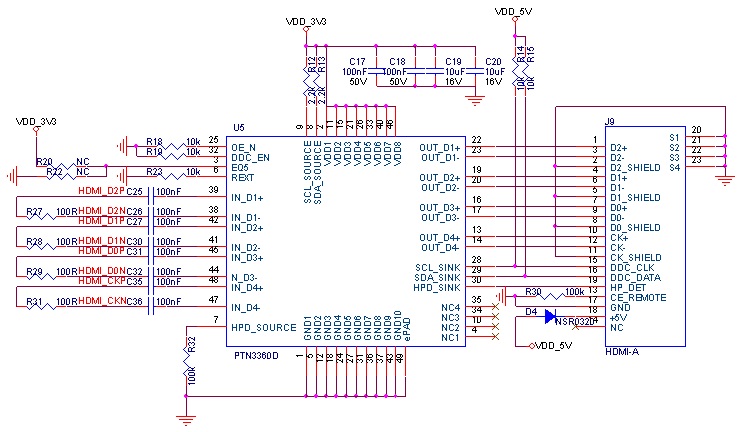

二、硬件电路

硬件电路如下图所示,LIFCL-40 FPGA的高速LVDS信号经NXP的交流耦合电平转换和驱动芯片PTN3360D后变为TMDS_33信号经HDMI Type-A接口输出到显示屏显示。

图1 HDMI显示电路

三、软件设计

本节描述设计软件,开发工具为Radiant3.0。

3.1 设计原理

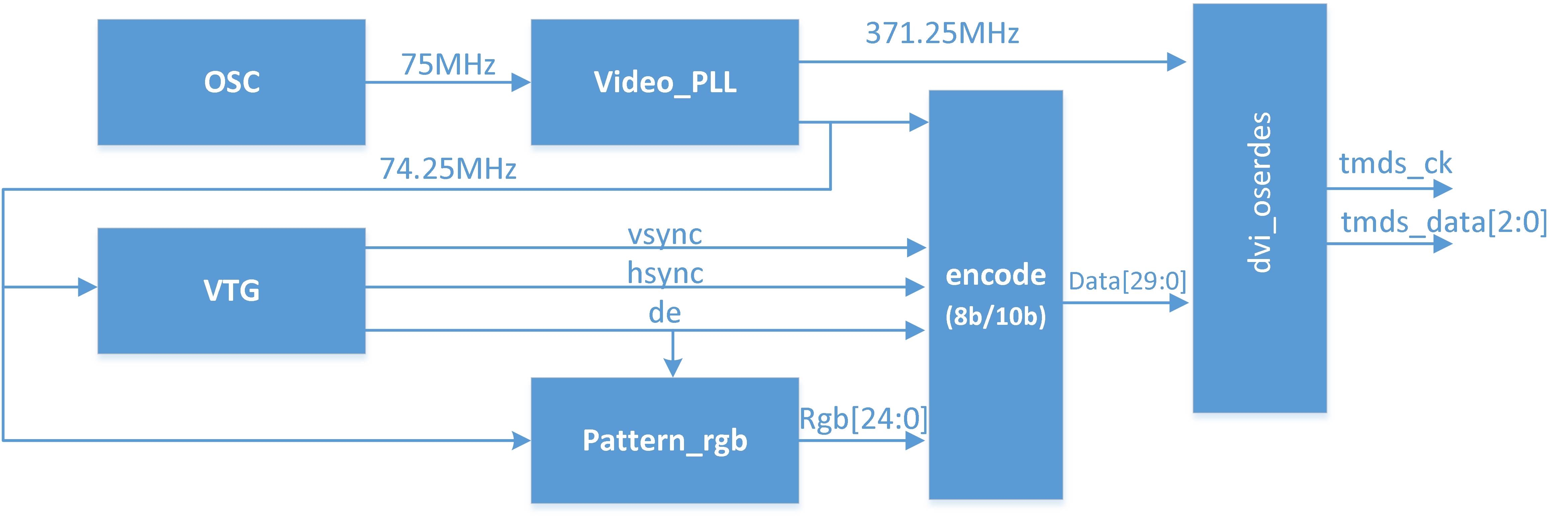

时钟结构如下:使用LIFCL-40片上振荡器产生75MHz基准时钟,再经锁相环产生74.25MHz的视频时钟和371.25MHz的串行化时钟。

RGB视频数据、HSYNC、VSYNC和DE经过8B/10B编码形成30bit的新数据,经1:10串行化后通过3个TMDS通道发送,整体结构如下图所示。

图2 HDMI发送逻辑框图

图2 HDMI发送逻辑框图

3.2 关键内容介绍

3.2.1 并串转换

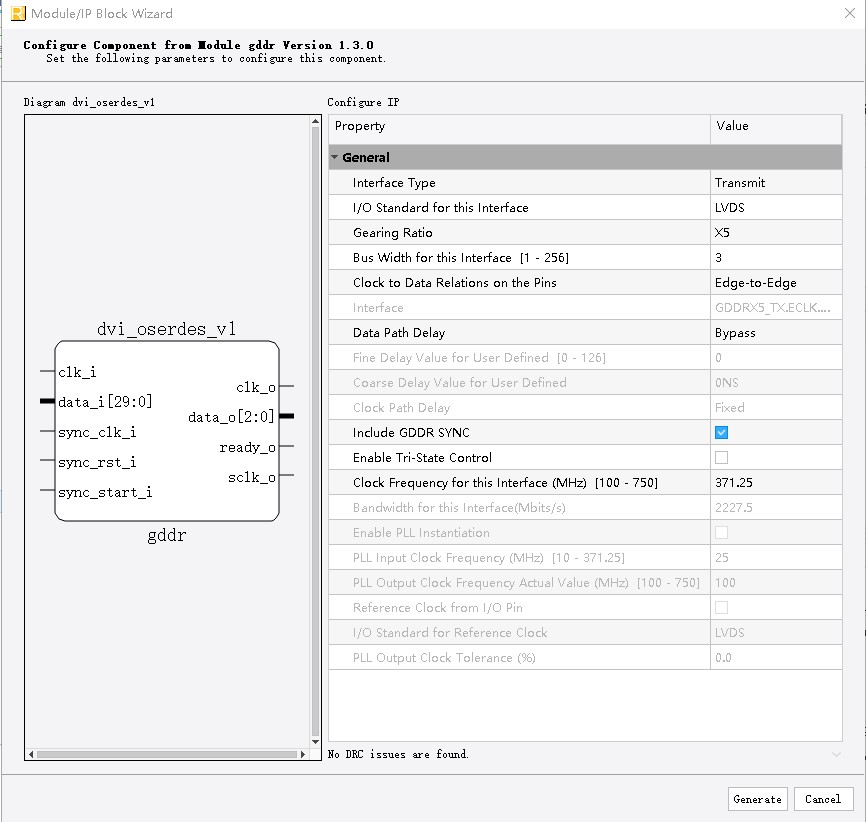

本例主要是使用LIFCL-40的ODDR5x原语实现串并转换,为简化设计,使用原语IP “DDR_Generic”实现,例化属性如下图3所示。

图3 IP例化属性

3.2.2 时序约束

对video pll产生的两路时钟进行周期约束,并将之设置为互不相关。

create_clock -name w_video_clk -period 13.4680134680135 [get_nets w_video_clk]

create_clock -name w_video_clk5x -period 2.69360269360269 [get_nets w_video_clk5x]

set_clock_groups -group [get_clocks w_video_clk] -group [get_clocks w_video_clk5x] –asynchronous

3.2.3 物理约束

需对IO、JTAG和QSPI加载等进行物理约束,详细内容见工程。

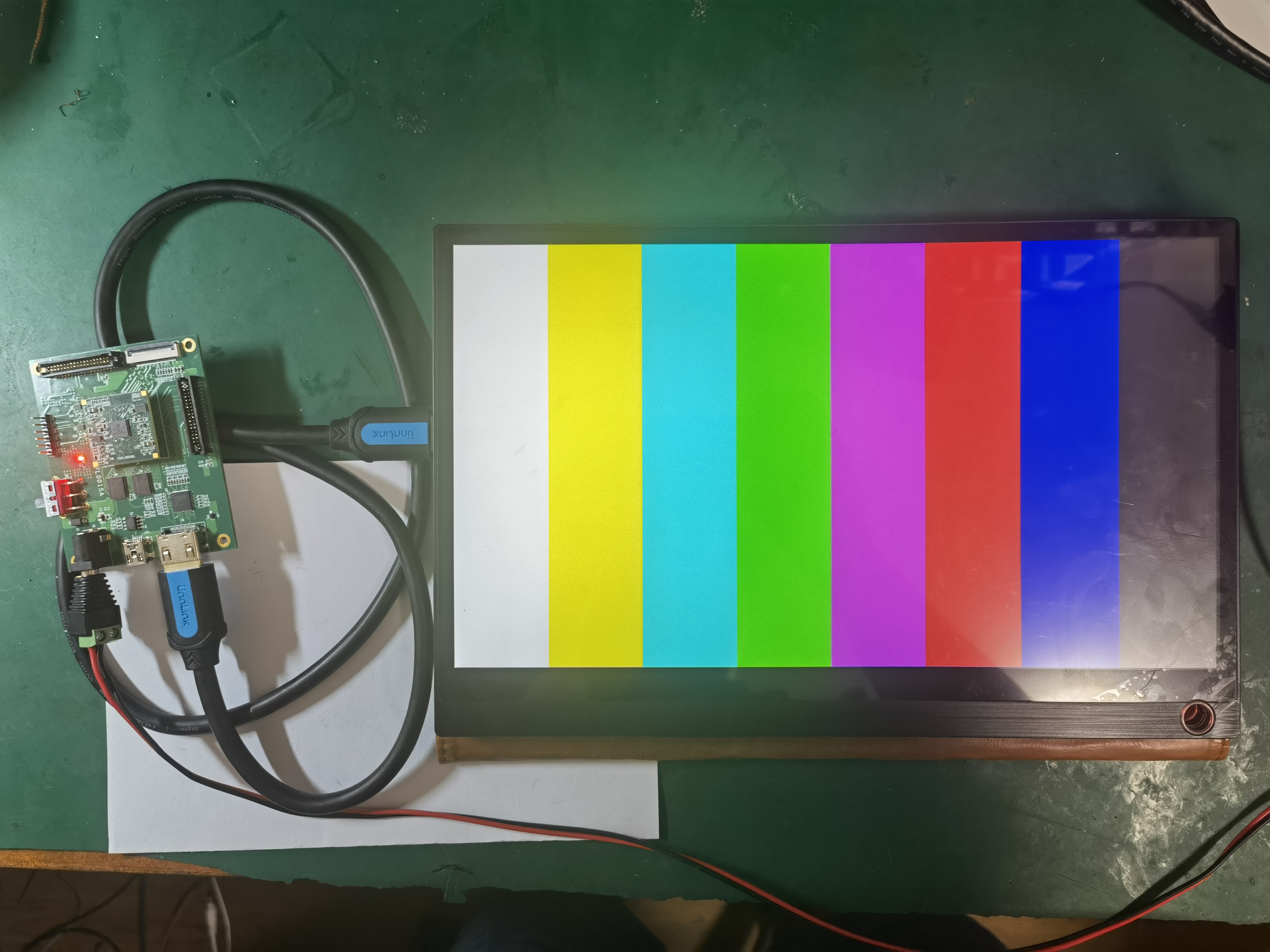

四、效果图

示例程序效果见下图4。

图4 示例效果图

本例分享结束,希望可以为设计带来帮助。最后,欢迎各位技术大牛们扫码加入QQ技术讨论区和关注微信公众号来,以便向各位大牛们学习,提升!

以上是关于Lattice CrosslinkNx LIFCL-40应用连载6:搭建HDMI(DVI)发送系统的主要内容,如果未能解决你的问题,请参考以下文章

Lattice CrossLinkNx LIFCL-40应用连载7:使用HyperRAM存储器

Lattice CrossLinkNx LIFCL-40应用连载7:使用HyperRAM存储器

Lattice CrossLinkNx LIFCL-40应用连载7:使用HyperRAM存储器

Lattice CrosslinkNx LIFCL-40应用连载5:如何使用MIPI D-PHY硬核IP