Lattice CrossLinkNx LIFCL-40应用连载7:使用HyperRAM存储器

Posted _Hello_Panda_

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了Lattice CrossLinkNx LIFCL-40应用连载7:使用HyperRAM存储器相关的知识,希望对你有一定的参考价值。

作者:Hello,Panda

今天熊猫君的技术分享是使用FPGA驱动读写HyperRAM。首先,我们要了解什么是HyperRAM,这种器件出现的时间不太长,是近十年才面世的,一些RAM大厂如Cypress、华邦、ISSI等均有相关产品。它的访问接口类似于NOR Flash,每次访问都是先发命令,再取一个burst的数据,因此它不像SRAM或DRAM那样需要地址、控制和数据线等若干IO,它具有占用引脚少的特点,8bit位宽的片子只需要12个IO,16bit位宽的片子只需要20个IO。HyperRAM的运行速率有166MHz、200MHz和250MHz三个速率等级,双边沿采样,如果是8bit器件的话,那么对应的带宽就可以达到333MB/s、400MB/s和500MB/s,容量从32Mb到512Mb不等。同时,HyperRAM具有低功耗的特点,并且时钟在非访问期间可以关闭,因此适合在穿戴设备、手持设备和部分车载应用等对功耗和体积要求严格且带宽吞吐不是那么特别大的场合使用,国内的FPGA厂商“高云”将HyperRAM集成到了它的“小蜜蜂”系列,一些传统的微控制器厂商也在产品中集成了HyperRAM控制器。

一、HyperRAM访问介绍

熊猫君以自有板子上搭载的华邦W956D8器件为例,详细介绍HyperRAM的访问流程。

华邦W956D8容量为64Mb,工作电压1.8V,8bit数据位宽,工作时钟200MHz(带宽400MB/s),最大突发长度128bytes(64clocks),在200MHz时钟频率工作时,命令插入等待周期最小为7clocks。

HyperRAM的访问分成寄存器访问、读数据、写数据三种来介绍。在器件复位信号释放以后需先对HyperRAM进行初始化。

1.1 HyperRAM命令集

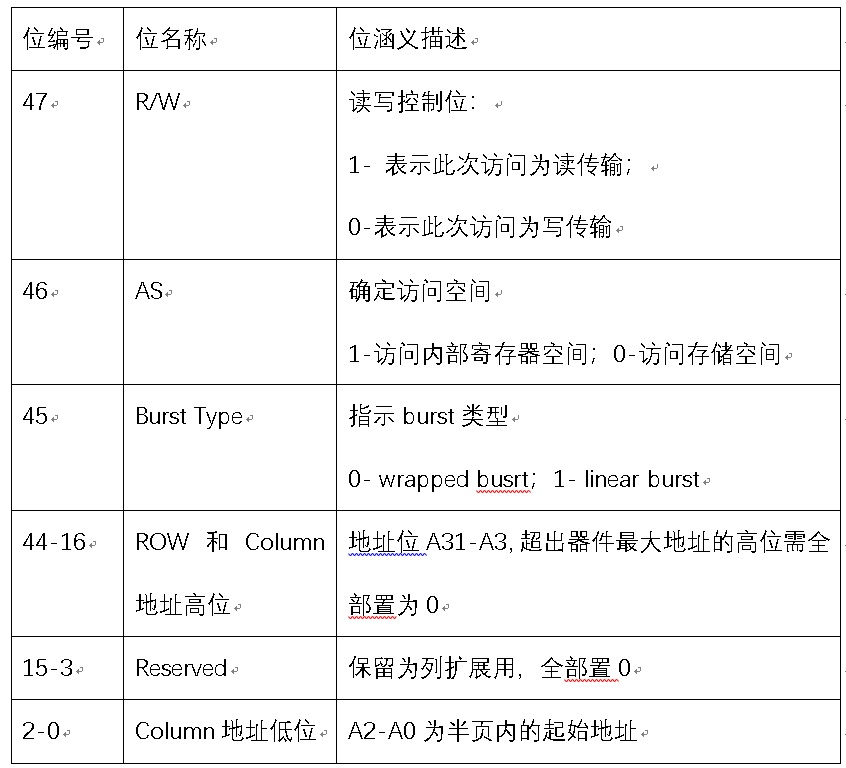

每个HyperRAM访问周期均以命令开始,命令有内部配置寄存器访问和存储空间访问两个大类。命令一共有48个bit,占用3个时钟周期,下表1是命令字的位定义。

表1 命令字定义

1.2 寄存器访问

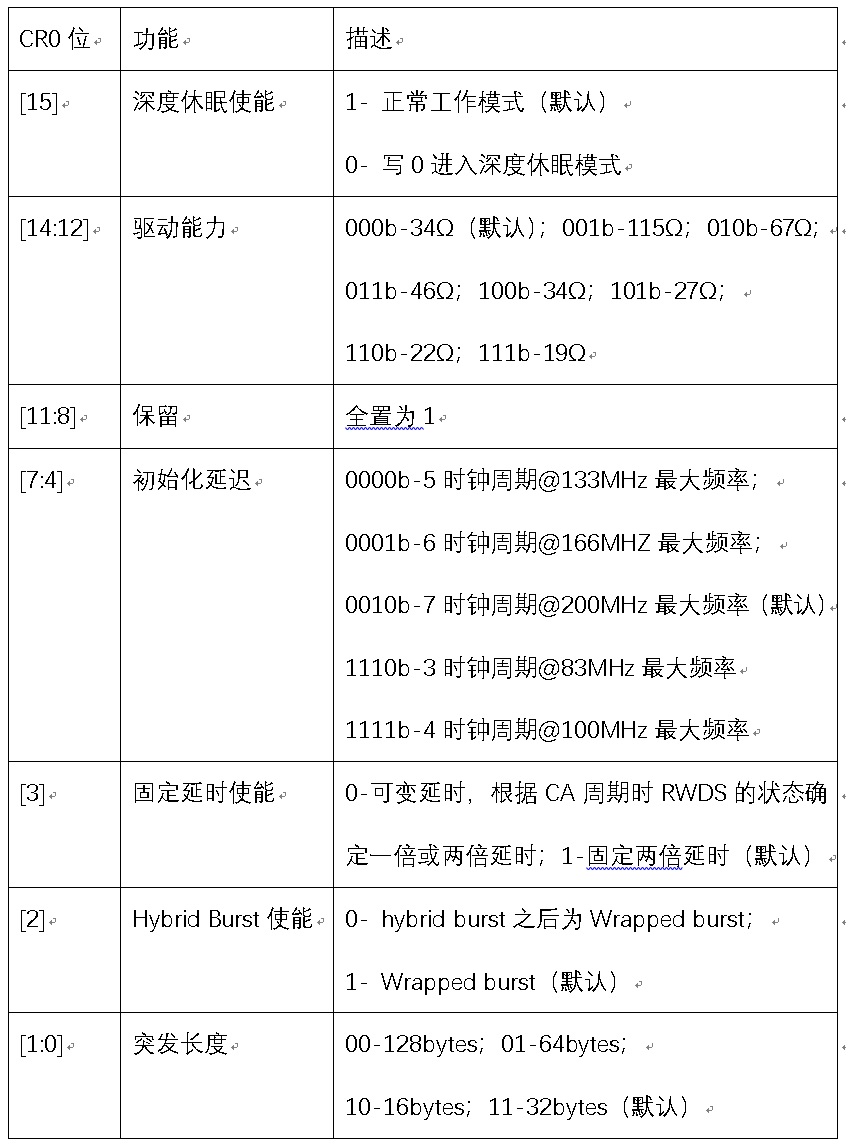

一般的,寄存器访问用于初始化HyperRAM内部寄存器,主要关注的是要正确设置“配置寄存器0”,写该寄存器对应的48bit命令字为16进制60-00-01-00-00-00,下表2为“配置寄存器0”的位定义。

表2 配置寄存器0位定义

在本例中,突发长度设为128bytes,其他为默认值,该寄存器的配置为8F2Ch。

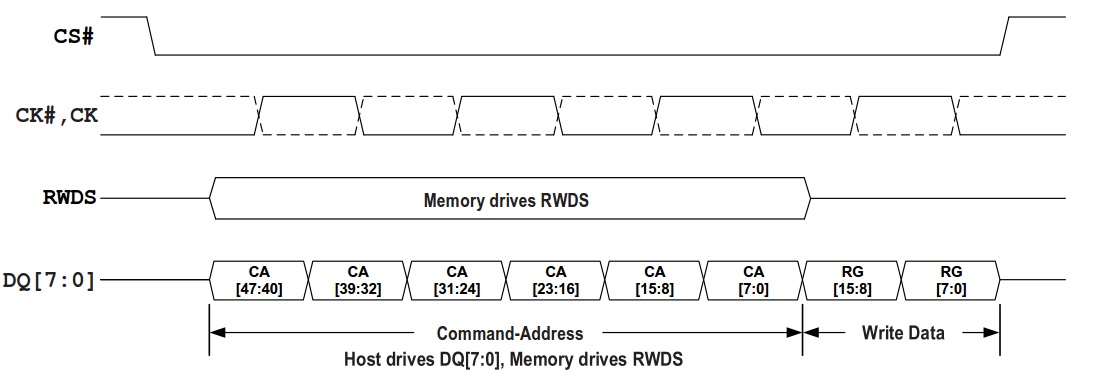

在配置HyperRAM内部寄存器时,寄存器配置值紧跟CA命令字,主控无需驱动RWDS信号,时序如下图1所示。

图1 写寄存器时序图

1.3写数据

写数据的时序如下图2所示:

(1)写数据周期时,需将CS信号拉低;

(2)CA周期时,RWDS信号由HyperRAM驱动,在CA周期结束后,RWDS由主控FPGA驱动;

(3)本例寄存器CR0设置为初始化延时7个时钟周期,固定2倍延时,因此需固定延时14个时钟周期后输出数据;

(4)在数据输出时,RWDS可用作MASK信号,当RWDS为高电平时,对应的数据被屏蔽写入HyperRAM,一般RWDS恒为‘0’,数据全部写入HyperRAM即可。

图2 写数据时序图

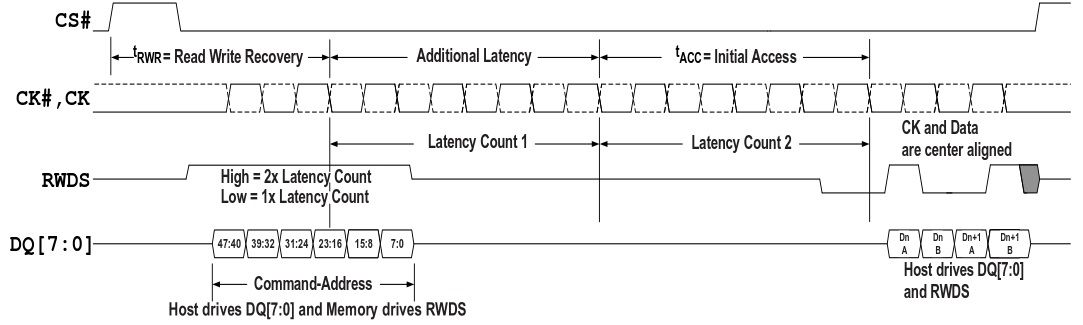

1.4 读数据

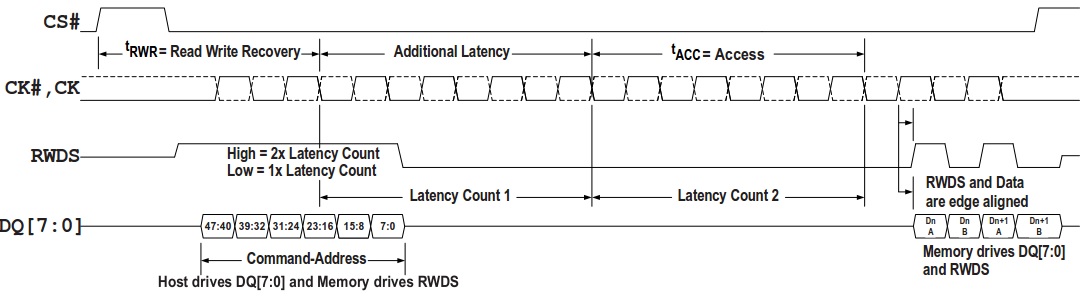

读数据的流程和写数据类似,RWDS全程由HyperRAM驱动,在数据输出时,数据和RWDS的边沿对齐,此时RWDS不具备数据屏蔽功能,仅通过边沿的变化指示数据正在输出,时序图见下图3。

图3 读数据时序图

二、FPGA驱动HyperRAM

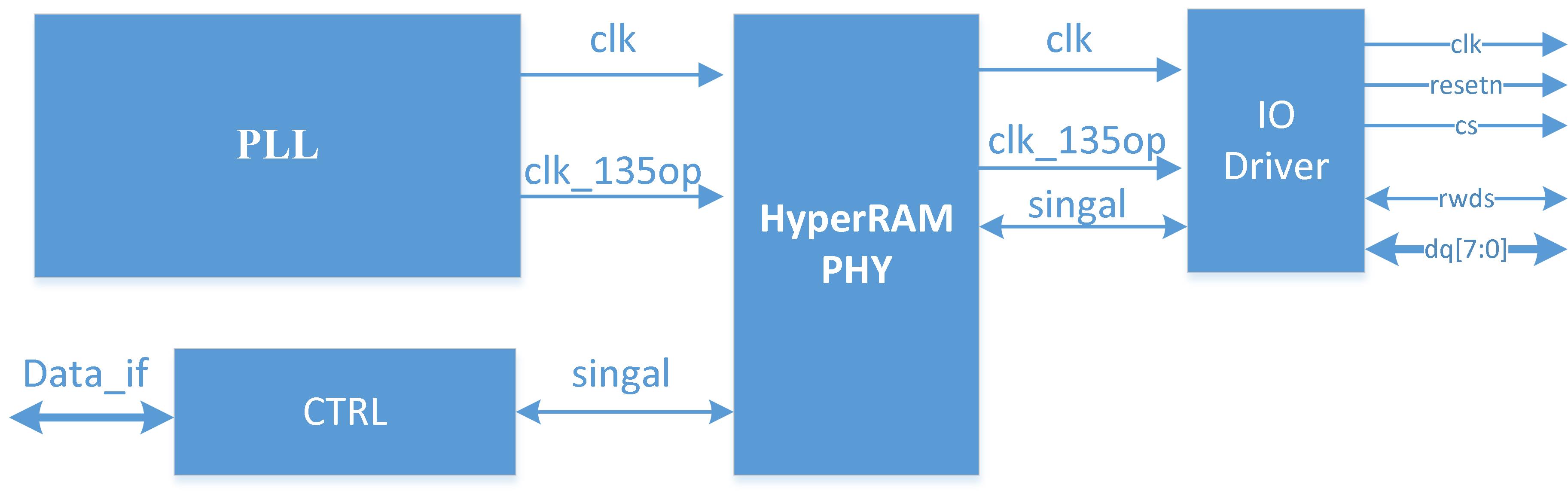

FPGA驱动HyperRAM的整体框图如下图4所示。

图4 整体框图

这个东东比较的简单,就不在文章里面啰嗦碎碎念了,可直接下载代码分析即可。如上图所示:(1)内部时钟采用clk,为保证满足采样相位,输出到HyperRAM的时钟和内部时钟频率相同,相位相差135度;(2)主控检测RWDS的状态,当RWDS为边沿跳变的1-0-1-0…序列时,主控采样RWDS数据。

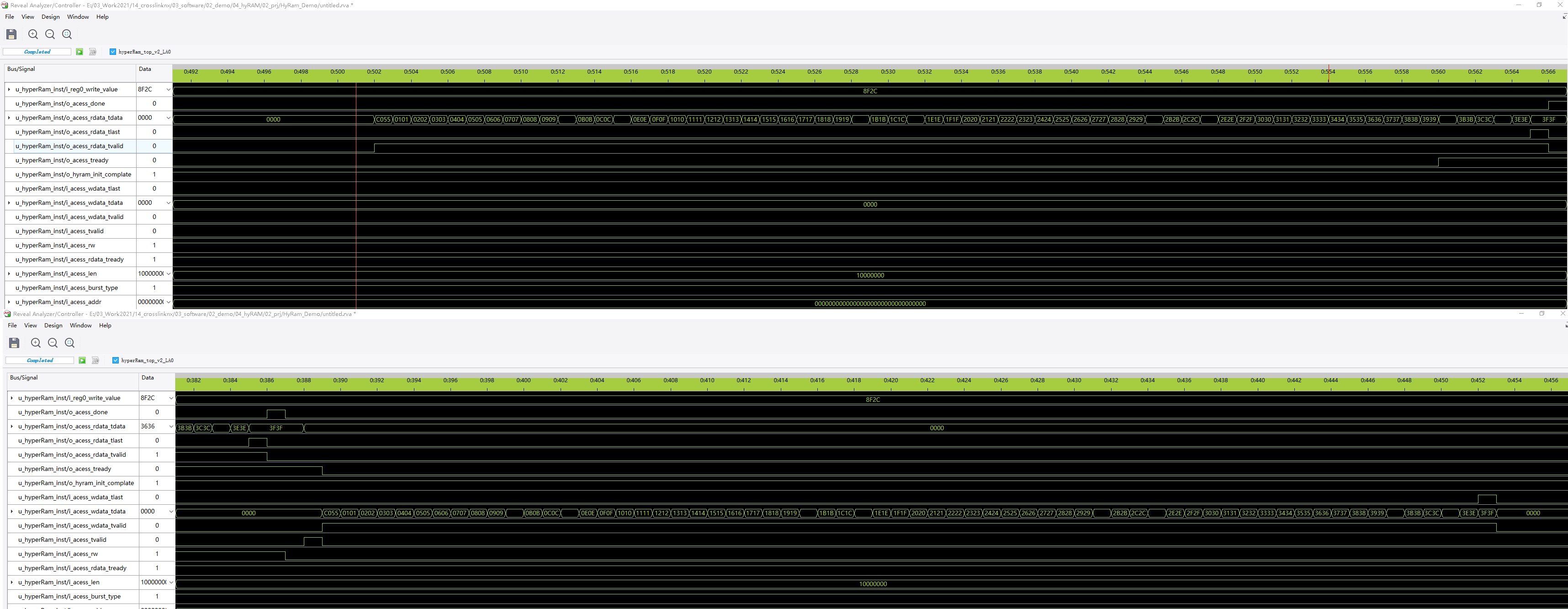

运行Demo功能,在线调试观察写入的数据和读出的数据,完全一致即为满足时序要求,运行结果见下图5。

图5 运行结果

好哒,今天的分享到此结束,通过关注微信公众号,在对话框中回复完整字符串YSPL-LIFCL-APP006即可获取本文对应的完整工程文件。最后,欢迎大家关注微信公众号或QQ讨论群,聊聊技术吹吹水,分享心得,共同进步!

以上是关于Lattice CrossLinkNx LIFCL-40应用连载7:使用HyperRAM存储器的主要内容,如果未能解决你的问题,请参考以下文章