DC-DC BOOST芯片SW管脚加RC电路,芯片概率性烧毁的原因?

Posted 记得诚

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了DC-DC BOOST芯片SW管脚加RC电路,芯片概率性烧毁的原因?相关的知识,希望对你有一定的参考价值。

大家好,我是记得诚。

有个读者在群里发了一个问题,是这样的。

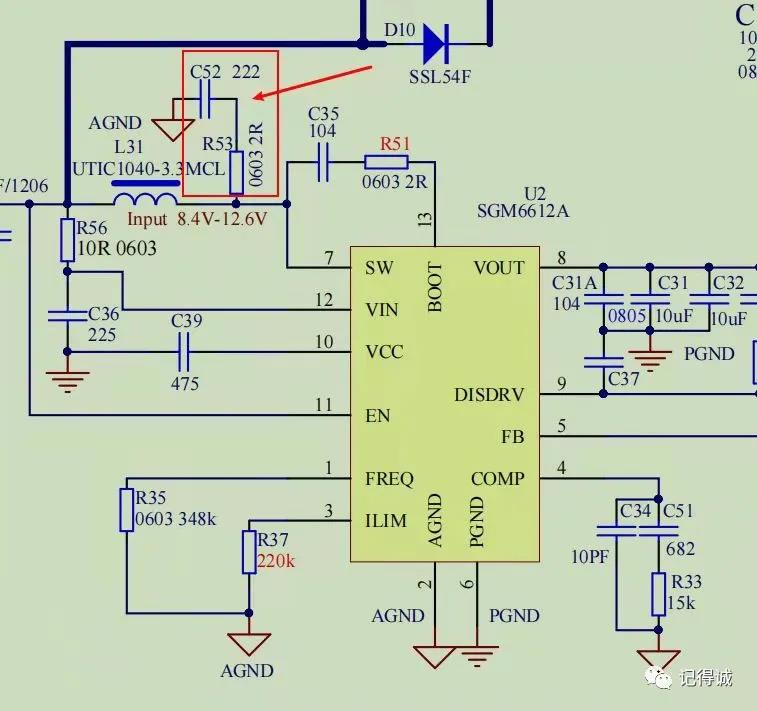

是一个BOOST电路,输入Vin是9~12.6V,VOUT输出是12.8V,在芯片的SW管脚,加R53和C52后,DC-DC概率性的损坏,不加这个RC,试了70块板子没有损坏,基本可以确定是这个导致的,但是是怎么坏的呢?

加C52和R53是为了吸收SW上尖峰的,C35和R51是自举电路,正常一个C35就够了,这地方R51贴的是0R,R51和C35构成RC充电,R越大,DC-DC内部MOSFET开的越慢,SW尖峰小,EMI好一些;R越小,MOSFET开越快,SW上尖峰大,EMI差一些,SW上加RC(C52、R53)是为了吸收这个尖峰。

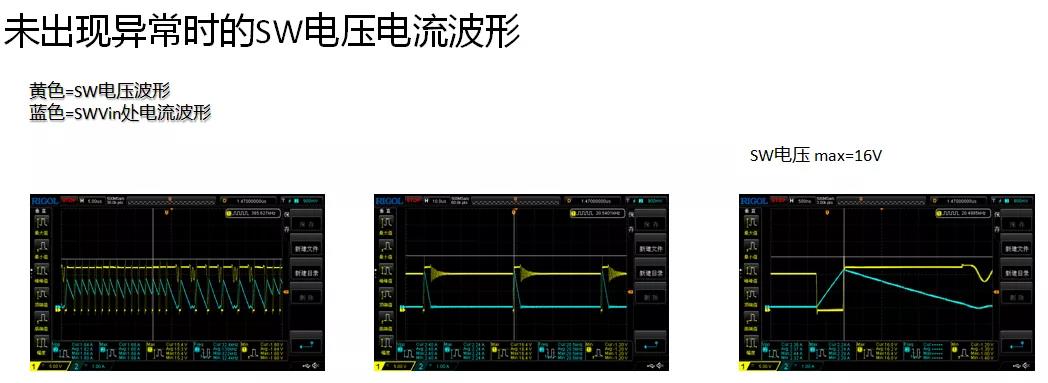

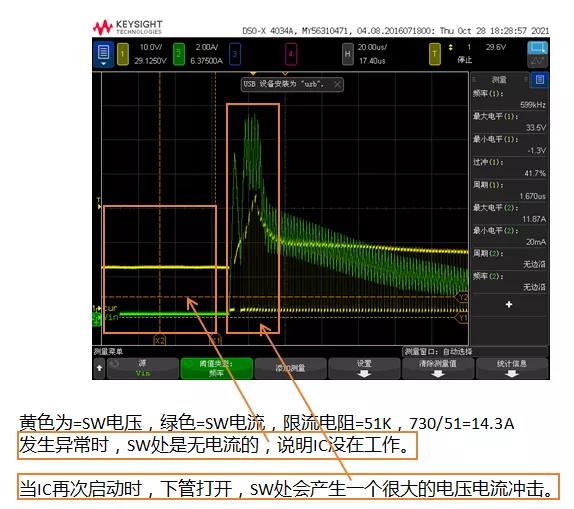

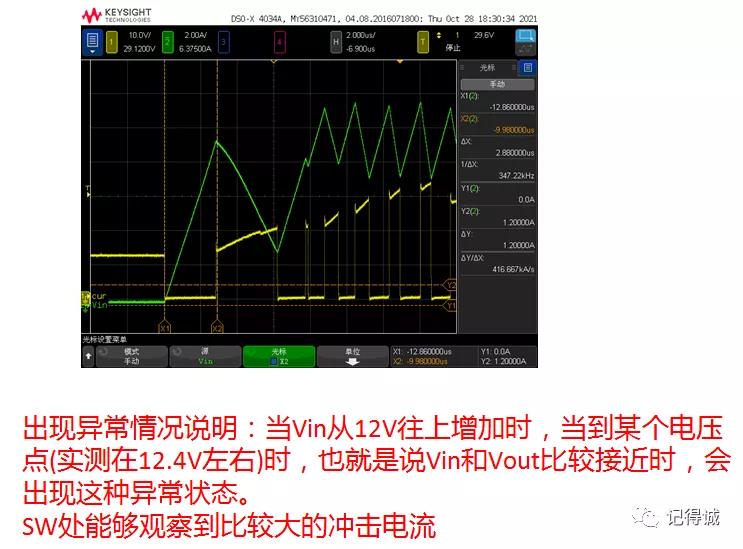

读者测试了SW的电压和电流波形,对比了正常情况下的波形和出现异常时的波形

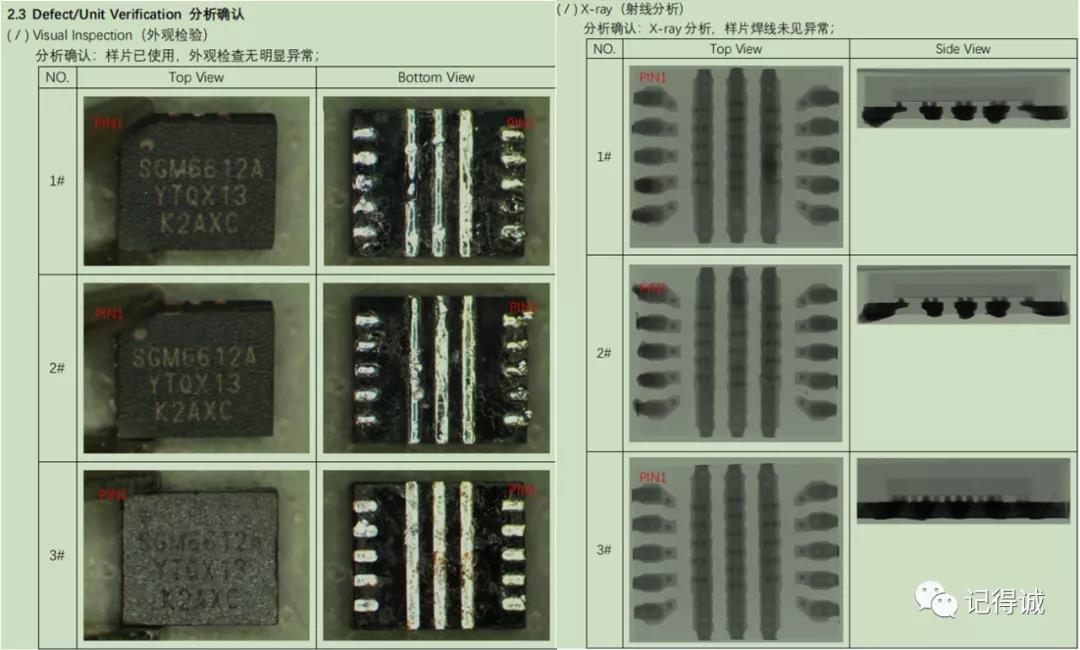

将损坏的芯片寄给原厂做了切片分析,外观检验和X-Ray未发现异常。

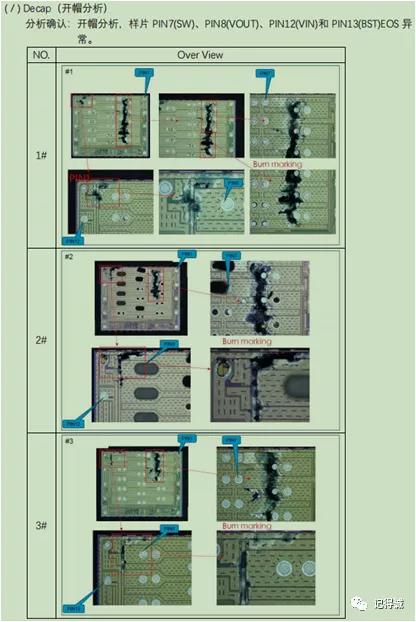

开帽分析,芯片的PIN7(SW)、PIN8(VOUT)、PIN12(VIN)、PIN13(BST) EOS异常。

小伙伴们,怎么看?为什么在SW管脚上加了RC,会出现芯片损坏的情况,欢迎留言区讨论。

以上是关于DC-DC BOOST芯片SW管脚加RC电路,芯片概率性烧毁的原因?的主要内容,如果未能解决你的问题,请参考以下文章