第3章 门电路

Posted 可能自洽

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了第3章 门电路相关的知识,希望对你有一定的参考价值。

第3章 门电路

一、概述

1.门电路及其分类

1.1 门电路

门电路是用以实现逻辑关系的电子电路。

1.2 门电路的分类

(1) 按所采用的半导体器件进行分类

分立元件门电路

集成门电路

双极型集成门(TTL)电路、MOS集成门

(2)按集成度的高低进行分类

SSI小规模集成电路(门电路小于10个)

MSI中规模集成电路(10-100个)

LSI大规模集成电路(100-10000个)

VLSI超大规模集成电路(10000- 100000个)

ULSI甚大规模集成电路(100000个以上)

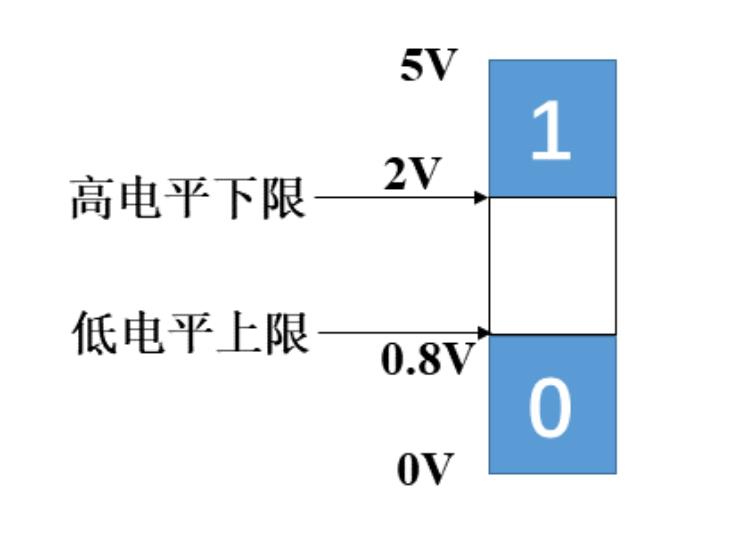

2.逻辑电平

2.1 逻辑电平的概念

逻辑0和逻辑1对应的是电压范围,因此在数字电路中,对电子元件、器件参数精度要求及其电气的稳定度要求比模拟电路要低。

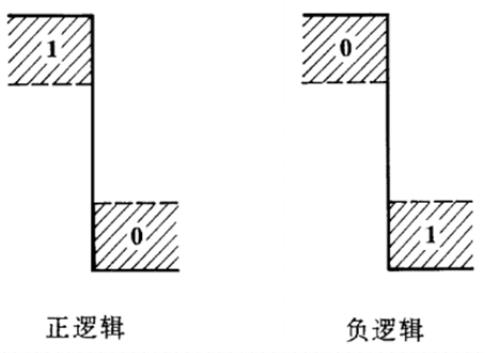

2.2 正逻辑和负逻辑

正逻辑:高电平1低电平0

负逻辑:高电平0低电平1

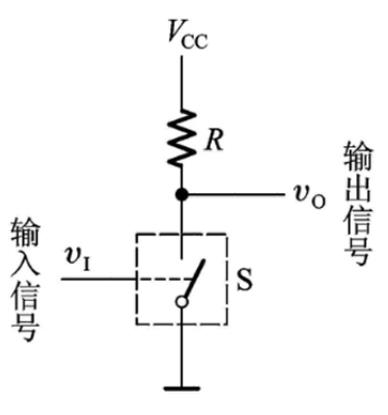

2.3 获得高低电平的方法

V

I

V_{I}

VI控制开关S的通、断情况

S断开,

V

O

V_{O}

VO为高电平

S接通,

V

O

V_{O}

VO为低电平

二、分立元件门电路

1.二极管

二极管具有单向导电性,外加反向电压超过某一数值时,反向电流会突然增大,这种现象称为电击穿。引起电击穿的临界电压称为二极管反向击穿电压。电击穿时二极管失去单向导电性

接正向电压可以导通,反向电压可以看作断开

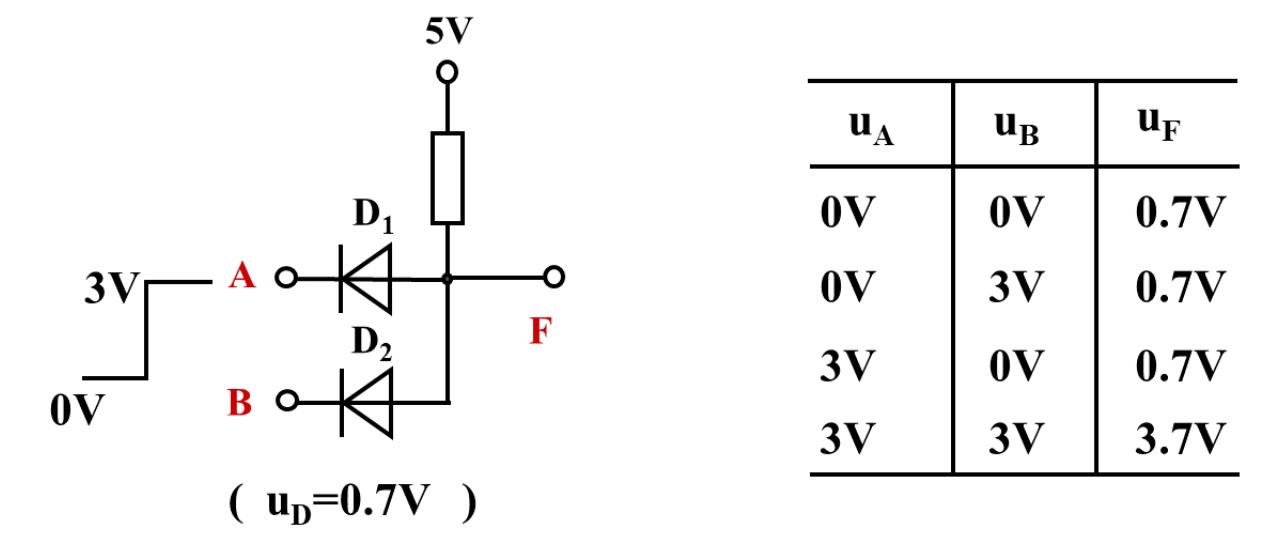

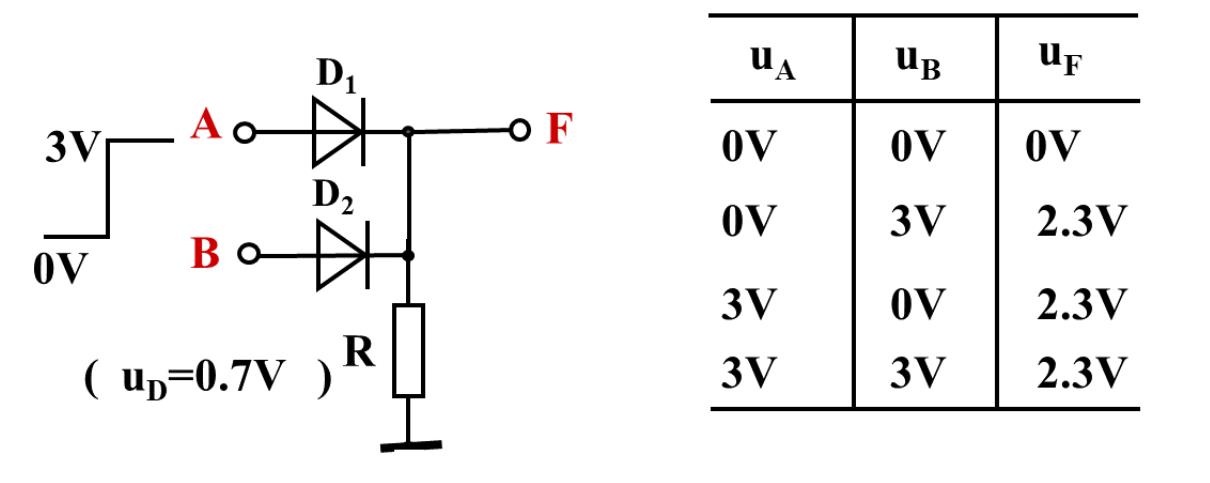

2.与门

逻辑式: F=AB

如图为二极管与门电路,Vcc = 5v,假设3v及以上代表高电平,0.7及以下代表低电平

(1)如果输入端A和B,都输入一个很小的电压。 Vcc远大于它,那么电路导通,Y则输出一个0.7V(相当于二极管的开启电压值)

(2)如果输出端A和B,都输入一个很大的电压假设是 V0 ,但是还是小于Vcc, 那么Y输出电压为(V0+0.7)

3.或门

逻辑式: F=A+B

4.分立元件门电路的缺点

1.电平有偏移

2.带负载能力差(只用于IC内部电路)

三、CMOS门电路(Complementary Metal Oxide Semiconductor(互补金属氧化物半导体))

1.MOS管基本概念

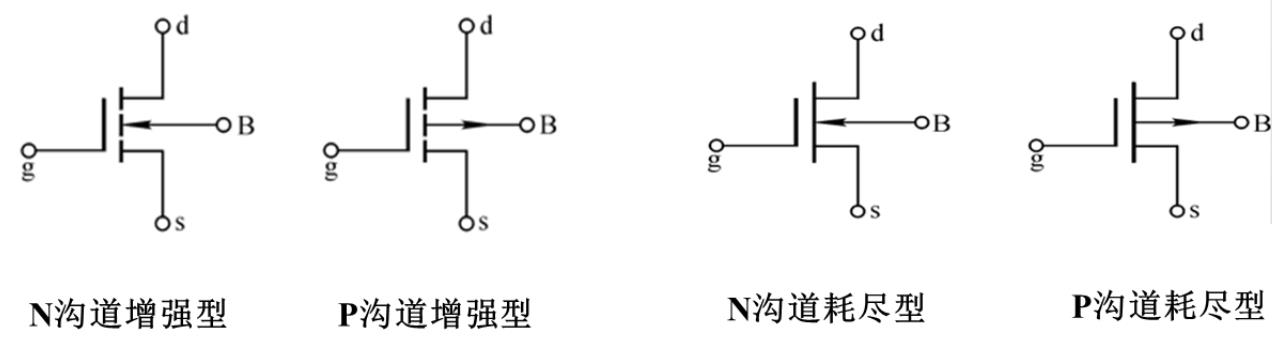

1.1 四类MOS

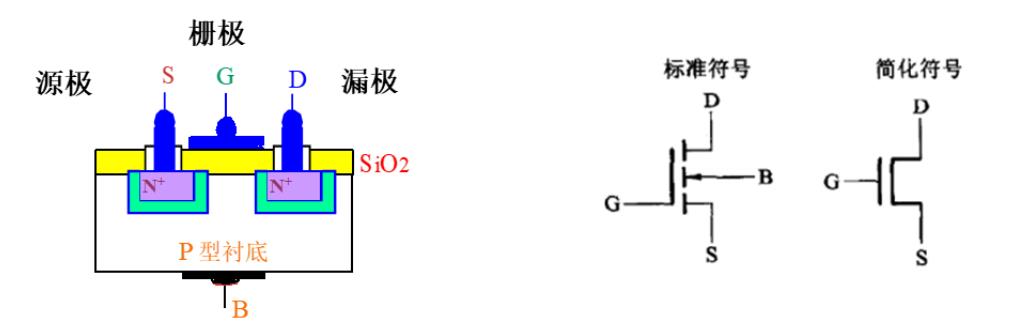

1.2 MOS管的结构一以N沟道增强型为例

取一块P型半导体作为衬底,用B表示。用氧化工艺生成一层

S

i

O

2

SiO_2

SiO2薄膜绝缘层。然后用光刻工艺腐蚀出两个孔。扩散两个高掺杂的N型区。从而形成两个PN结 (绿色部分)。从N型区引出电极,一个是漏极D(Drain, 流入载流子),一个是源极S(Source,流出载流子)。在源极和漏极之间的绝缘层上镀一层金属铝作为栅极G(Grid)。

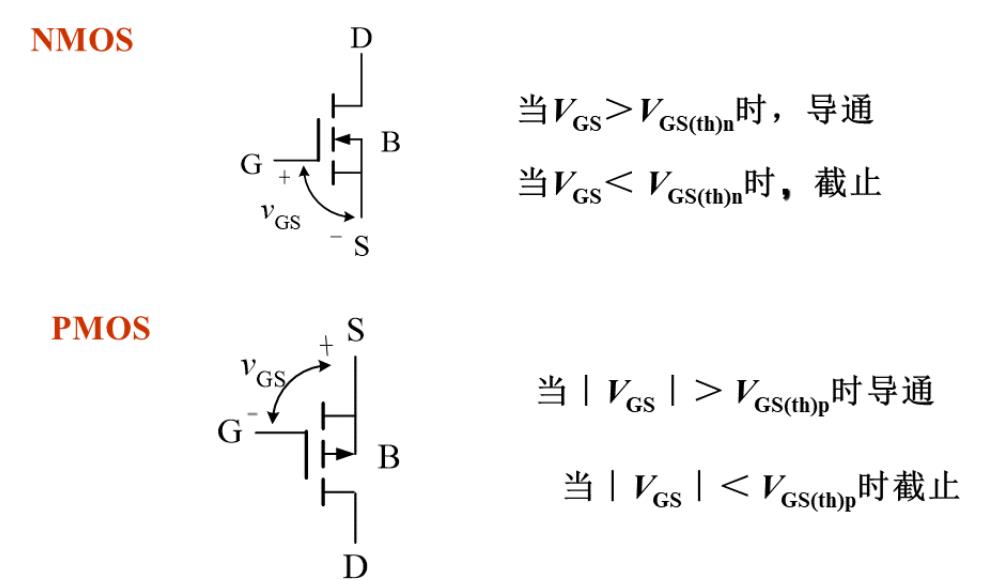

1.3 NMOS管和PMOS管的通断条件

2.CMOS逻辑门

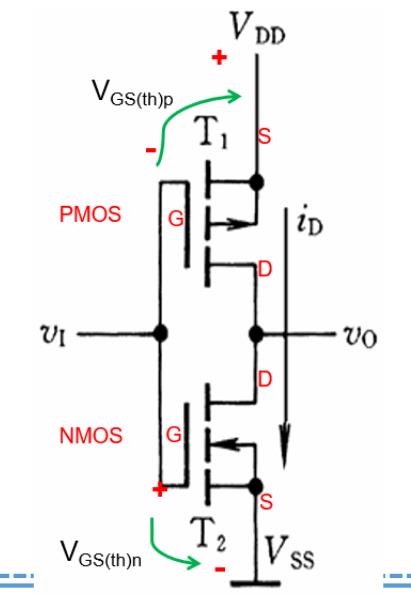

2.1 CMOS反相器

CMOS反相器由一个P沟道增强型MOS管和一个N沟道增强型MOS管串联组成。通常P沟道管作为负载管,N沟道管作为输入管。这种配置可以大幅降低功耗,因为在两种逻辑状态中,两个晶体管中的一个总是截止的。处理速率也能得到很好的提高,因为与NMOS型和PMOS型反相器相比,CMOS反相器的电阻相对较低。

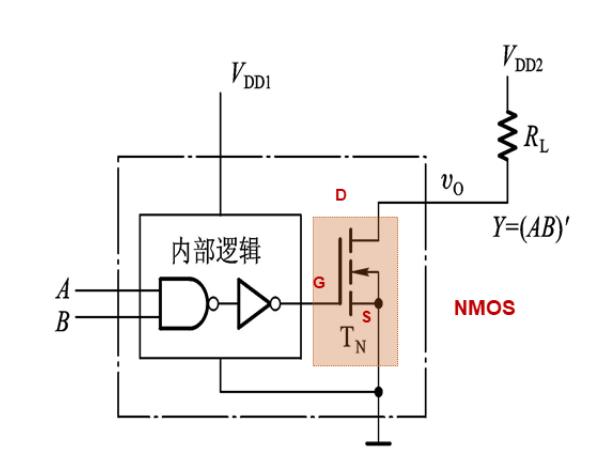

2.2 漏极开路输出门电路(OD门 Open-Drain Output)

OD输出与非门

可以实现“线与”

以上是关于第3章 门电路的主要内容,如果未能解决你的问题,请参考以下文章

2019-2020-20191201《信息安全专业导论》第4周学习总结