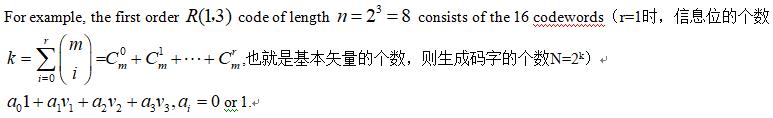

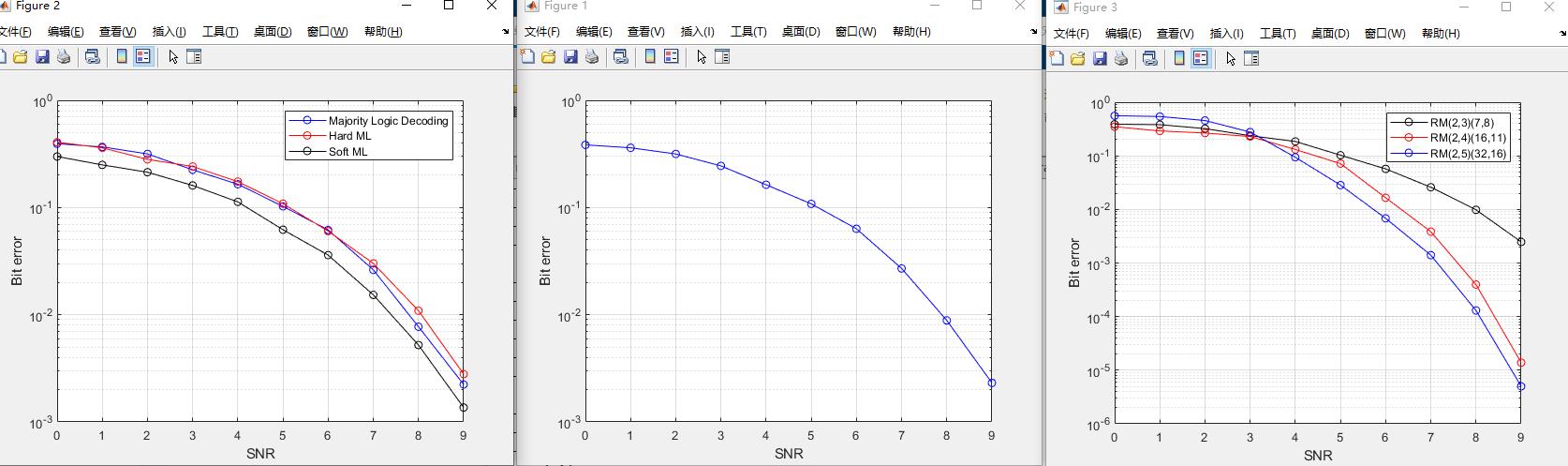

仿真RM码,及在高斯信道下的译码性能,对RM采用大数逻辑译码算法

Posted fpga&matlab

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了仿真RM码,及在高斯信道下的译码性能,对RM采用大数逻辑译码算法相关的知识,希望对你有一定的参考价值。

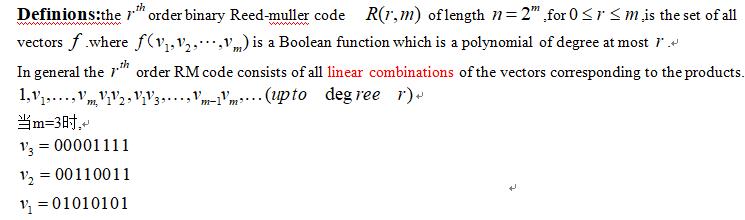

Table.1 the “1” order Reed-muller code of length 8

| Boolean function | codewords |

| 0 | 00000000 |

| 1 | 11111111 |

| V3 | 00001111 |

| V2 | 00110011 |

| V1 | 01010101 |

| V2 +V3 | 00111100 |

| V1+V3 | 01011010 |

| V1+V2 | 01100110 |

| V1+V2+V3 | 01101001 |

| 1+V3 | 11110000 |

| 1+V2 | 11001100 |

| 1+V1 | 10101010 |

| 1+V2+V3 | 11000011 |

| 1+V1+V3 | 10100101 |

| 1+V1+V2 | 10011001 |

| 1+V1+V2+V3 | 10010110 |

A01-96

以上是关于仿真RM码,及在高斯信道下的译码性能,对RM采用大数逻辑译码算法的主要内容,如果未能解决你的问题,请参考以下文章

基于matlab的COFDM调制系统性能仿真,采用DVB-T标准,符号同步,频偏估计,LDPC编译码,信道估计

LDPC-6编码码长对LDPC译码性能的影响分析——以BP译码算法为例进行matlab仿真

量化LDPC基于量化技术的LDPC译码算法的研究与matlab仿真