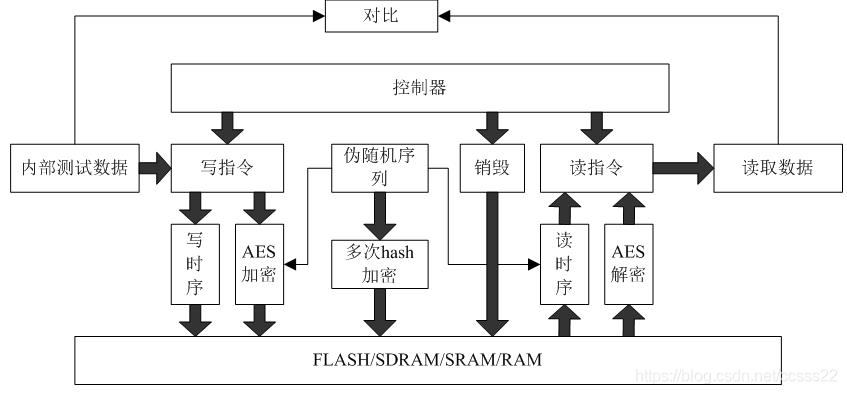

基于FPGA的AES加解密读写控制系统,实现FLASH内部读写内容的销毁功能

Posted fpga&matlab

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了基于FPGA的AES加解密读写控制系统,实现FLASH内部读写内容的销毁功能相关的知识,希望对你有一定的参考价值。

第一,由主控发送写指令,由于每次写入到闪存的时候,必须加密,所以在主控发出写指令的时候,随机序列模块产生伪随机序列作为加密的密钥。同时需要产生对密钥进行加密的mastkey序列。

第二,CBC加密,对于发送的序列(本课题,我们使用的是128位的AES),每128个进行划分,对于每个128个序列,首先和前一128个序列的密文进行异或,然后再通过密钥进行加密,然后再使用mastkey序列将当前的密钥进行加密,从而完成一个CBC加密链。

这里,对于闪存的存储空间做如下的设计:

以上是关于基于FPGA的AES加解密读写控制系统,实现FLASH内部读写内容的销毁功能的主要内容,如果未能解决你的问题,请参考以下文章

基于FPGA的DES加解密系统开发(5000字详细介绍欢迎订阅)