摘抄:一篇文章看看能不能讲透“阻抗匹配”

Posted 熊小仙儿

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了摘抄:一篇文章看看能不能讲透“阻抗匹配”相关的知识,希望对你有一定的参考价值。

一篇文章看看能不能讲透“阻抗匹配”

原文链接:

https://m.toutiao.com/i6794651664956523019/?traffic_source=CS1114&in_ogs=3&utm_source=HW&source=search_tab&utm_medium=wap_search&prevent_activate=1&original_source=3&in_tfs=HW&channel=

大家好,好久不见。最近一直在想新年第一篇文章与大家分享、探讨哪一个知识点,有好几个都感觉不错,但是作为新年的第一篇又都感觉不够格。无意中想到了“阻抗匹配”这个重要又经典的话题,顿时觉得再适合不过。之前聊485总线的时候稍微提及过,今天我们就来深入地分析分析。

先说“阻抗”和“阻抗匹配”的概念

电路中存在的电阻、电容和电感对电流起到的阻碍作用就叫做阻抗。阻抗的单位为欧姆(Ω),用Z来表示,是一个表达式为:Z=R+i(ωL–1/(ωC))的复数。实部R为电阻,虚部(ωL–1/(ωC))为电抗,其中ωL为感抗,1/(ωC)为容抗。

像我们平时接触到的耳机、喇叭,它的一个重要的参数就是阻抗,准确的说是在1KHz的正弦波信号电路中耳机所呈现的阻抗值。主要是电阻和感抗,没有容抗。

拜亚动力DT990Pro 250Ω

阻抗匹配是指信号源、传输线和负载之间达到一种适合的搭配关系,从而提升能源效益。

低频电路中的阻抗匹配

在直流电路中也就是理想化的纯电阻电路中,由电容和电感引起的电抗基本可以忽略不计,此时电路中的阻抗主要是来自于电阻。

如下图示,我们假设激励源已定,那么负载的功率由两者的阻抗匹配度决定。电路中的电流I=U/(r+R),负载的功率P=I²R,我们整理得到P=(U²*R)/(r+R)²,可以看出当R=r时负载的功率P最大=U²/4R。

纯电阻电路模型

此结论在交流电路中引入容抗和感抗以后会稍有不同,在交流电路中负载的阻抗与信号源的阻抗共轭的时候能够实现最大功率输出。

在低频电路中,我们一般不考虑传输线的匹配问题,只考虑信号源跟负载之间的阻抗匹配,因为低频信号的波长相对于传输线来说很长,传输线可以看成是“短线”,反射可以不考虑,因为即使反射回来,跟原信号也是一样的。

高频电路中的阻抗匹配

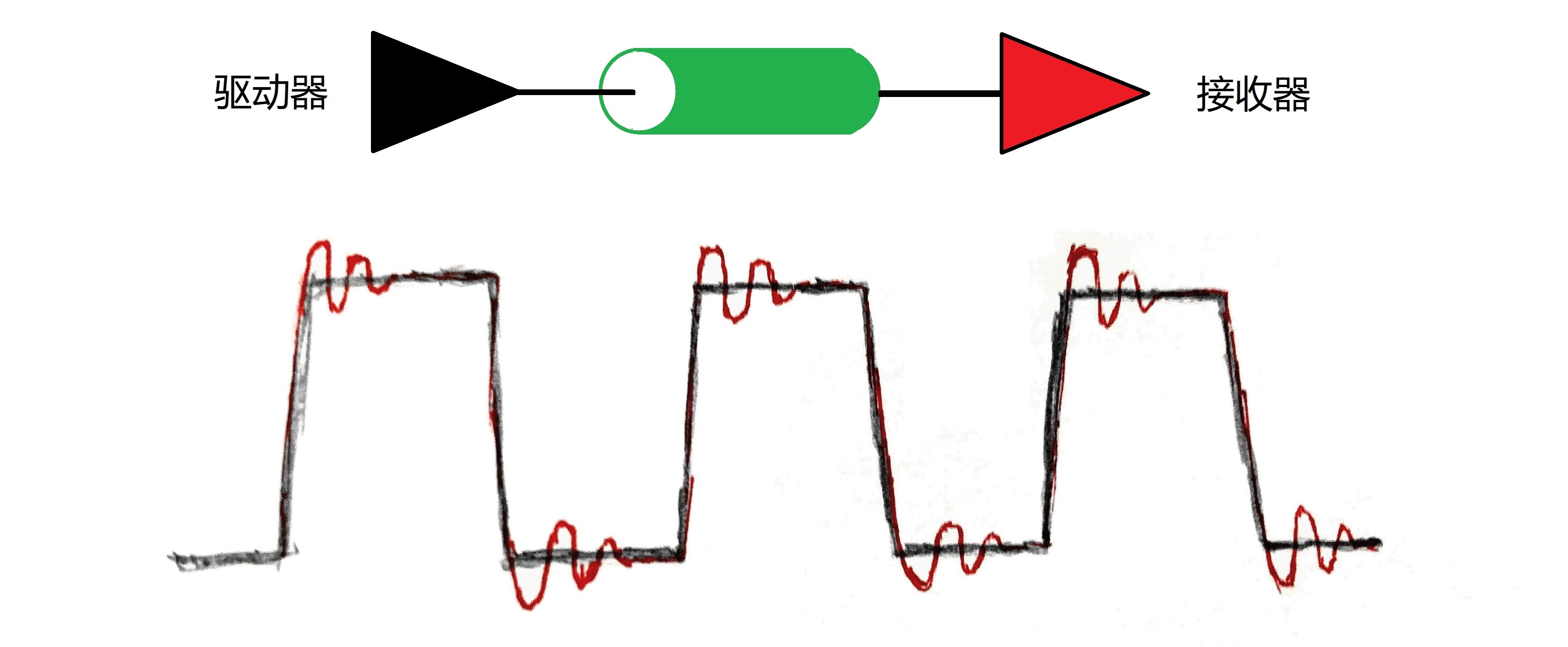

我为什么把高频电路单拉一个段落?因为在高频电路中引入了一个非常重要的因素—反射信号。我们知道当信号频率很高时,则信号的波长就很短。当波长和传输线长度同一量级时,反射信号叠加在原信号上将会改变原信号的形状。但是如果传输线的特征阻抗与负载阻抗相等(即阻抗匹配)时,就会有效的减少、消除高频信号反射。

信号传输波形

至于为什么阻抗不匹配会产生反射以及传输线的特征阻抗的算法,涉及到二阶偏微分方程的求解,在这里我就不细说了,有兴趣的朋友可以看一下高等教育出版社的教材《电磁场与电磁波》第四版的第七章<导型电磁波>的第6小结<传输线>,里面有详细描述。

上面我们提到的传输线特征阻抗是一个很重要的概念,其数值只由传输线的结构和材料决定,与线的长度以及信号的频率、幅值等无关。一些射频设备所使用的同轴电缆的特征阻抗为50Ω,闭路电视的同轴线缆一般为75Ω。

如果阻抗不匹配那么不良后果有哪些呢?换句话说就是形成反射的不良后果,主要是会降低能量传输效率,形成驻波,导致传输线的有效功率容量降低。如果是射频设备的话就会影响信号传输距离、信号质量,甚至会损坏发射设备。如果是电路板上的高速信号线与负载阻抗不匹配时,就有可能产生震荡、辐射干扰等。

阻抗匹配的应用场景

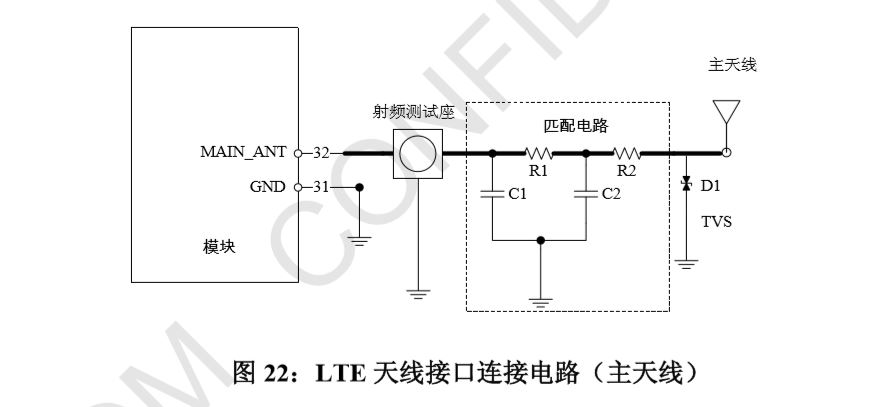

射频天线部分的设计,这块的要点在于天线和馈线间的阻抗匹配。发射信号时应使发射天线与馈线的特性阻抗相等,以获得最好的信号增益。接收信号时天线与负载应做共轭匹配,接收机(负载)阻抗一般认为只有实数部分,因此需要用匹配网络来除去天线的电抗部分并使它们的电阻部分相等。下图为simcom公司的NB-IOT模块天线部分的datasheet,使用网络分析仪测量阻抗以确定R1、R2、 C1、C2的取值,完成阻抗匹配,可达到射频最佳工作状态。

天线部分匹配电路

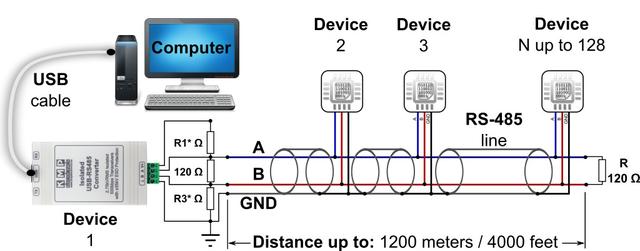

终端匹配电阻,在我们之前有一篇讲485的文章中有详细介绍,没看过的小伙伴可以去阅读一下,相信再结合本文会有一个更加深入的认知。双绞线的特性阻抗一般为120Ω,若不加终端的电阻,当线缆长度很长而传输速率高即信号频率高的时候就很容易发生我们上面所说的信号反射了。

485通讯模型

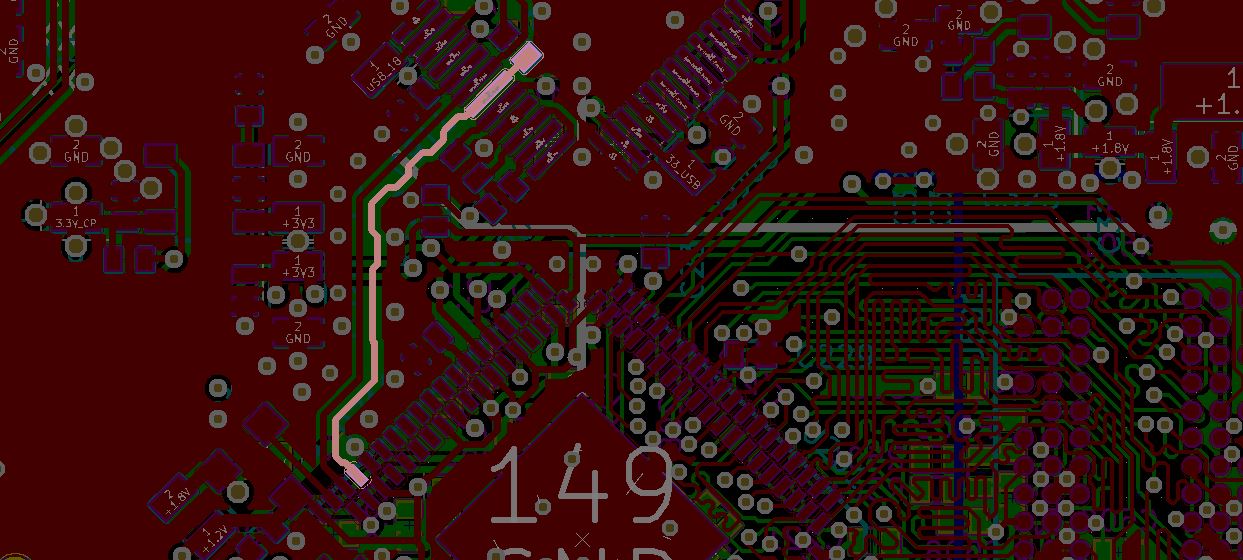

PCB布线在低频电路应用中基本可以不考虑阻抗匹配,但是在高频电路中PCB走线的阻抗就需要重视了,一般在数字信号的边沿时间小于1ns或模拟信号的频率超过300MHz的时候我们就需要考虑走线的阻抗问题。PCB走线阻抗主要来自寄生的电容、电阻、电感系数,主要因素有板厚、线宽、铜皮厚乃至过孔直径等。PCB阻抗的范围是 25 至120 欧姆,USB、HDMI、SATA等一般要做85~100Ω的阻抗控制。(下图为之前设计的一款linux小主机的USB数据走线)

linux主板布线

总结

这篇文章到这里就要结束了,希望大家通过我的这篇文章能对“阻抗匹配”这个重要的知识点有更进一步的了解。如果大家有更深入的认知欢迎在下方评论区留言分享,让我们能借助这个平台一起学习一起进步。

还是老套路,介绍一下接下来的开源计划,之前承诺的音响功放暂时放一下,在它之前我插入了一个耳放,几天后推出。还是用的TI的TPA6120A2,这回我对之前的那款进行了深入优化,同时选了一个更合适的壳体(之前那款壳体停产买不到了),这次我尽量整理出BOM,这样感兴趣的小伙伴做起来就更方便了

以上是关于摘抄:一篇文章看看能不能讲透“阻抗匹配”的主要内容,如果未能解决你的问题,请参考以下文章