USB IP核FPGA调试

Posted yuanyun_elber

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了USB IP核FPGA调试相关的知识,希望对你有一定的参考价值。

synopsys的usb dwc3 ip核调试已经开始一周多了,之前已经先行调通jlink和串口等常规调试手段,我们目前usb作为device端的软件已经准备好了,上周本来准备插上pc就能愉快地枚举跑起来,但是好事多磨,连get descriptor的第一个transfer都没跑完。

从软件打印来看,这个transfer中第一个transaction,也就是setup包data packe收的是对的,但是第二个transaction,因为是我们发数据,就开始出现不正常了。

工欲善其事必先利其器,后来我们就在等待usb分析仪的路上,从周一等到周三,周三又拖到周五,好不容易今天等到了usb分析仪,发现北京寄过来的usb分析仪根本就不对,(是一个usb接口的逻辑分析仪),果断向老同事求助借到了usb分析仪。

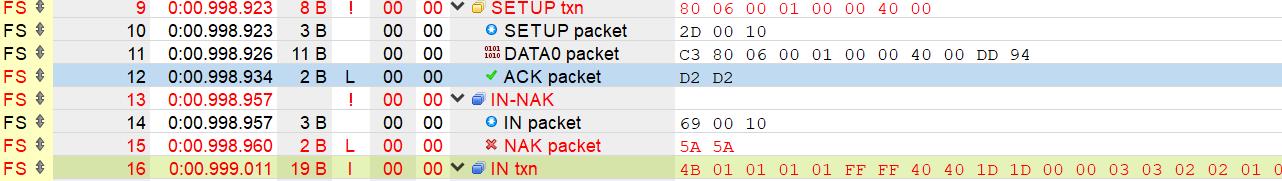

抓取usb分析仪数据发现(拓扑结构是fpga作为usb device接到pc上,中间串一个usb分析仪),我们发送的数据都多了一个字节,下图中的ack packet和nack packet以及in的数据都是两个两个出现的

尽管两个字节的ack电脑有时候也认,后续in包的token电脑也会发出来,但是我们出来的in数据不对,所以这个交互是失败的。而且有的时候,电脑连in包的token(0x69)都没发出来。

数字的同事拉UTMI信号线发现,txready和txvalid的确异常,txready比正常多了一个cycle

复习一下usb的数据包格式相关知识点:

我们的usb分析仪界面不算清楚,找了一张网上的图:

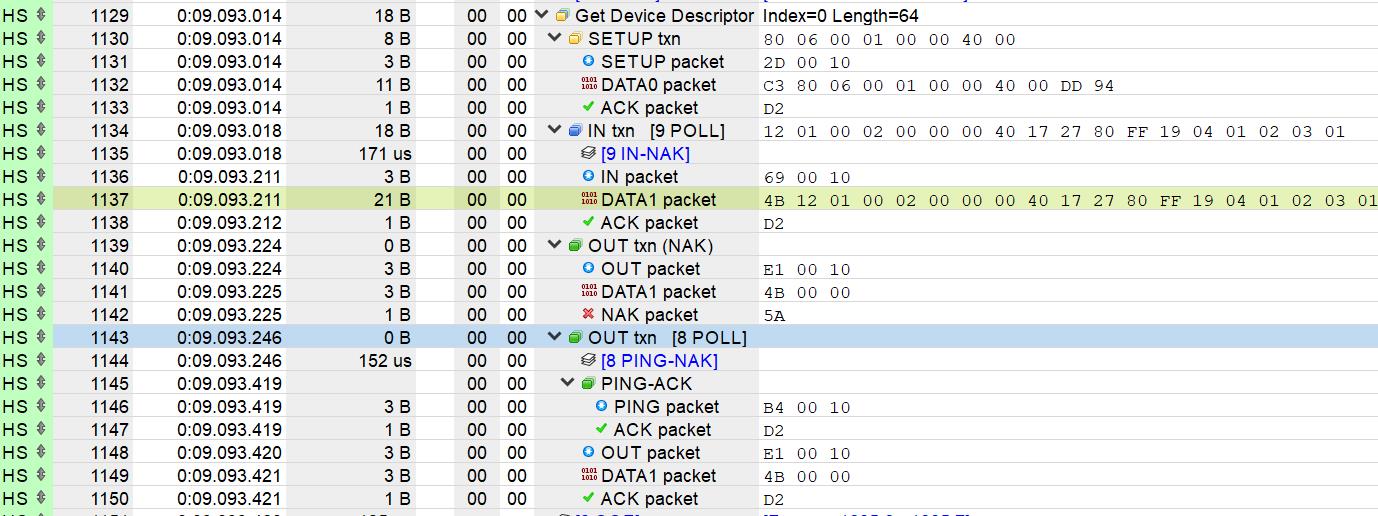

usb的transfer、transaction、packet等比较搞的概念看这张图基本就清楚了,是transfer>transaction>packet的层次结构,一个控制transfer包含2个或3个transaction,也就是setup、data、handshake(软件代码里叫做status)这三个阶段,handshake的方向和data方向必须相反。所谓的3stage就是这个意思,正是因为3段式通信太繁琐了,在usb3.0中,3段式通信被简化成了2段式。一个transaction又会包含若干个packet,上图是比较理想的状况,实际的packet数会比这个更多一点——

以我们抓包的get descriptor这个transfer为例,get descritpor的data in transcation多了9个nack packet,而status 阶段更多,多了PING包、nack包等很多包。

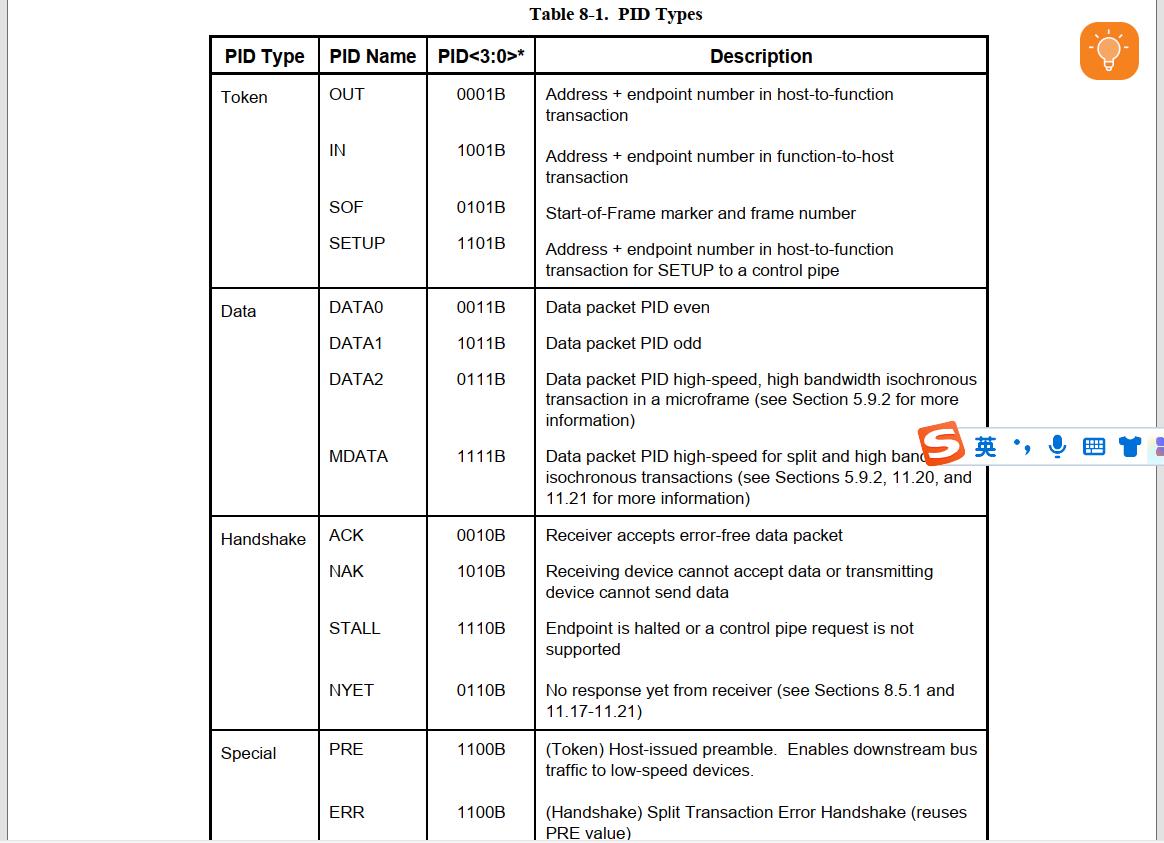

附usb的pid格式

以上是关于USB IP核FPGA调试的主要内容,如果未能解决你的问题,请参考以下文章