基于FPGA的波束形成verilog开发

Posted fpga和matlab

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了基于FPGA的波束形成verilog开发相关的知识,希望对你有一定的参考价值。

目录

一、理论基础

根据原理可知,整个波束形成的基本结构框图如下图所示:

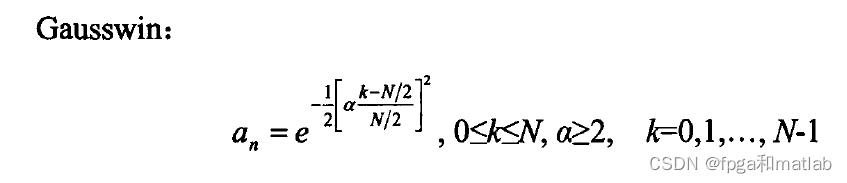

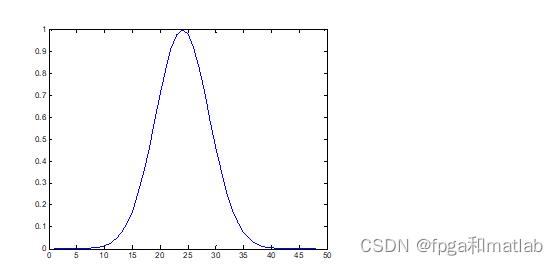

这里,我们使用的加权函数为:

这个模块,相当于上述结构的:

二、核心程序

`timescale 1ns / 1ps

module beamformer(

i_clk,

i_rst,

i_din00,i_din01,i_din02,i_din03,i_din04,i_din05,i_din06,i_din07,

i_din08,i_din09,i_din10,i_din11,i_din12,i_din13,i_din14,i_din15,

i_din16,i_din17,i_din18,i_din19,i_din20,i_din21,i_din22,i_din23,

i_din24,i_din25,i_din26,i_din27,i_din28,i_din29,i_din30,i_din31,

i_din32,i_din33,i_din34,i_din35,i_din36,i_din37,i_din38,i_din39,

i_din40,i_din41,i_din42,i_din43,i_din44,i_din45,i_din46,i_din47,

o_dut

);

input i_clk;

input i_rst;

input signed[7:0]i_din00,i_din01,i_din02,i_din03,i_din04,i_din05,i_din06,i_din07,

i_din08,i_din09,i_din10,i_din11,i_din12,i_din13,i_din14,i_din15,

i_din16,i_din17,i_din18,i_din19,i_din20,i_din21,i_din22,i_din23,

i_din24,i_din25,i_din26,i_din27,i_din28,i_din29,i_din30,i_din31,

i_din32,i_din33,i_din34,i_din35,i_din36,i_din37,i_din38,i_din39,

i_din40,i_din41,i_din42,i_din43,i_din44,i_din45,i_din46,i_din47;

output signed[21:0]o_dut;

wire[7:0]r_dut00,r_dut01,r_dut02,r_dut03,r_dut04,r_dut05,r_dut06,r_dut07;

wire[7:0]r_dut08,r_dut09,r_dut10,r_dut11,r_dut12,r_dut13,r_dut14,r_dut15;

wire[7:0]r_dut16,r_dut17,r_dut18,r_dut19,r_dut20,r_dut21,r_dut22,r_dut23;

wire[7:0]r_dut24,r_dut25,r_dut26,r_dut27,r_dut28,r_dut29,r_dut30,r_dut31;

wire[7:0]r_dut32,r_dut33,r_dut34,r_dut35,r_dut36,r_dut37,r_dut38,r_dut39;

wire[7:0]r_dut40,r_dut41,r_dut42,r_dut43,r_dut44,r_dut45,r_dut46,r_dut47;

delays_tao delays_tao_u(

.i_clk (i_clk),

.i_rst (i_rst),

.i_din00(i_din00),

.i_din01(i_din01),

.i_din02(i_din02),

.i_din03(i_din03),

.i_din04(i_din04),

.i_din05(i_din05),

.i_din06(i_din06),

.i_din07(i_din07),

.i_din08(i_din08),

.i_din09(i_din09),

.i_din10(i_din10),

.i_din11(i_din11),

.i_din12(i_din12),

.i_din13(i_din13),

.i_din14(i_din14),

.i_din15(i_din15),

.i_din16(i_din16),

.i_din17(i_din17),

.i_din18(i_din18),

.i_din19(i_din19),

.i_din20(i_din20),

.i_din21(i_din21),

.i_din22(i_din22),

.i_din23(i_din23),

.i_din24(i_din24),

.i_din25(i_din25),

.i_din26(i_din26),

.i_din27(i_din27),

.i_din28(i_din28),

.i_din29(i_din29),

.i_din30(i_din30),

.i_din31(i_din31),

.i_din32(i_din32),

.i_din33(i_din33),

.i_din34(i_din34),

.i_din35(i_din35),

.i_din36(i_din36),

.i_din37(i_din37),

.i_din38(i_din38),

.i_din39(i_din39),

.i_din40(i_din40),

.i_din41(i_din41),

.i_din42(i_din42),

.i_din43(i_din43),

.i_din44(i_din44),

.i_din45(i_din45),

.i_din46(i_din46),

.i_din47(i_din47),

.o_dut00(r_dut00),

.o_dut01(r_dut01),

.o_dut02(r_dut02),

.o_dut03(r_dut03),

.o_dut04(r_dut04),

.o_dut05(r_dut05),

.o_dut06(r_dut06),

.o_dut07(r_dut07),

.o_dut08(r_dut08),

.o_dut09(r_dut09),

.o_dut10(r_dut10),

.o_dut11(r_dut11),

.o_dut12(r_dut12),

.o_dut13(r_dut13),

.o_dut14(r_dut14),

.o_dut15(r_dut15),

.o_dut16(r_dut16),

.o_dut17(r_dut17),

.o_dut18(r_dut18),

.o_dut19(r_dut19),

.o_dut20(r_dut20),

.o_dut21(r_dut21),

.o_dut22(r_dut22),

.o_dut23(r_dut23),

.o_dut24(r_dut24),

.o_dut25(r_dut25),

.o_dut26(r_dut26),

.o_dut27(r_dut27),

.o_dut28(r_dut28),

.o_dut29(r_dut29),

.o_dut30(r_dut30),

.o_dut31(r_dut31),

.o_dut32(r_dut32),

.o_dut33(r_dut33),

.o_dut34(r_dut34),

.o_dut35(r_dut35),

.o_dut36(r_dut36),

.o_dut37(r_dut37),

.o_dut38(r_dut38),

.o_dut39(r_dut39),

.o_dut40(r_dut40),

.o_dut41(r_dut41),

.o_dut42(r_dut42),

.o_dut43(r_dut43),

.o_dut44(r_dut44),

.o_dut45(r_dut45),

.o_dut46(r_dut46),

.o_dut47(r_dut47)

);

wire signed[15:0]r2_dut00,r2_dut01,r2_dut02,r2_dut03,r2_dut04,r2_dut05,r2_dut06,r2_dut07;

wire signed[15:0]r2_dut08,r2_dut09,r2_dut10,r2_dut11,r2_dut12,r2_dut13,r2_dut14,r2_dut15;

wire signed[15:0]r2_dut16,r2_dut17,r2_dut18,r2_dut19,r2_dut20,r2_dut21,r2_dut22,r2_dut23;

wire signed[15:0]r2_dut24,r2_dut25,r2_dut26,r2_dut27,r2_dut28,r2_dut29,r2_dut30,r2_dut31;

wire signed[15:0]r2_dut32,r2_dut33,r2_dut34,r2_dut35,r2_dut36,r2_dut37,r2_dut38,r2_dut39;

wire signed[15:0]r2_dut40,r2_dut41,r2_dut42,r2_dut43,r2_dut44,r2_dut45,r2_dut46,r2_dut47;

multer_sum multer_sum_u(

.i_clk (i_clk),

.i_rst (i_rst),

.i_din00(r_dut00),

.i_din01(r_dut01),

.i_din02(r_dut02),

.i_din03(r_dut03),

.i_din04(r_dut04),

.i_din05(r_dut05),

.i_din06(r_dut06),

.i_din07(r_dut07),

.i_din08(r_dut08),

.i_din09(r_dut09),

.i_din10(r_dut10),

.i_din11(r_dut11),

.i_din12(r_dut12),

.i_din13(r_dut13),

.i_din14(r_dut14),

.i_din15(r_dut15),

.i_din16(r_dut16),

.i_din17(r_dut17),

.i_din18(r_dut18),

.i_din19(r_dut19),

.i_din20(r_dut20),

.i_din21(r_dut21),

.i_din22(r_dut22),

.i_din23(r_dut23),

.i_din24(r_dut24),

.i_din25(r_dut25),

.i_din26(r_dut26),

.i_din27(r_dut27),

.i_din28(r_dut28),

.i_din29(r_dut29),

.i_din30(r_dut30),

.i_din31(r_dut31),

.i_din32(r_dut32),

.i_din33(r_dut33),

.i_din34(r_dut34),

.i_din35(r_dut35),

.i_din36(r_dut36),

.i_din37(r_dut37),

.i_din38(r_dut38),

.i_din39(r_dut39),

.i_din40(r_dut40),

.i_din41(r_dut41),

.i_din42(r_dut42),

.i_din43(r_dut43),

.i_din44(r_dut44),

.i_din45(r_dut45),

.i_din46(r_dut46),

.i_din47(r_dut47),

.o_dut00(r2_dut00),

.o_dut01(r2_dut01),

.o_dut02(r2_dut02),

.o_dut03(r2_dut03),

.o_dut04(r2_dut04),

.o_dut05(r2_dut05),

.o_dut06(r2_dut06),

.o_dut07(r2_dut07),

.o_dut08(r2_dut08),

.o_dut09(r2_dut09),

.o_dut10(r2_dut10),

.o_dut11(r2_dut11),

.o_dut12(r2_dut12),

.o_dut13(r2_dut13),

.o_dut14(r2_dut14),

.o_dut15(r2_dut15),

.o_dut16(r2_dut16),

.o_dut17(r2_dut17),

.o_dut18(r2_dut18),

.o_dut19(r2_dut19),

.o_dut20(r2_dut20),

.o_dut21(r2_dut21),

.o_dut22(r2_dut22),

.o_dut23(r2_dut23),

.o_dut24(r2_dut24),

.o_dut25(r2_dut25),

.o_dut26(r2_dut26),

.o_dut27(r2_dut27),

.o_dut28(r2_dut28),

.o_dut29(r2_dut29),

.o_dut30(r2_dut30),

.o_dut31(r2_dut31),

.o_dut32(r2_dut32),

.o_dut33(r2_dut33),

.o_dut34(r2_dut34),

.o_dut35(r2_dut35),

.o_dut36(r2_dut36),

.o_dut37(r2_dut37),

.o_dut38(r2_dut38),

.o_dut39(r2_dut39),

.o_dut40(r2_dut40),

.o_dut41(r2_dut41),

.o_dut42(r2_dut42),

.o_dut43(r2_dut43),

.o_dut44(r2_dut44),

.o_dut45(r2_dut45),

.o_dut46(r2_dut46),

.o_dut47(r2_dut47)

);

weight_sum2 weight_sum_u(

.i_clk (i_clk),

.i_rst (i_rst),

.i_din00(r2_dut00),

.i_din01(r2_dut01),

.i_din02(r2_dut02),

.i_din03(r2_dut03),

.i_din04(r2_dut04),

.i_din05(r2_dut05),

.i_din06(r2_dut06),

.i_din07(r2_dut07),

.i_din08(r2_dut08),

.i_din09(r2_dut09),

.i_din10(r2_dut10),

.i_din11(r2_dut11),

.i_din12(r2_dut12),

.i_din13(r2_dut13),

.i_din14(r2_dut14),

.i_din15(r2_dut15),

.i_din16(r2_dut16),

.i_din17(r2_dut17),

.i_din18(r2_dut18),

.i_din19(r2_dut19),

.i_din20(r2_dut20),

.i_din21(r2_dut21),

.i_din22(r2_dut22),

.i_din23(r2_dut23),

.i_din24(r2_dut24),

.i_din25(r2_dut25),

.i_din26(r2_dut26),

.i_din27(r2_dut27),

.i_din28(r2_dut28),

.i_din29(r2_dut29),

.i_din30(r2_dut30),

.i_din31(r2_dut31),

.i_din32(r2_dut32),

.i_din33(r2_dut33),

.i_din34(r2_dut34),

.i_din35(r2_dut35),

.i_din36(r2_dut36),

.i_din37(r2_dut37),

.i_din38(r2_dut38),

.i_din39(r2_dut39),

.i_din40(r2_dut40),

.i_din41(r2_dut41),

.i_din42(r2_dut42),

.i_din43(r2_dut43),

.i_din44(r2_dut44),

.i_din45(r2_dut45),

.i_din46(r2_dut46),

.i_din47(r2_dut47),

.o_dut (o_dut)

);

endmodule 三、仿真测试结果

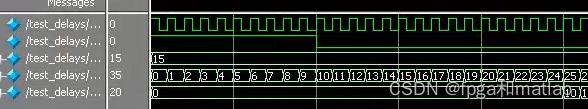

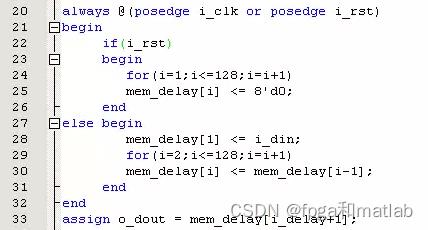

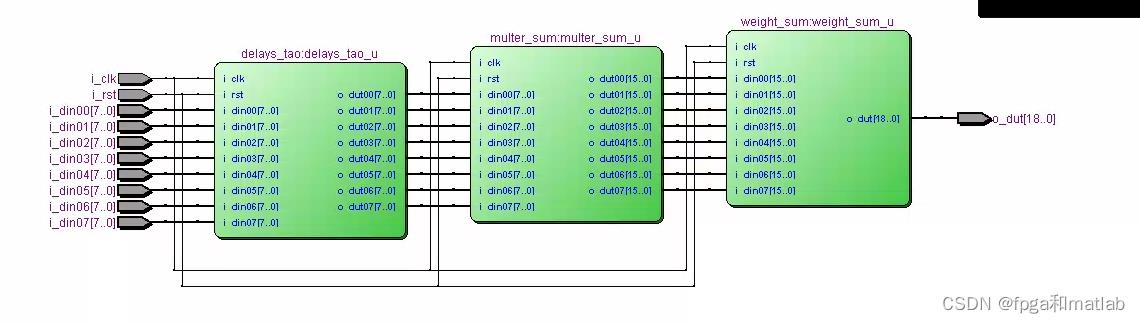

首先介绍一下延迟模块,根据各个延迟值,将其量化之后,获得不同数据的延迟值:

通过上面双口RAM的原理,获得延迟模块的设计与实现。

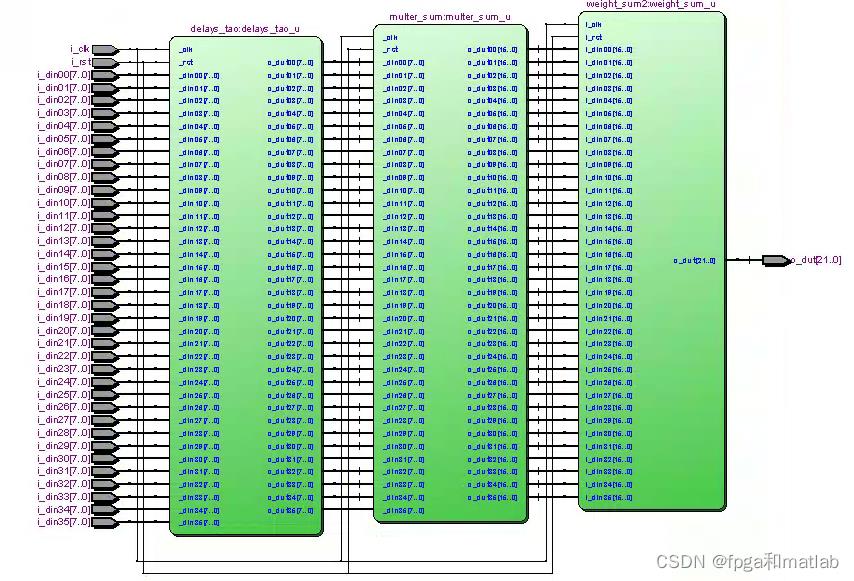

那么对于不同element个数的系统,只要调用上述模块即可。

四个数据,我们分别调用8次,24次,36次,48次即可。

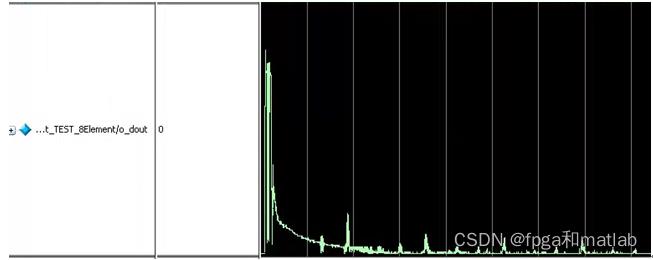

那么,对于8element,仿真结果如下图所示,其余几组类似:

这里,还是以8element为例子,进行仿真,其modelsim仿真结果如下图所示:

然后是加权和模块。

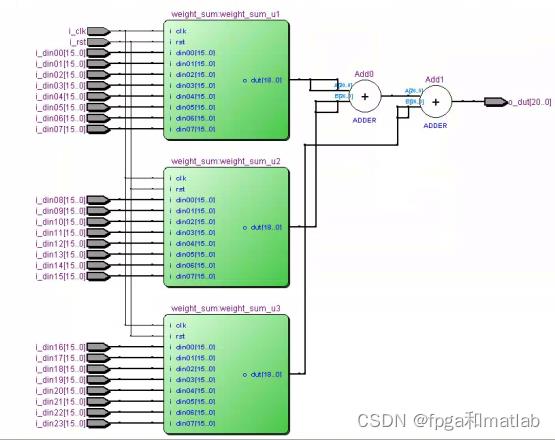

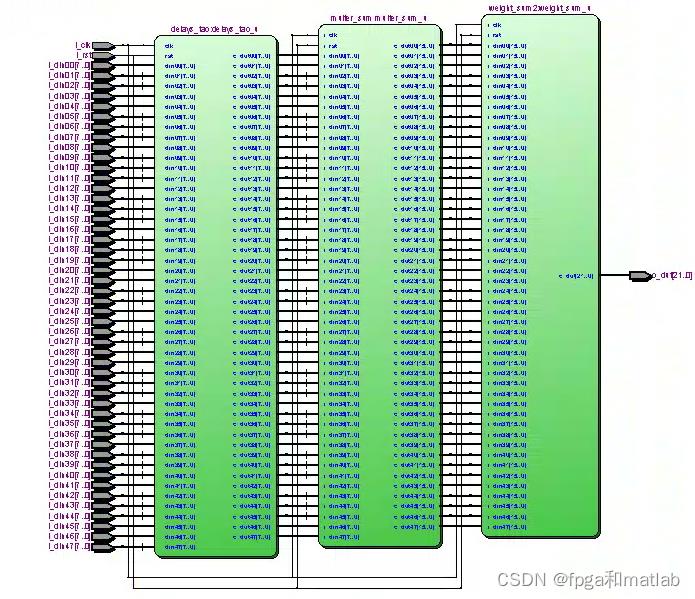

这个模块,主要采用流水线的树状结构进行逐级累积,其RTL图如下图所示:

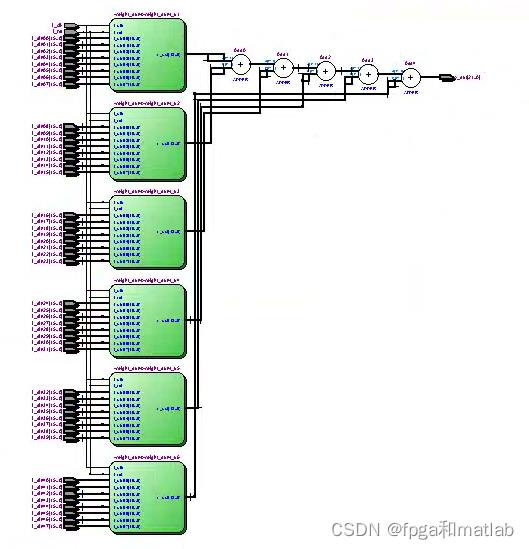

对于24.36.48element,其RTL图如下图所示:

最后得到完整的波束形成系统。

8element

24element

36element

48element

我们首先获得类似论文中的波形效果:

8element

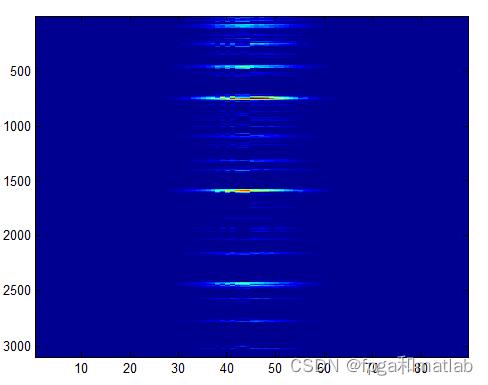

然后matlab进行成像,获得如下的效果:

8element

A21-08

以上是关于基于FPGA的波束形成verilog开发的主要内容,如果未能解决你的问题,请参考以下文章

FPGA教程案例51控制案例3——基于FPGA的PWM波形产生verilog实现

基于FPGA的DDS波形发生器可以用modelsim进行功能仿真吗?

FPGA教程案例29基于FPGA的DDS直接数字频率合成器之二——Verilog开发