雷达数字信号处理器的实时性模块化与容错设计

Posted 雷达通信电子战

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了雷达数字信号处理器的实时性模块化与容错设计相关的知识,希望对你有一定的参考价值。

预读:

实时性要求

大多数机载雷达系统需要实时完成多种模式下的单个脉冲或脉冲串的处理。换句话说,处理器用来处理数据的时间应当比它收集数据的时间要短。

但是,这并不是说处理延迟也必须满足同样的要求。可以在几个脉冲周期之后才输出第一个处理后的数据。当然这也不是绝对的,比如,对于一些高分辨率聚束SAR雷达,处理数据并形成一幅图像的时间就比收集数据的时间要长,因此这种情况下就无法对目标区域进行连续的成像。

流水线和并行计算的概念在前面纯计算层已经讨论过了,而在雷达处理链路层也可以使用流水线和并行处理技术。在纯计算层的规则在这一层中同样适用,总的目标是保持数据在流水线上移动,而不要产生瓶颈。首要的原则是提供足够的处理能力。然而,这个目标并不能百分百地实现。

处理流水线上不同阶段的工作负荷不同意味着处理架构中必须提供缓冲存储器从而使这些吞吐量的不连续性被平滑掉。

另外现代机载雷达通常会在多种工作模式下快速交替工作,这意味着会有非常大的工作负载变化,如SAR雷达和地面动目标指示(GMTI)两种模式的交替工作。这需要处理器具有快速重置能力和充足的缓存来平滑数据率的不同。这种工作模式的快速切换可以做到在操作者看来无缝连接,这需要精细的设计和对雷达时间的高度敏感。

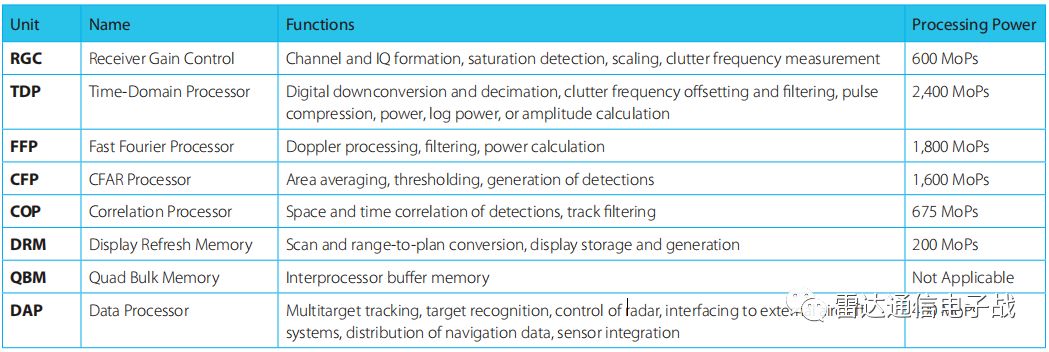

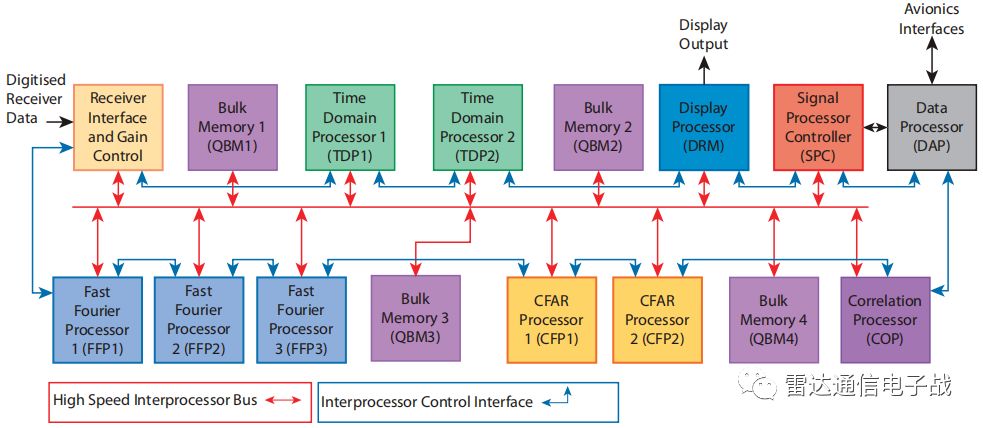

表1所示为二十世纪九十年代中期雷达信号处理器流程中的各个阶段,各部分的功能贡献以及各个阶段的处理能力指标。下图为处理流程的框图。

雷达数字信号处理器的发展

第一代(1980年代以前),处理器延时长,已实现流水线处理,但只有很小的编程弹性。控制使用硬连接线实现,且雷达通常只支持有限的几种功能。

第二代(1980-1990),这一代处理器能够充分利用高速专用集成电路技术的优势来短流水线延迟并可以使用微处理器作为控制器从而提供更加有弹性的编程能力。

在这一代处理器中,大多数组件还是定制化设计的,而且为了得到更高的性能,需要使用定制化的底板和互联系统。这一代处理器使第一代真正的多功能脉冲多普勒雷达投入使用。

设计通常会高度模块化,同样的处理模块会复用多次。通过使用定制化DSP专用集成电路技术对模块的运行进行裁剪以在信号处理流水线中完成特定的功能。

高速处理器间总线用来支持通用总线上的低延迟同步多通道数据传输。但是,这一代技术中最常见的商用货架产品的总线标准接口还不能满足雷达处理器的性能需求。

虽然这种架构在设计的应用环境中已经足够了,但仍然有架构上的缺陷。重要的缺陷是,功能专用的专用集成电路限制了流水线中高负荷阶段的资源重组。

如果信号处理过程进入到快速傅立叶变换处理阶段,那么空闲的处理器资源,如恒虚警检测处理器,却在性能提升上帮不上什么忙。另一个缺陷是通用总线的使用,限制了同步数据传输。

第三代(1990年代中期-2000年代早期)

这一代处理器减少了定制化硬件。使用商用组件,包括具有SIMD功能的通用处理器,以及FPGA,来替代专用集成电路。

商用通信市场的交换机组件可以用来进行快速弹性化的数据网络传输,而不必使用定制化组件并且移除了通用总线。更大的内存,更高的处理速率,以及非专用模块的应用大大提升了多功能指标和更低的软件部署成本。

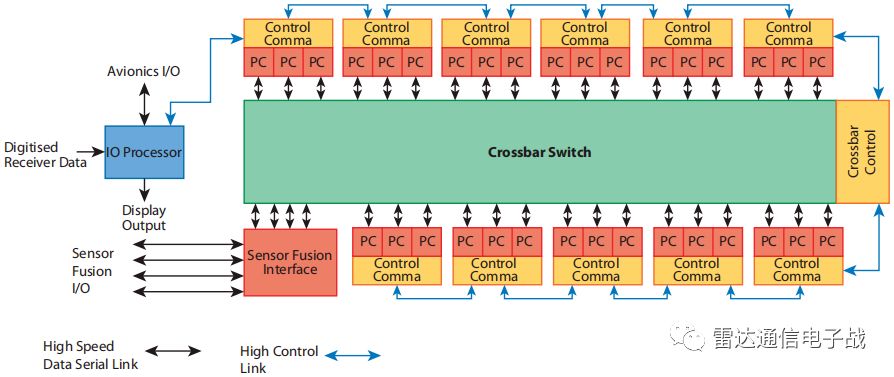

上图所示为第三代处理器架构。这代架构的处理模块包括三个完全相同的处理单元,每个处理单元都连接到交叉开关上。这种交叉开关允许在任意两个处理单元之间建立双向数据路径而不需要阻断系统中其他数据传输。

这代产品设计使用加强版的商用处理器,内存和开关组件来实现定制化架构实例。这种架构展示了一种更为规则的结构,这种结构具有更好的模块性从而克服了第二代设计的主要缺点。

在第三代产品中,这种内部互联可以根据需要进行设置,且处理器是通用的而不是像上代产品似的只适用于流水线上特定的某一阶段。

第四代:(2000年早期到现在)

从第三代到第四代信号处理架构的转换并没有表现出像前几代之间那么明显的变换。这代架构的性能优势来自于快速跟踪商用处理器的发展,以及高速通信技术标准的应用。

这代结构应用中的主要挑战是将软件分开以实现处理单元中多处理器核心的最大效率。这代产品设计可以通过人工的方式使用传统的高级语言实现或者使用高级图形化设计工具实现。

除了速度和性能的提升,第四代处理器与前几代处理器的主要不同是它们都使用军用货架模块搭建传感器的处理器。

最新一代的处理器还可以在许多现场可更换单元中拓展处理过程。由于第四代架构的的主要收益来自于它的模块化。

模块化设计

模块化设计为机载电子系统提供了巨大的操作性,保障性和成本效益。即使从单个雷达系统的角度出发,对于某个特定的机载型号也可以应用模块化设计并获得许多益处。例如,1990年代前的第二代架构就显示出了这种益处。

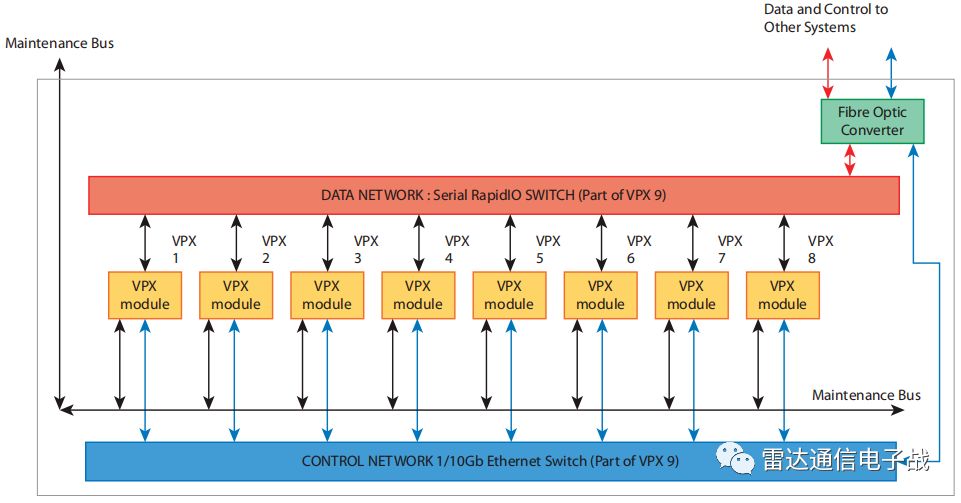

随着高性能、通用微处理器处理能力的提高,对特定功能硬件的需求已经减少。如今,除了特别苛刻的应用场景,只有雷达处理器的前端部件需要专门设计。处理器模块的商业标准已经发展到支持高速串行接口、交换结构标准和多种配置以满足军事应用环境规范。这些模块的定义可以从美国国家标准/VMEBus国际贸易协会(ANSI/VITA) 的VPX模块标准(早期Versa欧卡电路板标准(VME)的补充)中查到。

这些新标准,使得设备可以适应更加严酷的机械环境,并且为工作温度更高的模块和液体冷却提供了支撑(VITA 46、48和65)。基于这些模块的处理器设计允许快速开发、高一致性设计、模块的多源化并可以减少后勤备件储备。

这些模块的缺点是底层处理器技术变化迅速,在选择串行协议时允许很大的灵活性。不能保证MOTS或COTS模块供应商在两代或两代以上的模块设计中支持相同的接口配置或处理器配置。

上图所示为基于VPX标准的MOTS模块设计的第四代雷达处理器。图中所示的系统将占用VPX标准机架的10个插槽:VP1到VP8为VPX处理模块;VPX9用于数据和控制交换网络;VPX10为供电模块(图中没有显示)。

该处理系统中的数据网络使用一种称为串行快速IO的标准,这种标准允许灵活的互连拓扑结构并对通信冗余有强大的支持。同样的VPX模块也支持多端口10GB以太网交换机用于控制网络。有了足够数量的备用端口,这种处理系统就可以支持在主处理系统之外进行LRU扩展。

容错机制

机载雷达任务至上的特性要求雷达处理器具有高可靠性,甚至在出现故障时也能工作。如果处理器同时支持其他传感器的数据处理,那么对容错机制的需求就变得更加重要。

雷达处理器中用于确保系统正常工作的主要方法是内置测试(BIT),其目的有两方面:(1)在错误发生时进行检测;(2)尽可能准确地定位故障。处理器的所有部分都将支持上电自检(PBIT),以及周期性或连续的、非初始化的内置测试(CBIT)作为补充。此外,控制器还执行中断自检(IBIT)功能。

最初的几代处理器中使用定制化硬件,整个处理器的架构设计会从硬件上支持故障检测和定位的需求。基于商用货架产品的处理器设计的一个缺点是BIT通常没有硬件支撑。在软件层面,商用货架模块制造商通常会提供支持上电自检和中断自检的软件BIT。

编写能够可靠地检查微处理器中上千万个门电路功能的CBIT软件,同时不影响处理器正常的处理雷达信号,这绝不是一件容易的事。然而,还是有一些支持CBIT功能的微处理器。例如,大多数系统都支持温度监视,错误检测以及内存和通信包的修正,还有看门狗监视程序或处理器的异常行为。

实现上述错误检测是非常具有挑战性的,而现代化的模块化处理器可以提供容错和隔离故障的优势。

商用货架模块的容错特征包含以下几点:

1. 备份硬件模块和灵活的开关结构,允许故障模块的隔离和备用件的切换。

2. 支持故障检测和消息重路由的串行协议,如串行快速IO。这可以通过在交换结构中的冗余来补充实现。对于VPX示例(如图所示),这可能包括一个额外的交换模块,以在路由资源中提供冗余支持。

3. 具有足够存储和处理能力的处理单元,可以存储组件级别的详细信息,执行详细诊断并实现设备的智能重组。

现代处理器及其操作系统支持虚拟机操作。虚拟机将执行程序与实际硬件隔离开来,从而最小化程序错误或其他故障的后果。故障可能仅限于虚拟机,而不会导致大面积的系统故障。然后,监控操作系统可以执行适当的恢复操作。

本文为用户翻译,欢迎大家给予鼓励和支持!

以上是关于雷达数字信号处理器的实时性模块化与容错设计的主要内容,如果未能解决你的问题,请参考以下文章

基于OMAPL138/C6748 + SPARTAN-6 77GHz汽车防撞雷达信号处理平台设计