QUARTUS FPGA板级调试神器Signal Tap Logic Analyzer

Posted 小鱼FPGA

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了QUARTUS FPGA板级调试神器Signal Tap Logic Analyzer相关的知识,希望对你有一定的参考价值。

“ 利用Signal Tap Logic Analyzer,可以在板级调试的时候,实现对设计信号的采样与显示,相当于一款超级示波器”

01

—

经验漫谈

最近在调试摄像头的时候,通过Modelsim仿真,感觉设计没有任何问题,但是一上板实际测试,就老是有问题,一直没找到原因。后来了解到了Signal Tap Logic Analyzer的功能与作用,我就利用它来捕捉板级信号(设计中IO,寄存器等信号),最终助力我找到了问题所在。

所以在这我迫不及待的把这个工具推荐给大家!

02

—

工具使用介绍

Signal Tap Logic Analyzer其实就是添加额外的电路去实现对信号的采样。

以我前面做的一个流水线设计的小工程()为示例,介绍。如果手上有Altera FPGA开发板的小伙伴,可以跟着演练一遍。

-

打开上述工程后 点击 assignments -> Device

-

把器件型号改成你的板子上的FPGA的器件型号,我的是 Cyclone IV E系列的,型号为 EP4CE6E22C8

-

将整个工程全编译一遍。因为在布局布线之后Signal Tap Logic Analyzer才能获知有哪些信号。

-

全编译后,点击 Tools -> Signal Tap Logic Analyzer

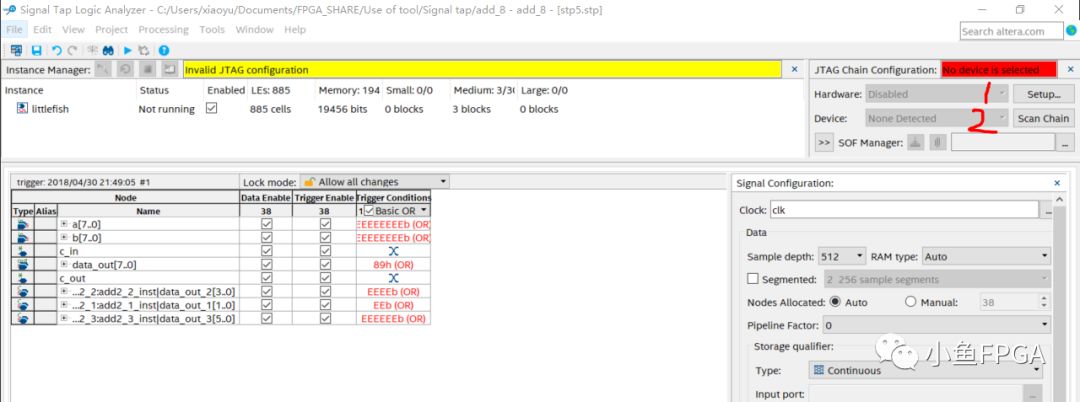

图1

图1中1的地方是一个工具自动为你生成的一个Signal Tap Logic Analyzer file ,可以右击-> Rename Instance或者按F2,对其进行从命名。我把它从命名为littlefish。

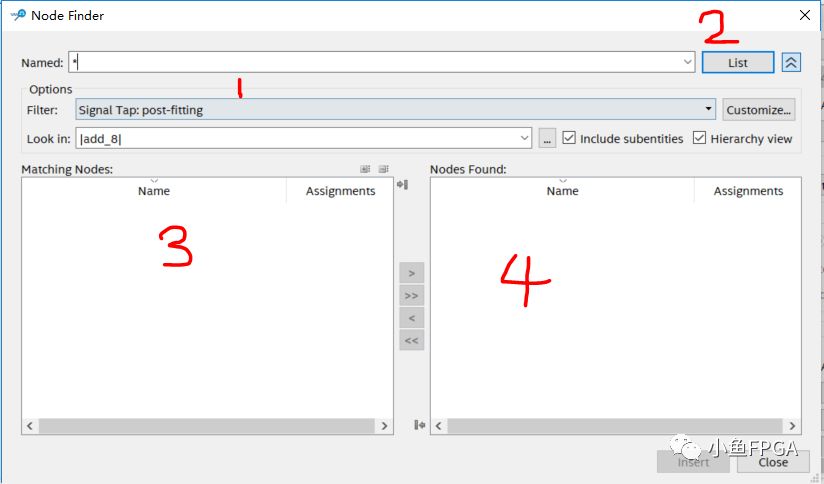

点击图1中2位置的Setup,4位置提示 Double-click to add nodes,即双击添加节点。也就是双击添加需要查看的信号节点。双击出现下图弹框。

图2

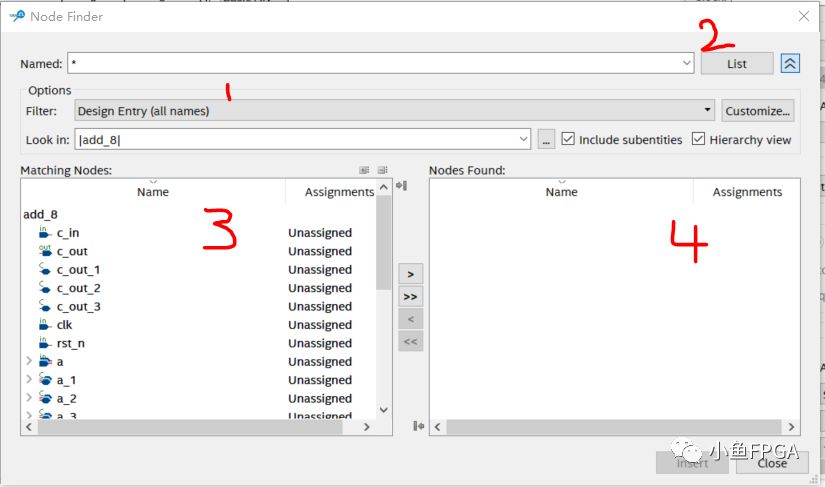

点击图2中1位置的Filter对应的下拉框,其中有一些筛选项。各筛选项具体含义在这不多说,其实大家也能看明白。我们点击选择Design Entry(all names)

再点击图2中2位置的list,过一会在位置3弹出所有设计里面的信号节点如下图。

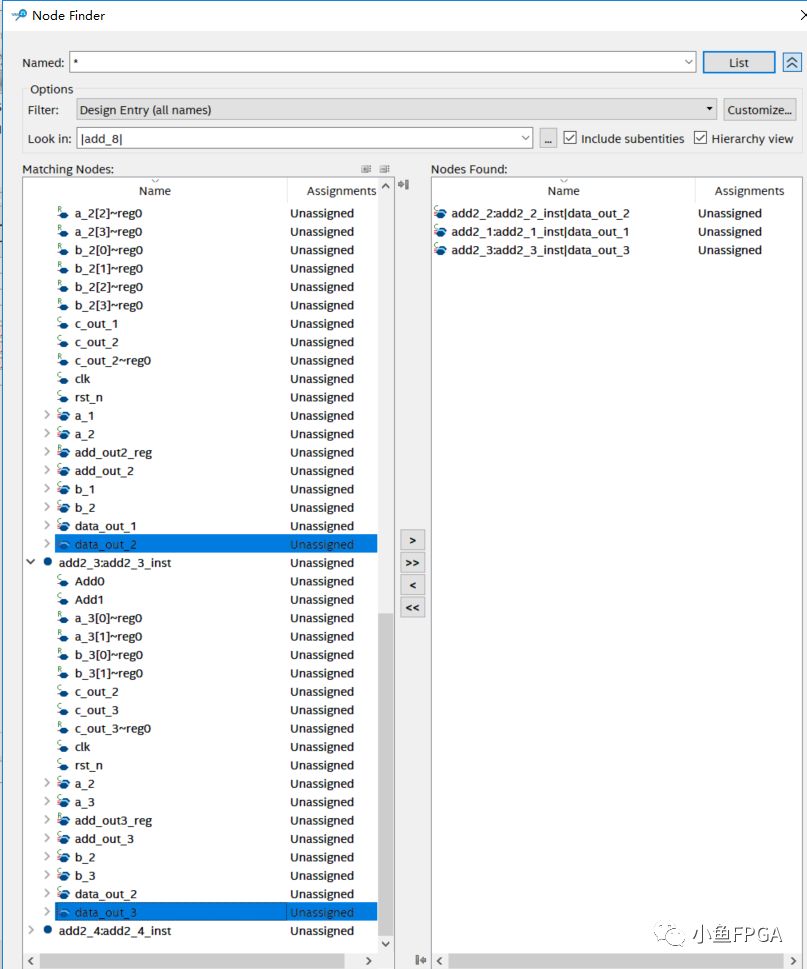

图3

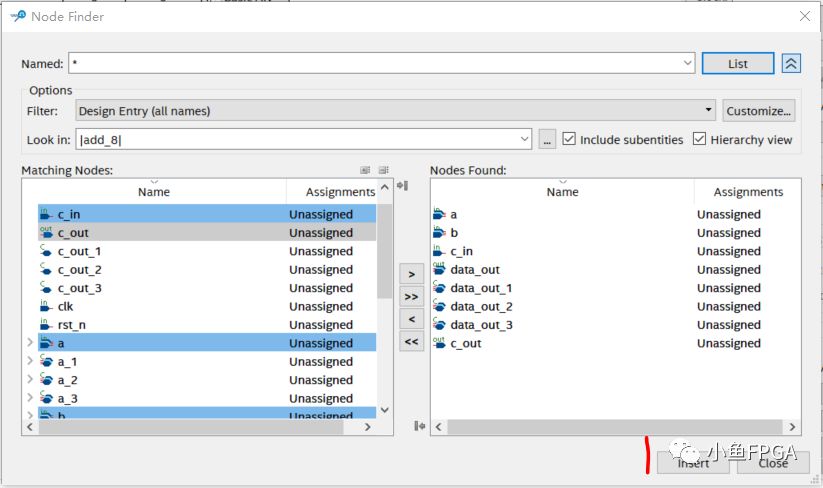

在位置3选择需要捕捉查看的信号,点击 > 按钮将其加入到4位置。

比如这里我选择a,b,c_in,data_out1,data_out2,data_out3,data_out,c_out

图4

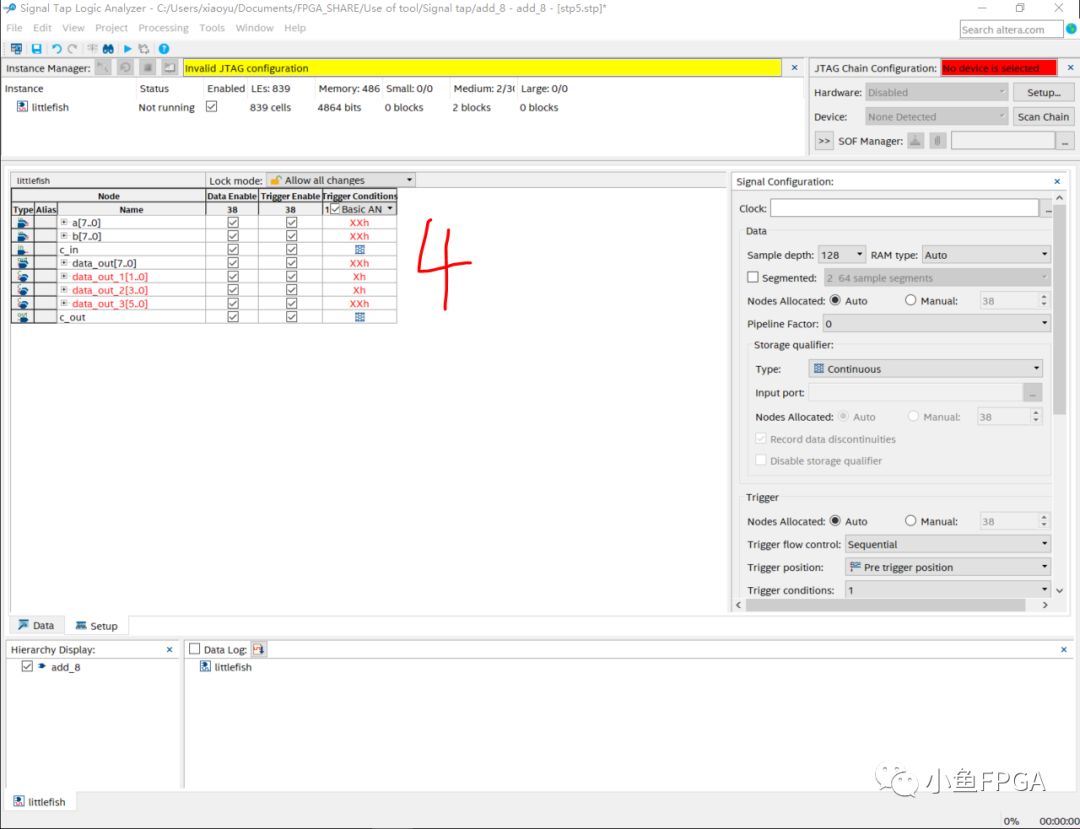

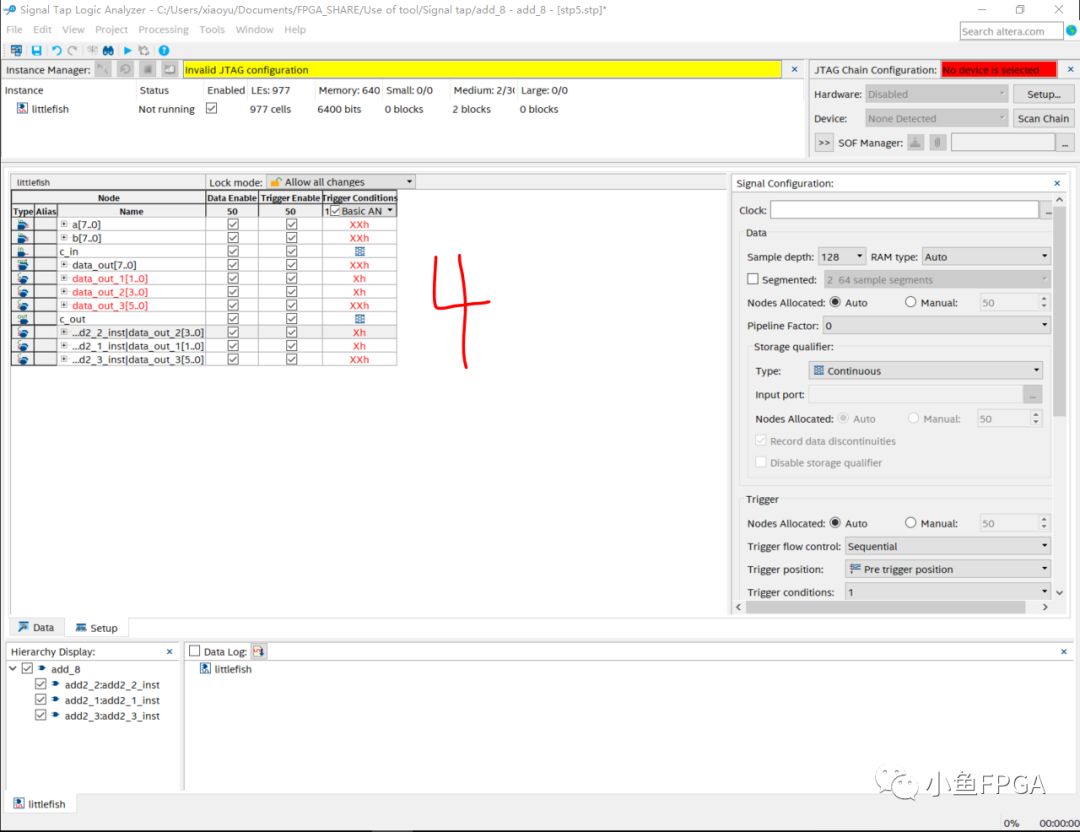

点击insert,在图1的位置4出现如下图情况。

其中data_out1,data_out2,data_out3显示为红色,说明这是无效的,原因为我们选择的data_out1,data_out2,data_out3不是其最底层模块的原始信号,而是选择了顶层模块对应的信号(很重要)。这三个信号对应的最原始的信号分别为add2_1_inst,add2_2_inst,add2_3_inst模块里面data_out1, data_out2, data_out3。从新双击4位置的空白位置。添加对应的信号。

现在4位置的情况如下图所示:

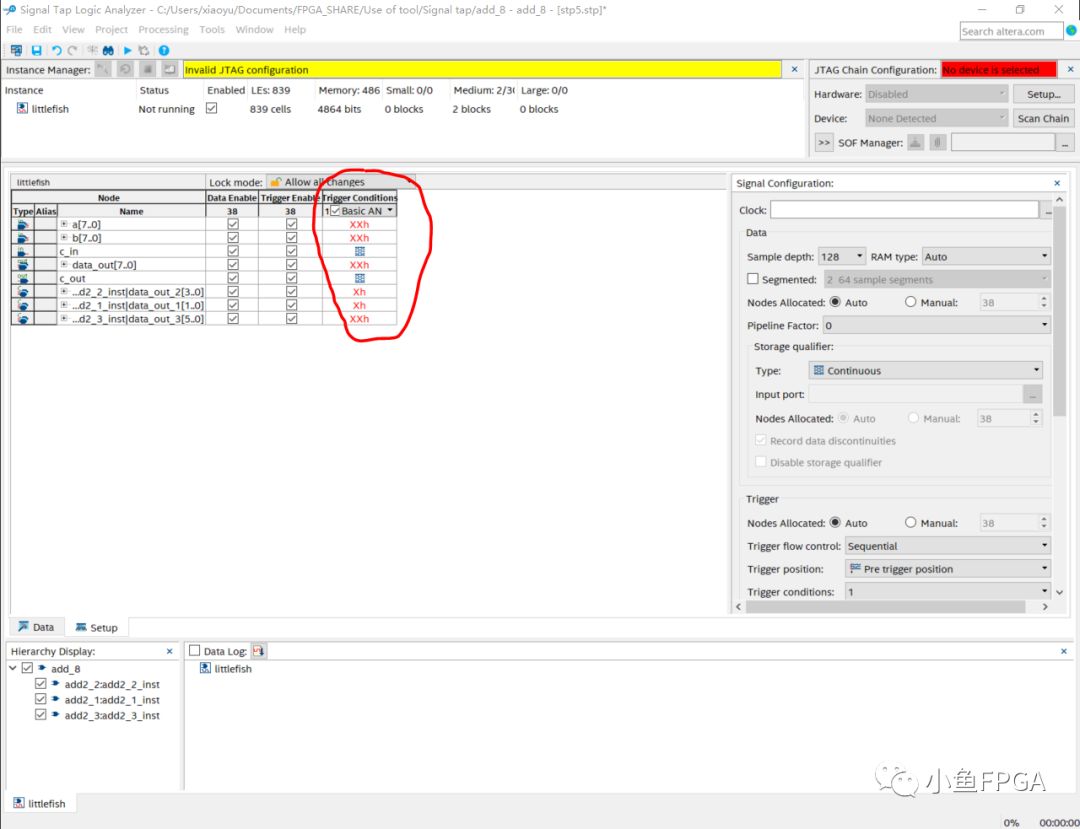

将信号名为红色的信号去掉(在相应信号上右击->Delet)得:

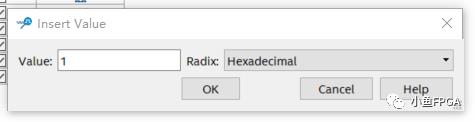

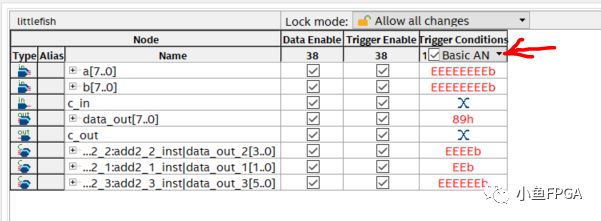

在画圈的一栏选择信号采样的触发条件(右击相应信号对应的最后一栏),出现设置选项。单bit信号可以设置为高电平,低电平或者上升沿,下降沿以及任意沿时采样。多比特信号可以设置为Either Edge采样或者在某一个特定值时采样。后一种的设置方法为右击相应信号对应的最后一栏 -> Insert Value弹出下图所示框。

Value:输入数值 Radix:设置相应的进制

比如设定data_out为在8‘h89时采样,其余信号在Either Edge采样。得到如下图所示。

上面设置完各个信号的采样条件之后,接下来就是设置这些条件之间的关系。设置方法如下:

点击上图红色箭头所指位置,其中有Basic AND,Basic OR。含义如下:

Basic AND:当所有信号的采样条件都满足时才进行采样

Basic OR:只要有某一个信号的采样条件满足就进行采样

这里我们先设置为Basic OR。

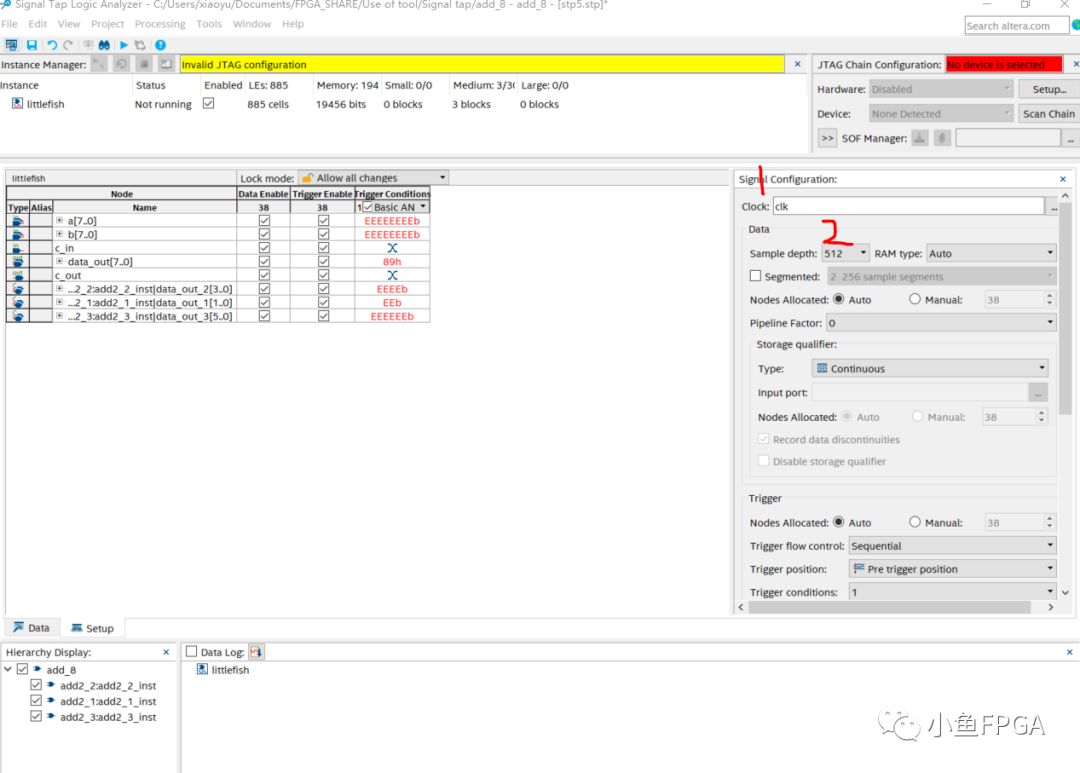

接下来就是设置采样的深度与采样时钟。采样深度即保存采样信号的数量,采样时钟即对信号进行采样的时钟,要高于被采样信号频率的两倍,一般设置为设计当中频率最高的时钟。设置方法如下图所示。

1位置设置采样时钟,这里设置为系统时钟clk; 2位置设计采样深度,这里设置为512。

到这,所有的基本设置讲解完毕。

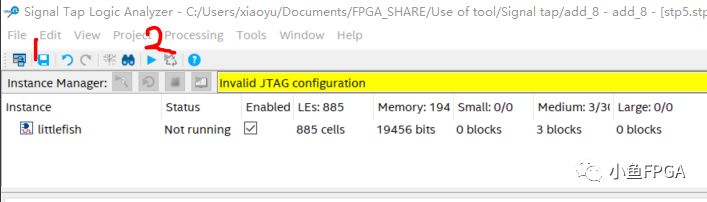

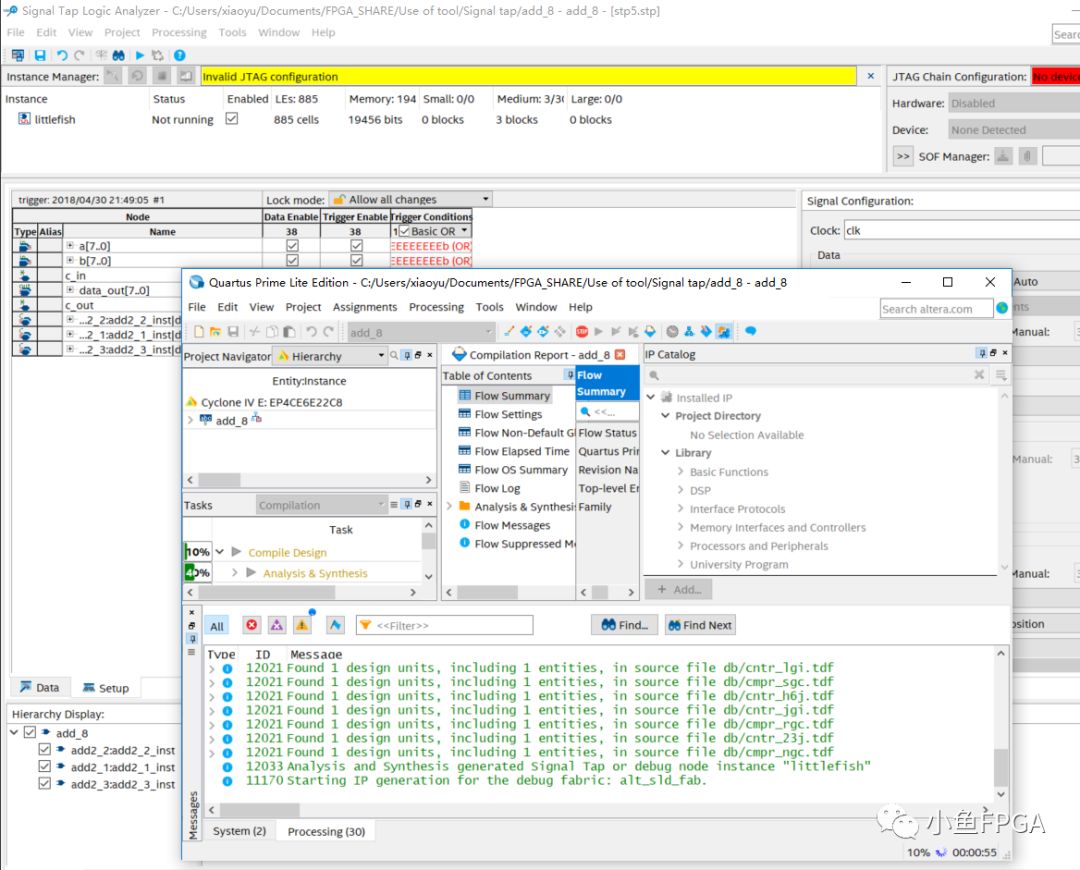

接下来进行点击保存并进行全编译(综合和布局布线),方法如下。

点击1位置的保存按钮,在接下来的弹框选择YES。再点击2位置的全编译按钮,进行全编译。

等待全编译结束。

将电脑,下载器与FPGA板子连接好。

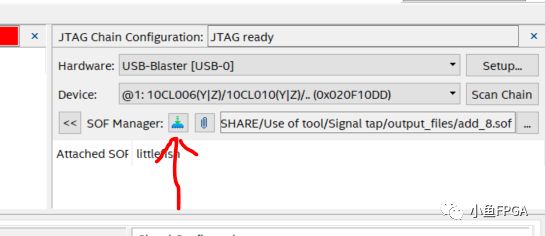

先在1位置点击Setup,查找设备;再在2位置点击Scan Chain添加sof文件。设置成功后如下图。

点击红色箭头所指按钮,进行下载(使用Signal Tap 工具,必须要在Signal Tap里面进行下载)

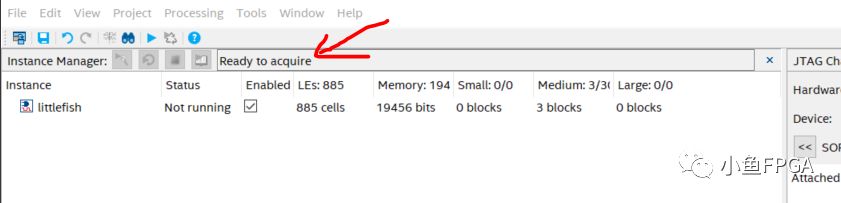

下载完成后,下图红色箭头位置会提示 Ready to acquire

点击下图1位置的Data,再选上2位置的littlefish, 最后点击3位置箭头所指按钮。

最后其效果如下图所示,显示各个信号的采样值。

点击红色箭头所指按钮,停止采样。

OK,大功告成!!!

以上是关于QUARTUS FPGA板级调试神器Signal Tap Logic Analyzer的主要内容,如果未能解决你的问题,请参考以下文章