fpga实操训练(signal tap调试)

Posted 嵌入式-老费

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了fpga实操训练(signal tap调试)相关的知识,希望对你有一定的参考价值。

【 声明:版权所有,欢迎转载,请勿用于商业用途。 联系信箱:feixiaoxing @163.com】

编写软件的同学都知道,如果需要调试软件的话,除了要学会打印信息日志之外,另外一个很重要的方面,就是学会使用调试软件的各个命令操作。windows上面的调试软件一般是visual studio,linux上面的调试软件则是gdb。调试软件基本不占用什么资源,对于简单的bug、复杂的bug都能够达到很好的调试效果。

那么今天,对于fpga调试也是一样的,需要学习对应的调试软件。特别对于fpga模块内部的逻辑,如果需要查看它们的信号逻辑,就要用到sigal tap这个软件了。这是quartus自带的调试工具,不需要额外安装。它的基本原理,就是把需要调试的信号先用ram保存下来,再用jtag送出来供开发者分析。所以,在这过程当中,可能会占用fpga上的ram资源,另外整个工程需要重新编译、综合,比较费时费力。

为了说明怎么使用signal tap软件,可以找一个demo演示一下,

module led_test(clk, rst, led);

input clk;

input rst;

output led;

wire clk;

wire rst;

reg[3:0] led;

reg[31:0] count;

wire[7:0] data;

always @(posedge clk or negedge rst)

if(!rst)

count <= 32'd0;

else if(count == 32'd4999_9999)

count <= 32'd0;

else

count <= count + 1'b1;

always@(posedge clk or negedge rst)

if(!rst)

led <= 4'd0;

else if(count == 32'd4999_9999)

led <= ~led;

endmodule

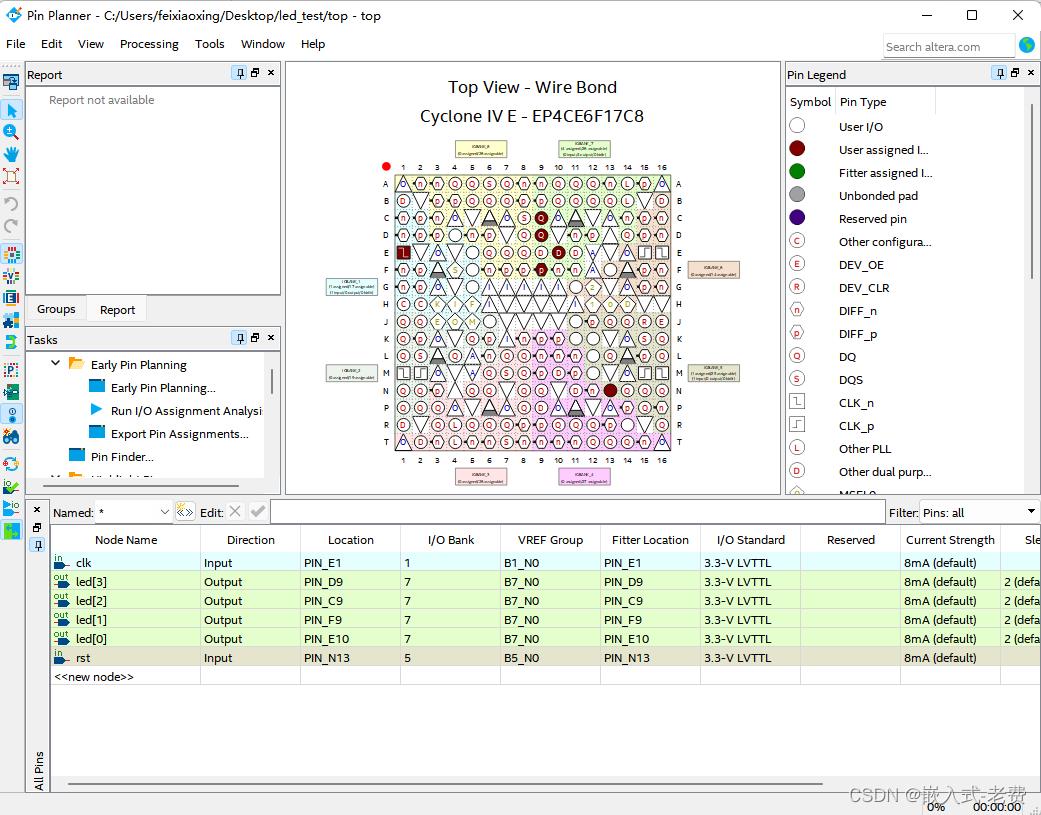

首先有这么一个verilog代码,先简单编译、综合下,确保没有问题,再进行引脚bind,

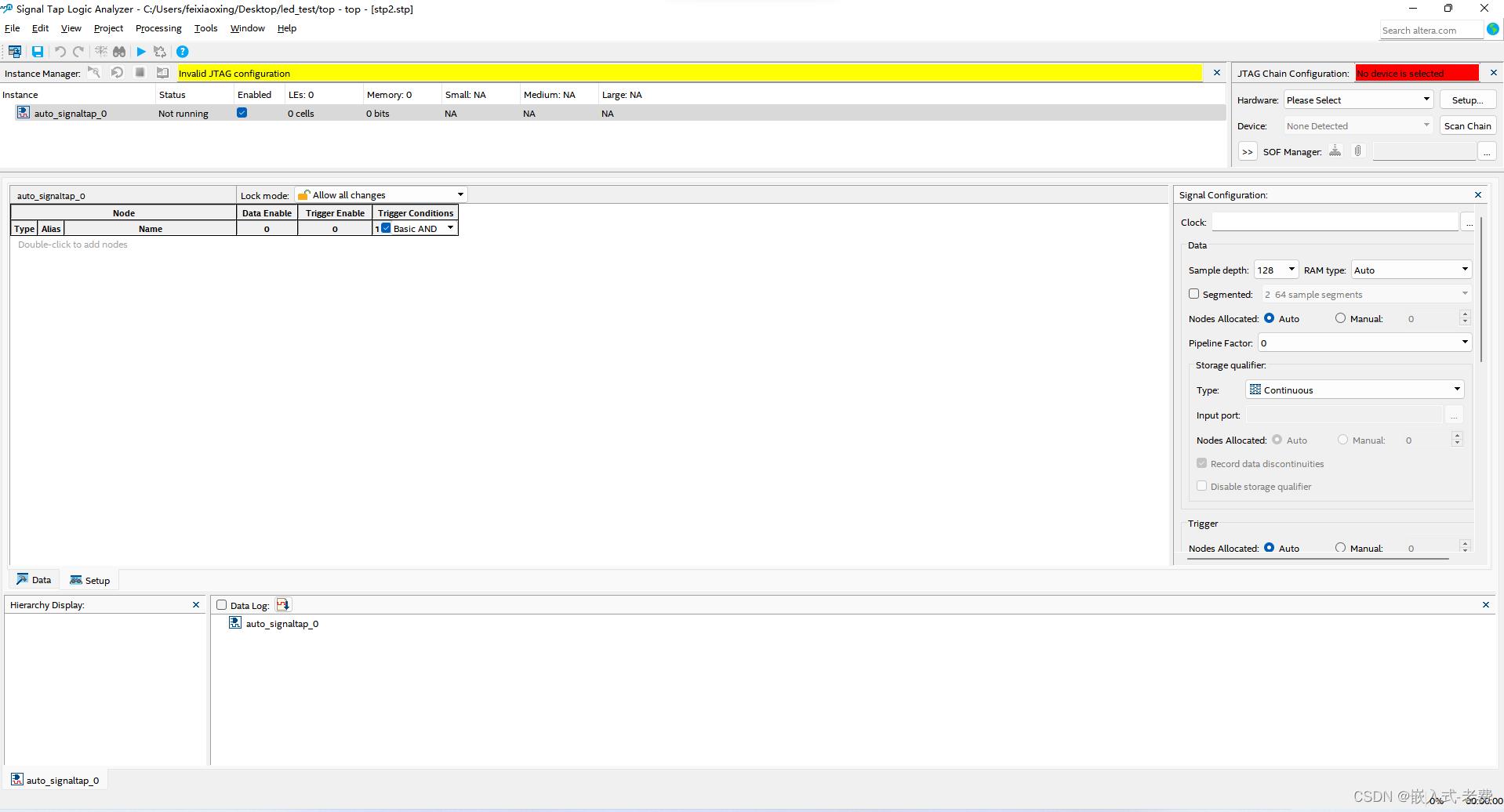

一切准备妥当,就可以开始准备signal tap的配置了。选择“Tools”-》“Signal Tap Logic Analyzer”,

不出意外,可以看到这样的界面,

这就是signal tap的界面。可以先把jtag配置下,

接着在右侧Signal Configuration里面选择clk信号,注意这里的Filter选择pre-synthesis,

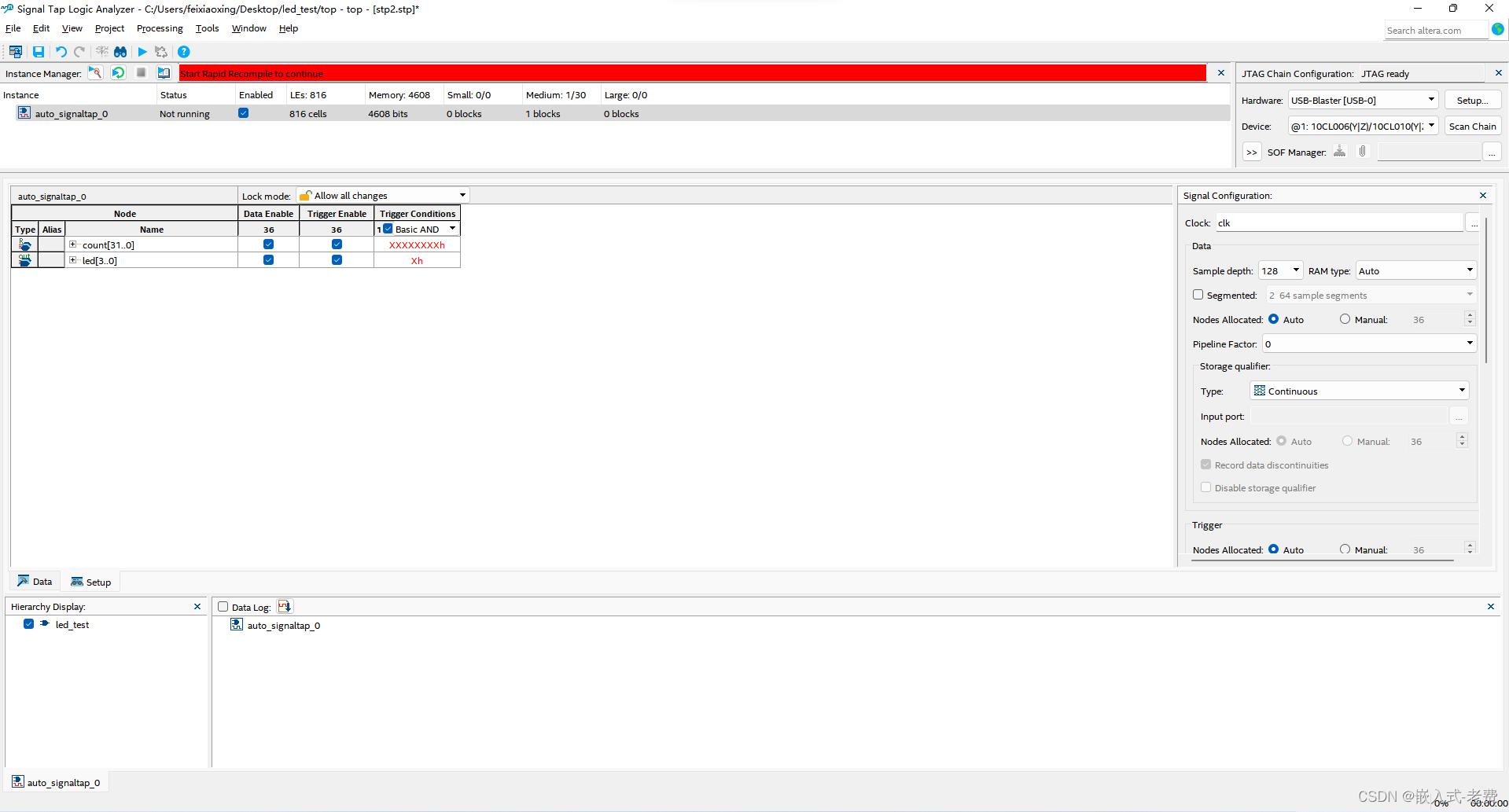

下面就是在左下侧“Setup”窗口中添加需要查看验证的信号,这里添加count和led,选择insert。

这一切都准备好了,界面是这样的,

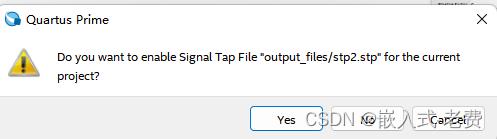

走到这一步,下面就可以退出这个窗口。系统会提示你,是否需要保存stp文件,保存即可,

接着,会继续提示你,是否把stp文件添加到当前工程,保存即可,

不出意外,你会看到stp文件已经被添加到当前工程当中。

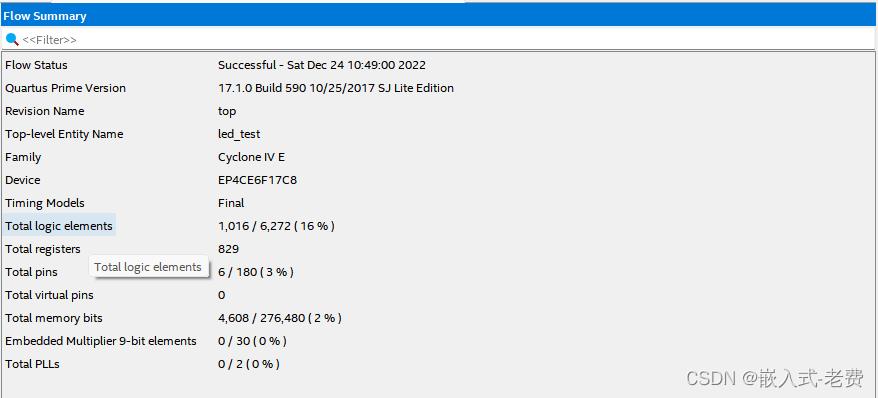

前面,我们讨论过,signal tap会占用fpga片上资源的。待会重新综合完之后,我们就可以看到结果了。和之前综合操作一样,重新综合一下,报告如下所示,

上面这是添加了stp文件之后综合的结果。可以发现,logic elements和memory bits都使用了一些。可以对比下,如果没有stp文件是什么样的情形。只需要单击“Assignments”-》“Setting”-》“Signal Tap Logic Analyzer”,去除enable之前的小箭头,

综合后的结果是这样的,

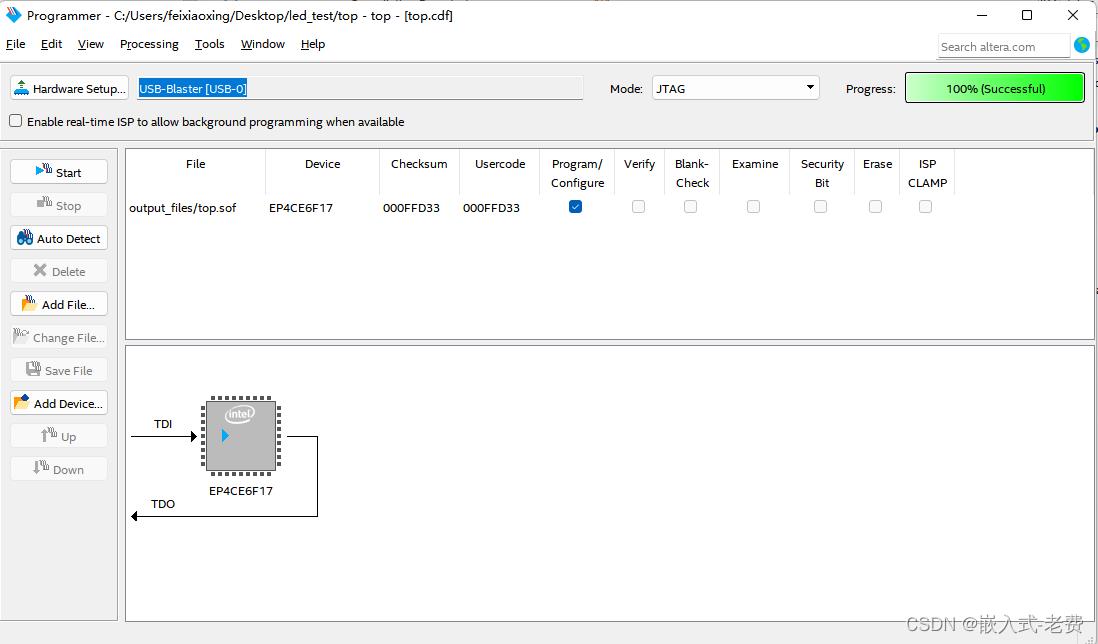

当然,这里需要演示如何使用signal tap,所以我们还是要打开这个开关的。等综合好生成sof文件之后,就可以烧入了。烧入过程和之前其他项目的烧入是一样,没有特殊之处。

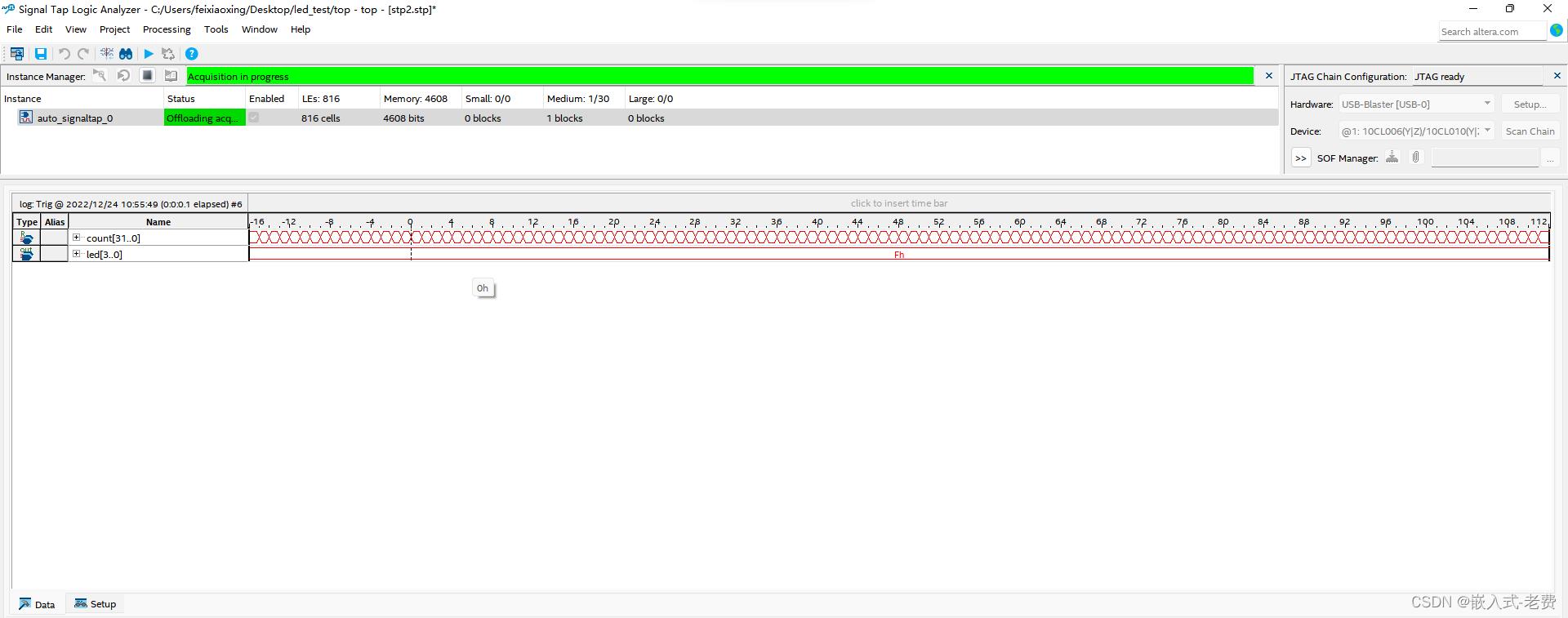

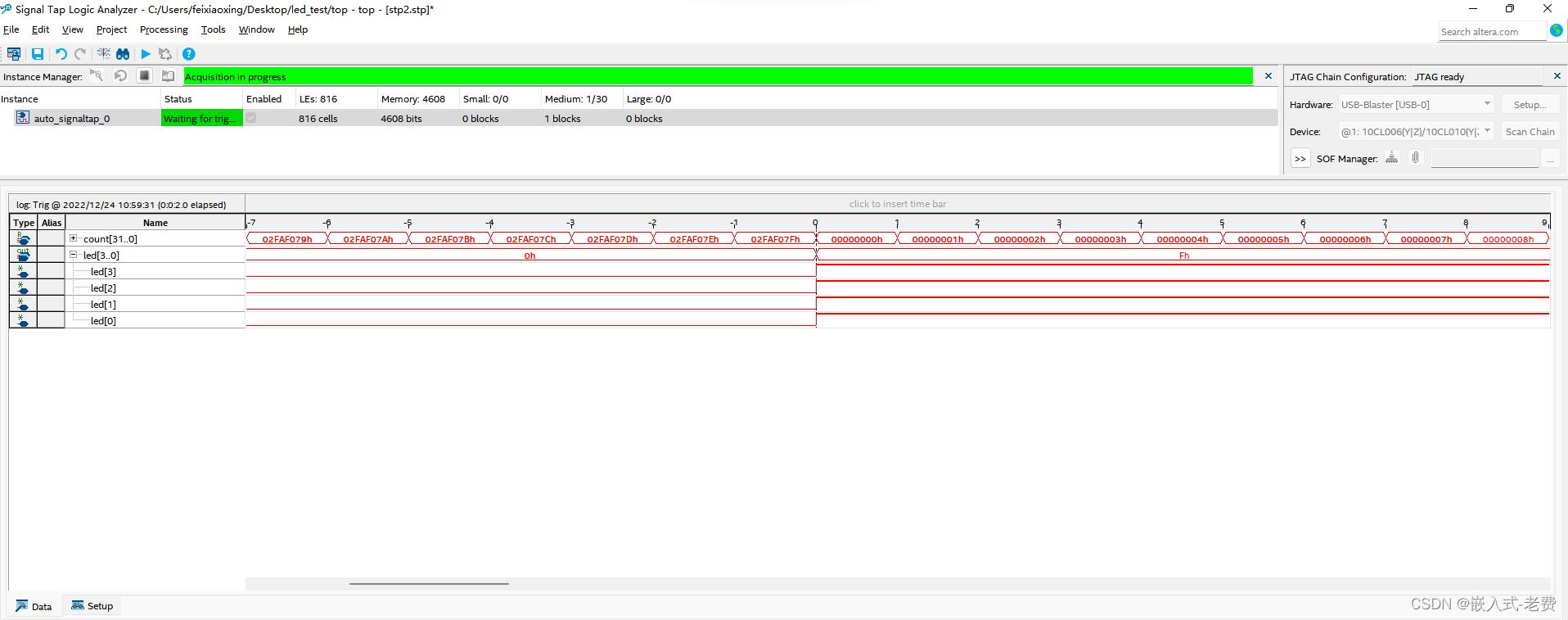

重新打开signal tap窗口,可以双击左侧stp2.stp文件,然后按下F6,“Data”窗口就会显示相关信号,

可以看到信号一直在采集。可以按下Esc,先停止采集,修正一下采集的触发条件,比如将LED修正为上升沿触发,选择上图中的“Setup”按钮,选中信号,右击按钮,

重新按下F6,就会看到这样的采集信号,

这样看上去信号就比较有意义了。注意,在这过程中开发板还是一直工作运行的,这和软件调试不一样的。将鼠标移动到信号上面,左击是放大,右击是缩小。 剩下来的工作,就是需要自己花时间慢慢掌握,变得比较熟练起来。

以上是关于fpga实操训练(signal tap调试)的主要内容,如果未能解决你的问题,请参考以下文章