ZYNQ | 开发工具

Posted ZYNQ

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了ZYNQ | 开发工具相关的知识,希望对你有一定的参考价值。

关注、星标公众号,直达精彩内容

ID :FreeZynq

从愿景到部署,Xilinx 开发工具着重端到端开发,包括:系统设计、软件和固件开发、硬件设计、协仿真和调试以及图像生成,我们先来看一段官方视频,纯英文版本的。

Xilinx 开发工具简介(点击跳转可观看)

那么在我们了解了ZYNQ之后,需要什么开发工具入手呢?

1、独立开发环境

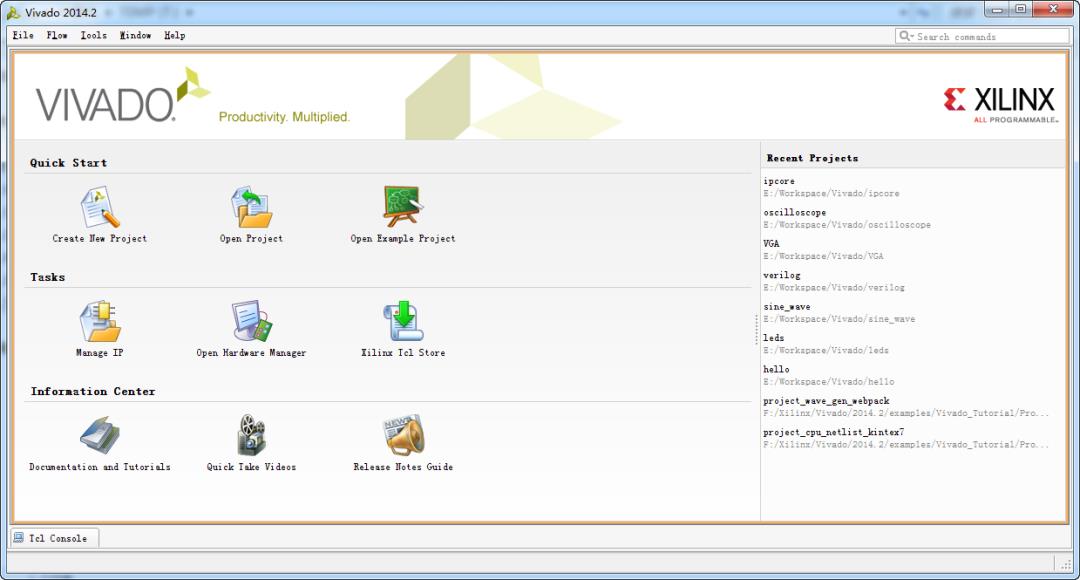

PL—> Vivado

PS(ARM)—> SDK(Xilinx)或者第三方ARM开发工具

sdk都集成在vivado中,软件首页如下图所示,目前最新版本是vivado

2019.2

Vivado Design Suite 安装简介(点击跳转可观看)

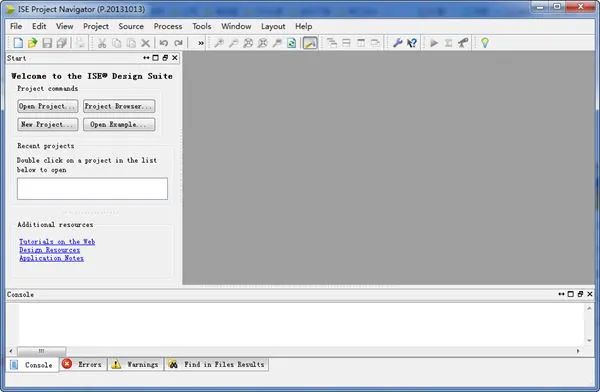

2、Xilinx ISE Design Suite

ISE design suite 支持 Spartan®-6、 Virtex®-6、和 CoolRunner™ 器件,及其上一代器件系列。ISE design suite 可以运行于 Windows 10 和 Linux 操作系统上。

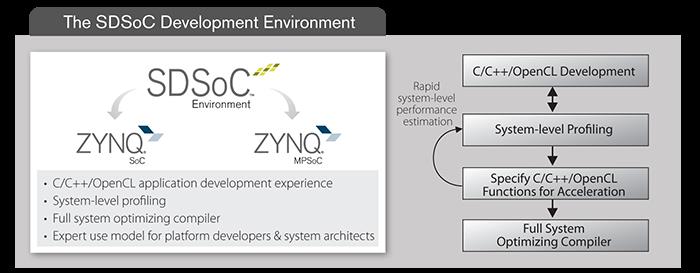

3、集成开发环境SDSoC

SDSoC 开发环境可为异构 Zynq SoC 提供类似嵌入式 C/C++/OpenCL 应用的开发体验,其中包括简单易用的 Eclipse IDE 和综合设计环境。这是具有里程碑意义的,SDSoC 提供业界首款 C/C++/OpenCL 全系统优化编译器,可实现系统级的特性描述、可编程逻辑中的自动软件加速、自动系统连接生成以及可加速编程的各种库。此外,它还可帮助最终用户及第三方平台开发人员快速定义、集成和验证系统级解决方案,为其最终用户实现定制化编程环境。

SDSoC 开发环境 (中文字幕) 演示(点击跳转可观看)

4、集成开发环境SDAccel

SDAccel 环境是一个集成型开发环境,主要针对面向 Xilinx Alveo 数据中心加速卡、AWS F1 实例以及其它 FPGA 即服务产品的应用。

它提供一个熟悉的软件开发流程,包括:

集成型开发环境 (IDE)

用于指导应用优化的分析器

面向主机及 FPGA 加速代码的编译器

快速开发及调试的仿真流程

软硬件间的自动通信

主机应用采用 C/C++ 开发,使用标准 OpenCL API 调用与 FPGA 加速函数互动,这些函数可以用 RTL 和 C/C++ 建模,也可以用 OpenCL 建模。这为硬件设计人员和软件工程师提供了熟悉的切入点。

SDAccel 开发环境介绍(点击跳转可观看)

注:自 2019.2 起,Xilinx SDKSDSoC™ 和 SDAccel™ 开发环境被整合为一个多用途的 Vitis™ 统一软件平台,用于应用加速和嵌入式软件开发。Xilinx SDK 不会有 2019.2 或更高版本。

5、Vitis™ 统一软件平台

Vitis 统一软件平台可实现在 Xilinx 异构平台(包括 FPGA、SoC 和 Versal ACAP)上开发嵌入式软件和加速应用。它可为边缘、云和混合计算应用加速提供统一编程模型。提供基于 GUI 和命令行的开发工具。

Vitis™ 统一软件平台简介视频(点击跳转可观看)

6、PetaLinux 工具

PetaLinux 工具提供在 Xilinx 处理系统上定制、构建和调配嵌入式 Linux 解决方案所需的所有组件。

PetaLinux 工具可帮助简化基于 Linux 产品的开发;您可以使用下列工具来完成从系统启动到执行的所有操作:

命令行接口

应用、器件驱动程序、库生成器以及开发模板

可引导的系统映像生成器

调试代理程序

GCC 工具

集成的 QEMU 全系统仿真器

自动化工具

支持 Xilinx 系统调试器

7、Modsim 仿真软件

modelsim是一款hdl语言仿真处理工具,它能提供友好的仿真环境,支持VHDL和Verilog混合仿真的仿真器,对加快调错提供了非常给力的手段。它采用直接优化的编译技术、Tcl/Tk技术、和单一内核仿真技术,编译仿真速度快,也将对加快调错提供了非常给力的手段。而且编译的代码与平台无关,便于保护IP核,个性化的图形界面和用户接口,为用户加快调错提供强有力的手段,让仿真更加的简单,快速,是FPGA/ASIC设计的首选仿真软件。

最后

https://china.xilinx.com/

长按识别图中二维码关注

以上是关于ZYNQ | 开发工具的主要内容,如果未能解决你的问题,请参考以下文章

ZYNQ从入门到头秃02 ZYNQ硬件介绍和Vivado开发流程