Java无垃圾稳态设计

Posted 编程一生

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了Java无垃圾稳态设计相关的知识,希望对你有一定的参考价值。

<groupId>org.openjdk.jol</groupId> 代码中使用时 其中pojo是自己要监控的对象,有空不妨试一试。 不要假定,要证明!-----《程序员修炼之道》

<artifactId>jol-core</artifactId>

<version>0.14</version>

</dependency>log.info("内部信息:[]", ClassLayout.parseInstance(pojo).toPrintable());

log.info("外部信息[]", GraphLayout.parseInstance(pojo).toPrintable());

log.info("totalSize[]", GraphLayout.parseInstance(pojo).totalSize());数字IC设计verilog编写——5无毛刺时钟MUX设计

1.Glitch Free技术

在时钟切换时,需要涉及到时钟切换的MUX设计 glitch free技术(一种防止毛刺产生的多路选择器设计)问题

无缝切换需要解决两个问题:

一是异步切换信号的跨时钟域同步问题,需要同步电路原理消除亚稳态;

二是同步好了的切换信号与时钟信号如何做逻辑,才能实现无毛刺。

2.Glitch Free 技术原理

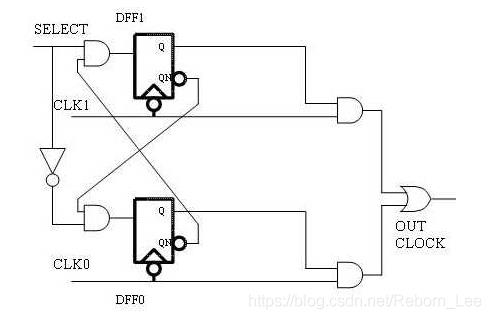

下图显示了防止源时钟相互倍数的时钟开关输出出现毛刺的解决方案。

在每个时钟源的选择路径中插入一个负边沿触发的D触发器。 在时钟的下降沿采样选择控制(SELECT),以及仅在首先使其他时钟无效后使能选择(SELECT),可以提供出色的输出保护。

当SELECT为0时,明显CLK1的那部分通路到输出无效,仅仅看下半部分电路即可,在CLK0的下降沿采样SELECT(取反后)信号,与CLK0相与之后输出;

当SELECT为1时,同理上半部分电路有效;

需要重点分析的是当SELECT在任意时刻切换的时候,输出会不会出现毛刺?

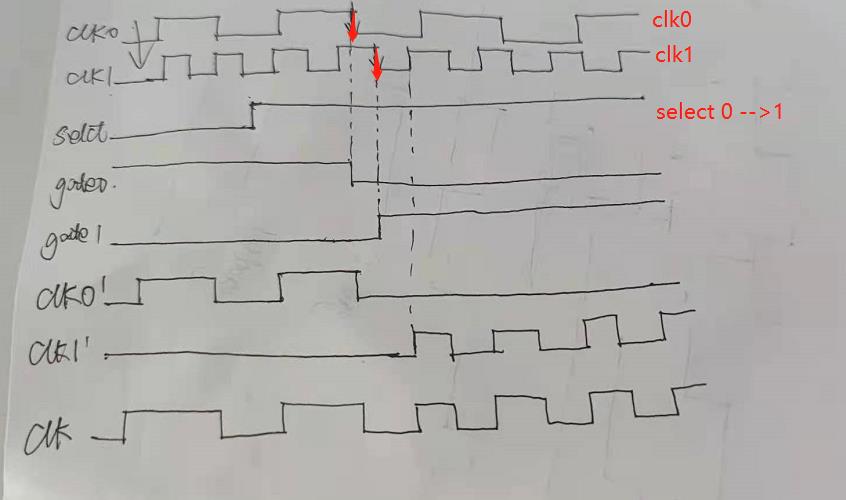

波形示意图如下所示,重点需要关注的是,只有当clk1下降沿采完SELECT变低之后,clk1的下降沿时钟才能开始采样上升沿,这类似与锁存器,先将select值锁存,等到clk1的边沿时,将值重新赋值;

2.Glitch Free 2-1MUX Verilog 实现

`timescale 1ns/10ps

module clock_mux (

// OUTPUTs

output clk_out, // Clock output

// INPUTs

input clk_in0, // Clock input 0

input clk_in1, // Clock input 1

input reset, // Reset

input select_in // Clock selection

);

//----------------------------------------

// Regs declare

//----------------------------------------

reg dff0a,dff0b;

reg dff1a,dff1b;

//----------------------------------------

// clk_in0 path

//----------------------------------------

// negedge of clk_in0

always @(negedge clk_in0 or posedge reset)

if(reset)

dff0a <= 1'b1;

else

dff0a <= !select_in & !dff1b;

always @(posedge clk_in0 or posedge reset)

if(reset)

dff0b <= 1'b1;

else

dff0b <= dff0a;

wire clk_in0_gate = clk_in0 & dff0b;

//----------------------------------------

// clk_in1 path

//----------------------------------------

// negedge of clk_in1

always @(negedge clk_in1 or posedge reset)

if(reset)

dff1a <= 1'b0;

else

dff1a <= select_in & !dff0b;

always @(posedge clk_in1 or posedge reset)

if(reset)

dff1b <= 1'b0;

else

dff1b <= dff1a;

wire clk_in1_gate = clk_in1 & dff1b;

//-----------------------

// clock mux out

//-----------------------

assign clk_out = clk_in0_gate | clk_in1_gate;

endmodule

有关多路MUX参考这篇文章:SOC设计——时钟切换的MUX设计 glitch free技术(一种防止毛刺产生的多路选择器设计)

以上是关于Java无垃圾稳态设计的主要内容,如果未能解决你的问题,请参考以下文章