怎么设计一个分频器,可实现2分频、4分频、8分频、16分频输出的电路

Posted

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了怎么设计一个分频器,可实现2分频、4分频、8分频、16分频输出的电路相关的知识,希望对你有一定的参考价值。

设计一个振荡器、分频器,可实现2分频、4分频、8分频、16分频输出的电路,每路分频输出,用发光二极管指示显示;整荡器频率及分频指示以人眼能够分辨为宜。

器材:

数字逻辑实验箱、双踪示波器、万用表,直流稳压电源、发光二极管;

集成芯片:74LS161、74LS00、74LS112、74LS74、74LS90,74LS191,NE555;

电阻、电容、导线若干、通用印刷电路板一块。

现在只看得懂 但是自己想不出来啊

使用74LS161计数振荡器的输出,不用设置复位和置数功能,计数器的输出从低位到高位正好满足2分频、4分频、8分频、16分频,分别接发光二极管即可。因为2,4,8,16正好是2的1,2,3,4次方。振荡器使用NE555搭建即可。

74LS161是常用的四位二进制可预置的同步加法计数器

74LS160 芯片是同步十进制计数器(直接清零)。

CD4060是14 级二进制串行计数器(分频器/振荡器)各引脚功能如下:

1、12级分频输出

2、13级分频输出

3 、14级分频输出

4、6级分频输出(2的6次方=64分频)

5、5级分频输出(2的5次方=32分频)

6、7级分频输出 (以此类推)

7、4级分频输出 (2的4次方=16分频)

从工作原理看,分频器就是一个由电容器和电感线圈构成的滤波网。高音通道只让高频信号经过而阻止低频信号;

低音通道正好相反,只让低音经过而阻止高频信号;中音通道则是一个带通滤波器,除了一低一高两个分频点之间的频率能够经过,高频成分和低频成分都将被阻止。

扩展资料:

功率分频器设计:

功率分频器设计在功率放大器之后,主要采用电容和电感元件组成,所以也被称作是感容分频器。因为电感和电容有滤波作用,通过电感和电容能够实现低通和高通,最后达到分割频率的目的。这类分频器设置在音箱内部,通过LC滤波网络,将功放输出的音频信号分成高、中、低之后分别送至每一个发声单元。

最简单的功率分频为电容分频,就是在高音单元的后面串联一个电容来实现分频的方法。稍微复杂一些的可以在每一路中都使用电容和电感来达到更加精确的频率分割效果。

但无论如何,功率分频器安装还是很简单的,有源和无源的音箱均能够适用。功率分频在频率分割后的频段也是存在衰减现象的,衰减曲线的斜率一般会与滤波的次数有关。

但功率分频器的缺点也比较明显,它本身就消耗功率,会出现音频谷点并产生交叉失真。另外功率分频器的参数与扬声器单元本身的阻抗拥有直接的关系,因为单元的阻抗是频率的函数,与标称值偏离很大,因此误差很大,不利于调音,可能需要足够的经验和技术才能够让功率分频实现好的效果。

功率分频器设计在功率放大器之后,主要采用电容和电感元件组成,所以也被称作是感容分频器。因为电感和电容有滤波作用,通过电感和电容能够实现低通和高通,最后达到分割频率的目的。

这类分频器设置在音箱内部,通过LC滤波网络,将功放输出的音频信号分成高、中、低之后分别送至每一个发声单元。

最简单的功率分频为电容分频,就是在高音单元的后面串联一个电容来实现分频的方法。稍微复杂一些的可以在每一路中都使用电容和电感来达到更加精确的频率分割效果。

但无论如何,功率分频器安装还是很简单的,有源和无源的音箱均能够适用。功率分频在频率分割后的频段也是存在衰减现象的,衰减曲线的斜率一般会与滤波的次数有关。

但功率分频器的缺点也比较明显,它本身就消耗功率,会出现音频谷点并产生交叉失真。另外功率分频器的参数与扬声器单元本身的阻抗拥有直接的关系,因为单元的阻抗是频率的函数,与标称值偏离很大,因此误差很大,不利于调音,可能需要足够的经验和技术才能够让功率分频实现好的效果。

在功率放大器之后,主要采用电容和电感元件组成,所以也被称作是感容分频器。因为电感和电容有滤波作用,通过电感和电容能够实现低通和高通,最后达到分割频率的目的。

这类分频器设置在音箱内部,通过LC滤波网络,将功放输出的音频信号分成高、中、低之后分别送至每一个发声单元。

74LS160 芯片是同步十进制计数器(直接清零),

CD4060是14 级二进制串行计数器(分频器/振荡器)各引脚功能如下:

①、12级分频输出 ②、13级分频输出 ③ 、14级分频输出 ④、6级分频输出(2的6次方=64分频)

⑤、5级分频输出(2的5次方=32分频) ⑥、7级分频输出 (以此类推) ⑦、4级分频输出 (2的4次方=16分频) ⑧、Vss地

⑨、信号正向输出 ⑩、信号反向输出 ⑾ 、信号输入 ⑿、复位信号输入

⒀、9级分频输出 ⒁、8级分频输出 ⒂、10级分频输出 ⒃、VDD电源

时钟分频

在设计项目的时候,系统时钟通常只有一个,而在工程应用中经常用到各种频率的时钟,这时候就要对系统时钟进行分频或者倍频以满足工程需求。

1、时钟分频两种方法:

1) PLL IP核:频率之间是否成整数比均可,可分频可倍频

2) Verilog 编写代码:频率之间得成整数比,仅可分频

在作为时钟使用的时候,通常采用PLL IP核的方式。

2、Verilog编写代码分频:偶分频、奇分频

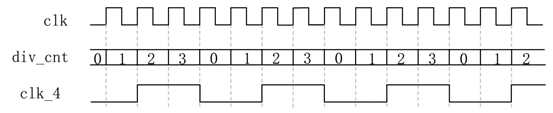

1)偶分频:在时钟的上升沿进行计数,如下图所示为4分频的波形,计数器计数值为0~N-1,分频时钟在N/2-1的时候拉高,在N-1的时候拉低。

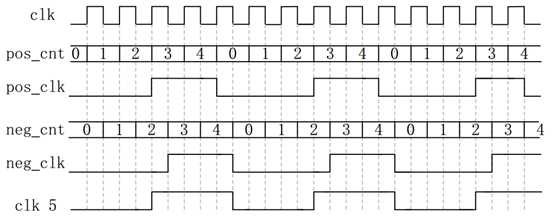

2)奇分频:在时钟的上升沿和下降沿分别采用计数器进行计数到N-1,得到上升沿的计数和下降沿的计数。如下图所示为5分频的波形,上升沿/下降沿时钟在计数器的N/2(取整数)的时候拉高,在N-1的时候拉低,最后将上升沿分频的时钟和下降沿分频的时钟进行相或,得到奇分频时钟。

以上是关于怎么设计一个分频器,可实现2分频、4分频、8分频、16分频输出的电路的主要内容,如果未能解决你的问题,请参考以下文章