基于verilog的分频器设计(半整数分频,小数分频:下)

Posted gragon

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了基于verilog的分频器设计(半整数分频,小数分频:下)相关的知识,希望对你有一定的参考价值。

第二种方法:对进行奇数倍n分频时钟,首先进行n/2分频(带小数,即等于(n-1)/2+0.5),然后再进行二分频得到。得到占空比为50%的奇数倍分频。下面讲讲进行小数分频的设计方法。

小数分频:首先讲讲如何进行n+0.5分频,这种分频需要对输入时钟进行操作。基本的设计思想:对于进行n+0.5分频,首先进行模n的计数,在计数到n-1时,输出时钟赋为‘1’,回到计数0时,又赋为0,因此,可以知道,当计数值为n-1时,输出时钟才为1,因此,只要保持计数值n-1为半个输入时钟周期,即实现了n+0.5分频时钟,因此保持n-1为半个时钟周期即是一个难点。从中可以发现,因为计数器是通过时钟上升沿计数,因此可以在计数为n-1时对计数触发时钟进行翻转,那么时钟的下降沿变成了上升沿。即在计数值为n-1期间的时钟下降沿变成了上升沿,则计数值n-1只保持了半个时钟周期,由于时钟翻转下降沿变成上升沿,因此计数值变为0。因此,每产生一个n+0.5分频时钟的周期,触发时钟都是要翻转一次.

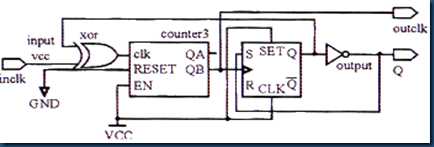

半整数分频器:计数器是通过上升沿触发,故在计数为N-1时对计数触发进行翻转,时钟的下降沿变为上升沿,因此计数值为0,所以每产生n+0.5分频时钟的周期,触发时钟都要翻转一次。如图所示,采用异或门和2分频模块设计脉冲扣除电路,脉冲扣除是输入频率和2分频输出相异或的结果。

module fenpin(clk,rst_n,clk_out); input clk; input rst_n; output clk_out; reg clk_out2; wire clk_out1; reg [1:0] cnt; reg FB_CLK; [email protected](posedge clk_out2,negedge rst_n) begin if (!rst_n) FB_CLK<=0; else FB_CLK<=~FB_CLK; end [email protected](posedge clk_out1,negedge rst_n) begin if (!rst_n) begin cnt<=0; clk_out2<=0; end else if (cnt==2) begin cnt<=0; clk_out2<=1; end else begin cnt<=cnt+1‘b1; clk_out2<=0; end end xor xor1(clk_out1,clk,FB_CLK); wire CLK_OUT_R; assign CLK_OUT_R=(cnt==1) ? 1‘b0:1‘b1; assign clk_out=clk_out2 | CLK_OUT_R; endmodule

以上是关于基于verilog的分频器设计(半整数分频,小数分频:下)的主要内容,如果未能解决你的问题,请参考以下文章