基于RS422通信的FPGA软件设计第二天

Posted 皇甫春云

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了基于RS422通信的FPGA软件设计第二天相关的知识,希望对你有一定的参考价值。

基于RS422通信的接收端FPGA软件设计报告

一、需求分析

1 设计输入

1)发送端采用RS-422标准异步串行协议,波特率为115.2kbps,每个字节发送时包含1bit起始位,8bit数据位,1bit奇校验位,1bit停止位。数据字节内部的传输顺序为低位在前高位在后,高字节在前低字节在后。(大头模式)

2)软件版本使用Vivado2016.1,硬件平台选择Xilinx A7系列XC7A100T;

3)FPGA的系统时钟为40MHz;

2 具体要求

1) 设计一个异步422接收端FPGA软件,并将接收到的数据按字节写入FPGA内部FIFO中;

2) 要求画出软件实现流程图;

3) 软件编写完成后,要求对其输出接口进行仿真,并给出仿真结果;

二、详细设计

串口通信理论学习

我们都知道,在一般情况下我们会使用串口进行通讯,但是这种串口只适合连接2个设备之间,因此存在很多不方便之处(比如我们进行一对多的通讯),制约了串行数据的收发,这个时候我们就可能需要用到485通讯协议。除了RS485以外,常见的还有RS232和RS422。

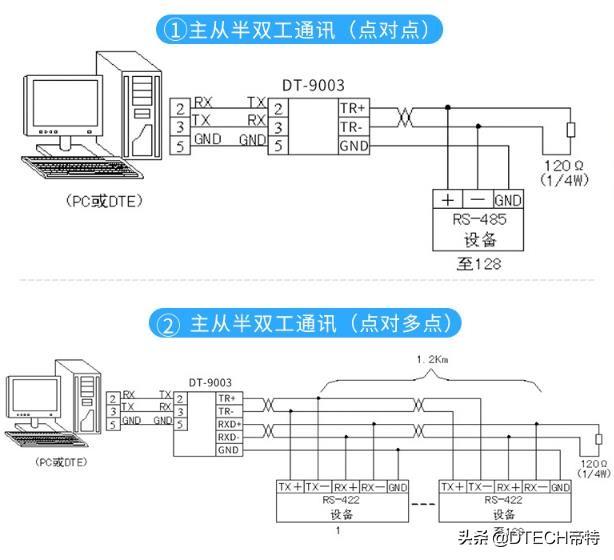

1 RS485、RS232、RS422各协议简介

RS485:2线式(A、B)、半双工、点对多主从通讯(4线制因只能点对点已经淘汰)

RS485采用差分信号负逻辑,同一总线上最多可以挂接32个节点。缺点就是共模干扰问题和EMI问题。

RS232:3线制(RXD、TXD、GND)、全双工、点对点通讯(因点对点通讯方式而无法联网,导致出现RS485)

RS232是异步传输接口,即电脑上的COM口,有9个引脚(DB-9)或者是25个引脚(DB-25)的型态出现。RS232-C标准规定的数据传输速率为50、75、100、150、300、600、1200、2400、4800、9600、19200、38400波特。

RS422:4线制、全双工、点对多主从通讯(实际上还有一根信号地线,共5根线)

RS422标准全称是“平衡电压数字接口电路的电气特性”。允许在相同传输线上连接多个接受节点,最多可接256个节点。

2 RS485、RS232、RS422的区别

1)通讯距离

RS232口最大通讯距离是15米,而RS422/485最大通讯距离是1200米。

2)所连接设备个数

RS232只能连接一个设备,而RS485可以连接多个设备。

3)这三种端口的定义

RS232是标准接口,为D形9针头,所连接设备的接口的信号定义是一样的。

而RS422/RS485为非标准接口,一般为15针串行接口(也有使用9针接口的),每个设备的引脚定义也不一样。另外还需要说明的是,RS422和RS485也有区别:RS422为4线制,全双工模式;RS485为两线制,半双工模式。

RS-232、RS-422与RS-485都是串行数据接口标准,RS-232是PC机与通信中应用最广泛的一种串行接口。RS-232被定义为一种在低速率串行通讯中增加通讯距离的单端标准。RS-232采取不平衡传输方式,即所谓单端通讯,而RJ45接口通常用于数据传输,最常见的应用为网卡接口。

9针RS232串口线序(DB9)

1 CD 载波侦测(Carrier Detect)

2 RXD 接收数据(Receive)

3 TXD 发送数据(Transmit)

4 DTR 数据终端准备(Data Terminal Ready)

5 GND 地线(Ground)

6 DSR 数据准备好(Data Set Ready)

7 RTS 请求发送(Request To Send)

8 CTS 清除发送(Clear To Send)

9 RI 振铃指示(Ring Indicator)

至于哪一个是1,我们要看具体的线材,分为交叉和直接两种接法(下图是普通的接口图,一般1234的位置都是这样的):

3 RS232,RS485的特性区别

1)RS485的电气特性:首先,逻辑性简单,十分容易表示。逻辑“1”表示的就是2到6V的电压值,逻辑“0”表示的就是-2到-6V的电压值。接口方面不易损坏,耐用。并且能与TTL兼容,使用方便,便捷。

2)RS485的数据最高传输速率为10Mbps。

3) RS485接口是采用平衡驱动器和差分接收器的组合,抗共模干能力增强,也就是说有很不错的抵御外界干扰的能力。

4) RS485接口拥有最大的传输长度规定是3900英尺,但是实际上应该能达到 2900M,并且RS232-C接口只能有一个发生器与它连接,这就叫做单站能力。但是RS485接口它可以在总线上与其他一百二十八个发生器相连。这就叫做多站能力,所以说使用者就能够使用一个RS485接口非常简单地建立起设备网络。

并且RS485有十分不错的抵抗外界干扰的能力,正是因为它拥有很远的传输距离,然后还有多站能力,这才使它在工业上得到了广泛响应。正是由于RS485接口组成的半双工网络,通常来讲要2根线,也是因为这样RS485接口都使用的是屏蔽双绞线传输。RS485接口连接器采用DB-9的9芯插头座,智能终端RS485接口采用DB-9孔,与键盘连接的键盘接口RS485采用DB-9针。

4 RS232与RS422之间转换原理和接法

大多数的时候我们日常生活中对视频、录像、换台等直接的播出以及切换控制用到的都是串口接口,绝大多数用到的都是RS232、RS422与RS485这3种。之后我们要说的就是串口的规定,用到的部件和电缆,我们将对他们进行分别阐述。

RS232、RS422与RS485标准仅仅是关于接口的电气特点存在标准,它是不会关系到插件、电缆和协议,建立在这个要求之上我们使用者能够建立属于我们的高层通信协议。

RS232、RS422和RS485他们都属于串行的数据接口,并且还都是由EIA颁发的,RS232是于1962年颁发的。RS422完全是RS232改进而来的,为了提高RS232通信长度不够用、效率不高的问题,RS422规定了一种平衡通信接口,它能够把传输速率提升至10Mbps,传输长度提高至3900英尺处于速率小于100Kbps时,还能够在一条平衡总线上连接十个接收器。

故整体的设计思路是先完成单个的RS232通信,然后再在程序中进行例化声明,来实现RS422的通信即可。具体的执行步骤如下:

第一步:调通RS232通信的接收端的程序并进行简单仿真,进行功能验证

第二步:了解RS422通信是如何和RS232通信建立的联系,得出修改建议

第三步:进行系统的联合调试

串口通讯(Serial Communication)是一种非常常用的串行通讯方式,无论是学习单片机还是 FPGA,都会从它开始入手。该协议采用异步通信的方式,在 FPGA 与其他设备如 ARM、DSP、PC间通信使用非常广泛。我们常说的UART、RS232、RS422、RS485都是采用了这种通讯协议,其接口时序都是一致的,只是具体的物理层的电平的不同。

因此,无论是RS232协议,还是RS485、RS422协议,我们都可以直接将串口的代码拿过来用,具体的物理层上的电平转换是由硬件实现的,我们不需关心。

这里着重讲解串口的接口时序及其在FPGA上的实现。

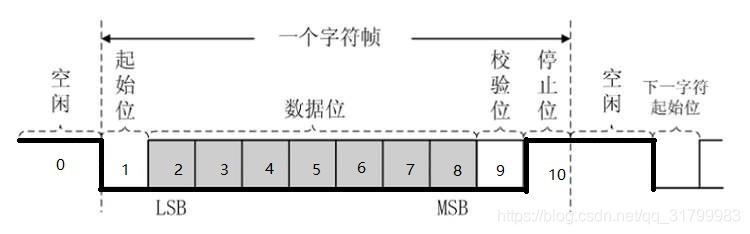

串口是由两个信号线构成,一条为接收信号 rxd,一条为发送信号线 txd。我们在与另一方进行通信前,需要约定好波特率、停止位、奇偶校验等,才能进行良好的通信。通常我们一次发送一个字节的有效数据,即一个字节。下面我们默认使用发送一个字节来进行说明。

具体的时序如下图所示,我们可以看到每一个时刻发送的数据。以发送为例,txd 在不工作时处于空闲状态,即高电平,当有数据需要发送时,txd 由 0 时刻跳转到 1 时刻,电平由高电平变为低电平并保持一个波特率的时间,跳转到时刻 2 开始发送一个数据字节的 LSB(最低位),每隔一个波特率的时间会开始发送下一个 bit,直到 8 个 bit 位发送完成,即到了时刻 9 ,开始发送校验位(具体为0还是为1需要根据发送的数据即采用的校验方式决定),在经过一个波特率时间后,开始发送停止位(如果停止位设置为 1,则保持一个波特率时长的时间;如果停止位为 2,则保持 2 个波特率时长的时间),至此一帧数据发送完毕。

奇偶校验:奇校验指的是让数据位与校验位中的 1 的个数为奇数 ,偶校验则让数据位与校验位中的 1 的个数为偶数。

版权声明:本文为CSDN博主「fpgaer0630」的原创文章,遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接及本声明。

原文链接:https://blog.csdn.net/qq_31799983/article/details/94880571

经过上述的内容学习,从理论上理解了RS232通信到RS422通信的过渡,即差分信号已经经过了芯片的处理。

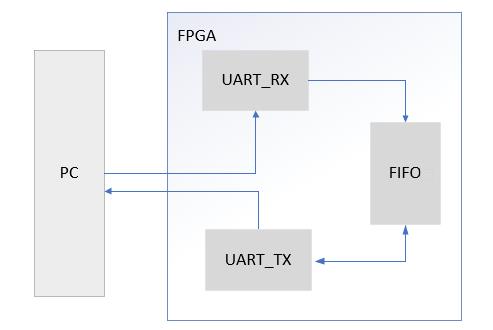

4 RS232通信回环实验设计

这个是实现RS422通信的一个关键步骤,这里采用自顶向下的设计方式,实现回环实验,需要设计一个顶层模块,顶层模块又包括发送模块,接收模块,数据处理模块和上位机软件四个部分组成,具体的框图如下所示:

下面逐一介绍上述顶层模块和其中三个模块的功能和外部引脚定义。

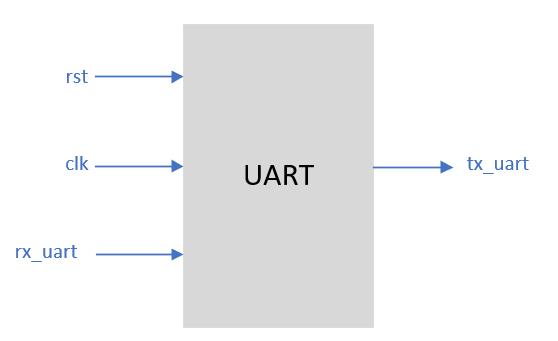

- 顶层模块

| 顶层模块 | |||

|---|---|---|---|

| 引脚定义 | 方向 | 位宽 | 含义 |

| rst | 输入 | 1bit | 实现串口的全局复位 |

| clk | 输入 | 1bit | 为串口通信实现时钟 |

| rx_uart | 输入 | 1bit | 数据的输入端 |

| tx_uart | 输出 | 1bit | 数据的输出端 |

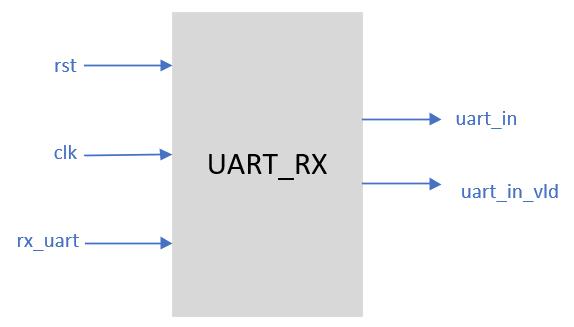

- 接收模块

| UART_RX模块 | |||

|---|---|---|---|

| 引脚定义 | 方向 | 位宽 | 含义 |

| clk | 输入 | 1bit | 为串口接收模块提供时钟 |

| rst | 输入 | 1bit | 对串口接收模块进行复位操作 |

| rx_uart | 输入 | 1bit | 作为串口模块对外的输入接口 |

| uart_in | 输出 | 8bit | 作为串口模块内部的数据输出接口 |

| uart_in_vld | 输出 | 1bit | 指明当前接受到的数据是有效的,高有效 |

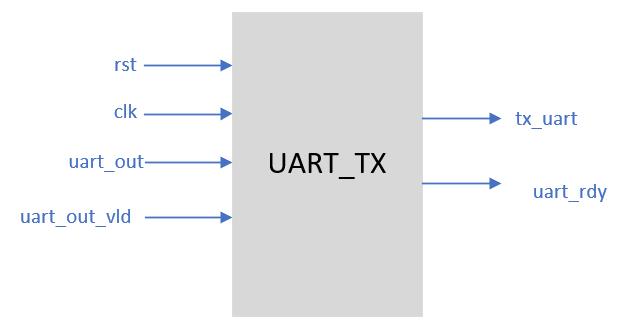

- 发送模块

| UART_TX模块 | |||

|---|---|---|---|

| 引脚定义 | 方向 | 位宽 | 含义 |

| rst | 输入 | 1bit | 实现发送模块的复位 |

| clk | 输入 | 1bit | 为发送模块提供时钟 |

| uart_out | 输入 | 8bit | 作为串口内部的数据输入接口 |

| uart_out_vld | 输入 | 1bit | 指明当前发送的数据是有效的 |

| tx_uart | 输出 | 1bit | 作为串口模块对外发送数据的接口 |

| uart_rdy | 输出 | 1bit | 指明当前发送模块的忙闲状态,高为闲,低为忙 |

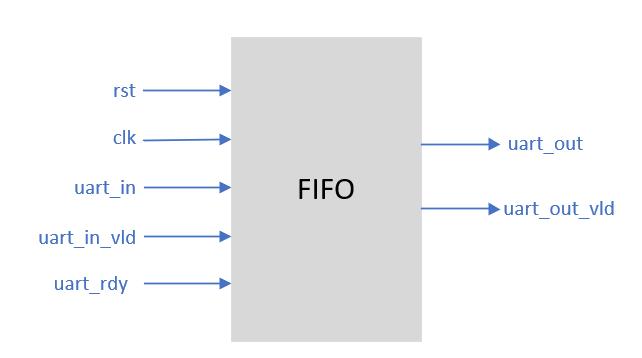

- 缓存处理模块

| 缓存处理模块 | |||

|---|---|---|---|

| 引脚定义 | 方向 | 位宽 | 含义 |

| clk | 输入 | 1bit | 为处理模块提供时钟 |

| rst | 输入 | 1bit | 实现对处理模块的复位 |

| uart_in | 输入 | 8bit | 接收串口内部的数据 |

| uart_in_vld | 输入 | 1bit | 用于判断串口内部当前接收到的数据是否有效 |

| uart_rdy | 输入 | 1bit | 判断串口内部下游的模块的闲忙状态 |

| uart_out | 输出 | 8bit | 将串口的串行数据转换为并行输出给下游模块 |

| uart_out_vld | 输出 | 1bit | 指示当前串口内部输出的数据是否有效 |

三、仿真结果

四、 问题思考

五、参考资料

[参考一](终于有人把常用的三种通讯方式:RS485、RS232、RS422讲明白了_新浪科技_新浪网 (sina.com.cn))

[参考二]([ZYNQ Ultrascale+ MPSOC FPGA教程]第十二章 RS422实验_ALINX技术博客-CSDN博客)

[参考三]([ZYNQ Ultrascale+ MPSOC FPGA教程]第十二章 RS422实验_ALINX技术博客-CSDN博客)

参考五

以上是关于基于RS422通信的FPGA软件设计第二天的主要内容,如果未能解决你的问题,请参考以下文章

基于Quartus II软件FPGA与PC之间的串行通信系统开发(9000+字)