实验:4级流水线32bits全加器

Posted jtwty

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了实验:4级流水线32bits全加器相关的知识,希望对你有一定的参考价值。

一.实验内容

本次实验为仿真实验,设计完成后仅需进行行为仿真。

实验要求:

- 实现 4 级流水线 32bit 全加器,需带有流水线暂停和刷新;

- 模拟流水线暂停,仿真时控制 10 周期后暂停流水线 2 周期(第 2 级),流水线恢复流动;

- 模拟流水线刷新,仿真时控制 15 周期时流水线刷新(第 3 级)。

二.实验设计

(1)功能描述

输入两个32位数据进行加法运算,以四级流水线来执行,最终输出结果与溢出位。运算模块具有暂停和刷新功能。

(2)接口定义

| 接口 | I/O端口 | 位宽 | 功能描述 |

|---|---|---|---|

| cin_a | input | 32 | 第一个输入数据端口 |

| cin_b | input | 32 | 第二个输入数据端口 |

| rst | input | 1 | 刷新端口 |

| clk | input | 1 | 时钟端口 |

| stop | input | 1 | 停止端口 |

| c_in | input | 1 | 进位端口 |

| c_out | input | 1 | 溢出端口 |

| sum | input | 32 | 输入结果 |

(3)逻辑控制

我们将32位相加分为四次进行,即每次相加8位,然后用寄存器存储每次相加后的结果、进位情况以及未相加部分。其中cout1、cout2、cout3、cout4来存储溢出位,sum1、sum2、sum3、sum4存储每次累加后的结果,surA1、surA2、surA3存储cin_a的未参与相加数据,surB1、surB2、surB3存储cin_b的未参与相加数据。

三.verilog语言流水线代码

module add32_4(

input [31:0] cin_a, //输入两个操作数

input [31:0] cin_b,

input rst, //归零

input clk, //时钟

input stop, //停止

input c_in, //进位标志

output wire c_out, //溢出标志

output wire [31:0] sum //和

);

reg cout1,cout2,cout3,cout4; //存储溢出位

//存储对应每级累加后的结果

reg [7:0] sum1;

reg [15:0] sum2;

reg [23:0] sum3;

reg [31:0] sum4;

//存储每次加8位后剩余的数据

reg [23:0] surA1,surB1;

reg [15:0] surA2,surB2;

reg [7:0] surA3,surB3;

//第一级

always@(posedge clk)

begin

if(rst)

begin

cout1<=0;

sum1<=0;

surA1<=0;

surB1<=0;

end

else if(stop)

begin

cout1<=cout1;

sum1<=sum1;

surA1<=surA1;

surB1<=surB1;

end

else

begin

{cout1,sum1} = {1'b0,cin_a[7:0]} + {1'b0,cin_b[7:0]} + {7'b0000_000,c_in};

surA1<=cin_a[31:8];

surB1<=cin_b[31:8];

end

end

//第二级

always@(posedge clk)

begin

if(rst)

begin

cout2<=0;

sum2<=0;

surA2<=0;

surB2<=0;

end

else if(stop)

begin

cout2<=cout2;

sum2<=sum2;

surA2<=surA2;

surB2<=surB2;

end

else

begin

{cout2,sum2[15:7]} = {1'b0,surA1[7:0]} + {1'b0,surB1[7:0]} + {7'b0000_000,cout1};

sum2[7:0]<=sum1;

surA2<=surA1[23:8];

surB2<=surB1[23:8];

end

end

//第三级

always@(posedge clk)

begin

if(rst)

begin

cout3<=0;

sum3<=0;

surA3<=0;

surB3<=0;

end

else if(stop)

begin

cout3<=cout3;

sum3<=sum3;

surA3<=surA3;

surB3<=surB3;

end

else

begin

{cout3,sum3[23:16]} = {1'b0,surA2[7:0]} + {1'b0,surB2[7:0]} + {7'b0000_000,cout2};

sum3[15:0]<=sum2;

surA3<=surA2[15:8];

surB3<=surB2[15:8];

end

end

//第四级

always@(posedge clk)

begin

if(rst)

begin

cout4<=0;

sum4<=0;

end

else if(stop)

begin

cout4<=cout4;

sum4<=sum4;

end

else

begin

{cout4,sum4[31:24]} = {1'b0,surA3[7:0]} + {1'b0,surB3[7:0]} + {7'b0000_000,cout3};

sum4[23:0]<=sum3;

end

end

assign sum=sum4;

assign c_out=cout4;

endmodule

四.仿真文件

module add32_4_test( );

reg [31:0] cin_a;

reg [31:0] cin_b;

reg clk;

reg rst;

reg cin;

reg stop;

wire cout;

wire [31:0] sum;

initial begin

clk = 1;

rst = 0;

stop = 0;

cin_a = 32'h0000_0000;cin_b=32'h0000_0000;cin=1'b0;

@(posedge clk)

cin_a = 32'h0000_0000;cin_b=32'h0000_0000;cin=1'b0;

@(posedge clk) cin_a = 32'h0000_0000;cin_b=32'h0000_0000;cin=1'b0;

@(posedge clk) cin_a = 32'h0000_0001;cin_b=32'h0000_0001;cin=1'b0;

@(posedge clk) cin_a = 32'h0000_0010;cin_b=32'h0000_0001;cin=1'b0;

@(posedge clk) cin_a = 32'h0000_0100;cin_b=32'h0000_0001;cin=1'b0;

@(posedge clk) cin_a = 32'h0000_1000;cin_b=32'h0000_0001;cin=1'b1;

@(posedge clk) cin_a = 32'h0001_0000;cin_b=32'h0000_0001;cin=1'b1;

@(posedge clk) cin_a = 32'h0010_0000;cin_b=32'h0000_0001;cin=1'b1;

@(posedge clk) stop=1;cin_a = 32'h0100_0000;cin_b=32'h0000_0001;cin=1'b1;

@(posedge clk) cin_a = 32'h1000_0001;cin_b=32'h0000_0001;cin=1'b1;

@(posedge clk) stop=0;cin_a = 32'h1000_1111;cin_b=32'h0000_0001;cin=1'b1;

@(posedge clk) cin_a = 32'h1000_0001;cin_b=32'h0000_0001;cin=1'b1;

@(posedge clk) cin_a = 32'h1000_0001;cin_b=32'h0000_0001;cin=1'b1;

@(posedge clk) cin_a = 32'h1000_0001;cin_b=32'h0000_0001;cin=1'b1;

@(posedge clk) rst=1;cin_a = 32'h1000_0001;cin_b=32'h0000_0001;cin=1'b1;

@(posedge clk) cin_a = 32'h1000_0011;cin_b=32'h0000_0001;cin=1'b1;

@(posedge clk) cin_a = 32'h1000_1011;cin_b=32'h0000_0001;cin=1'b1;

@(posedge clk) cin_a = 32'h1000_0111;cin_b=32'h0000_0001;cin=1'b1;

repeat(10) @(posedge clk);

$finish;

end

always #5 clk = ~clk;

add32_4 a(cin_a,cin_b,rst,clk,stop,cin,cout,sum);

endmodule

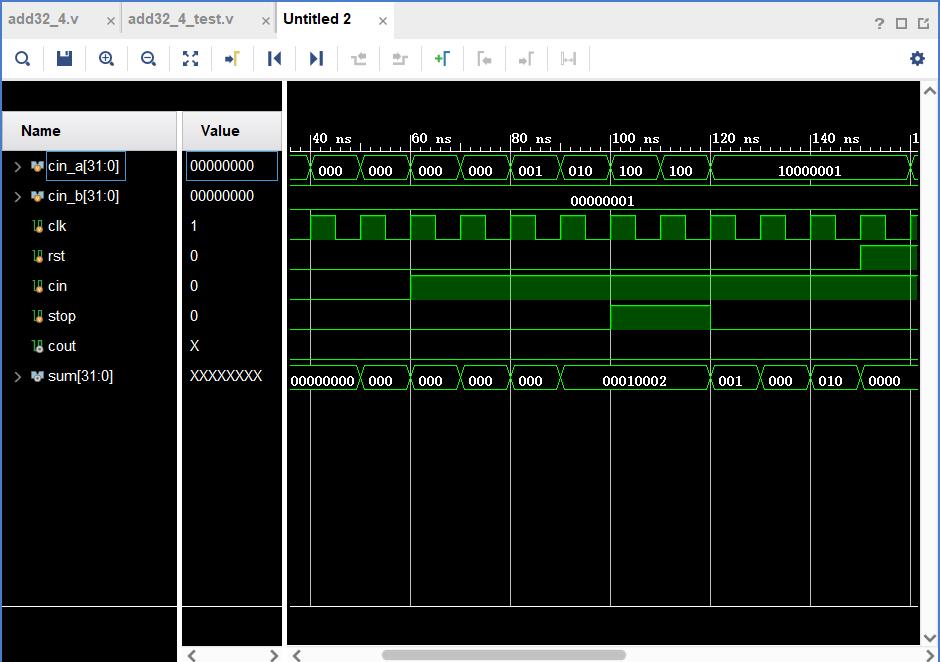

仿真结果

以上是关于实验:4级流水线32bits全加器的主要内容,如果未能解决你的问题,请参考以下文章