实验六 移位寄存器及其应用

Posted 毛_三月

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了实验六 移位寄存器及其应用相关的知识,希望对你有一定的参考价值。

目录

一、预习要求

1、复习有关寄存器的内容,弄懂移位寄存器工作的基本原理。

2、查阅74LS194(或CC40194)的有关资料,熟悉其逻辑功能及引脚排列。

3、绘出实验内容的详细电路图,并拟出实验所需的测试记录表格。

二、实验目的

1、掌握中规模4位双向移位寄存器的逻辑功能测试和使用方法。

2、学会移位寄存器的应用,如实现数据的串/并转换、构成环形计数器等。

三、实验原理

1、移位寄存器

寄存器是一种用于寄存在二进制数码或指令的时序逻辑部件,它被广泛地应用于各类数字系统和数字计算机中。其功能是在时钟脉冲的作用下,将数码或指令存入寄存器(写入),或从寄存器中将数码或指令取出(读出)。寄存器只能短时存放数据,电路失电数据便消失,故又称暂存器。存取数据的方式有串行和并行两种,寄存器按功能不同可分为:①数码寄存器:数码寄存器一般由多位D触发器或D锁存器构成,也可由JK触发器构成,其数码的输入和输出都是并行的,且只能存放数据而没有移位功能;②移位寄存器:移位寄存器是一个具有移位功能的寄存器,由触发器连接组成同步时序电路,每个触发器的输出端连接到下一级触发器的控制输入端,所有触发器共用一个时钟脉冲源,寄存器中所存的代码能够在移位脉冲的作用下依次左移或右移。既能左移又能右移的称为双向移位寄存器,只需要改变左右移的控制信号便可实现双向移位要求。根据寄存器存取信息的方式不同分为:串入串出、串入并出、并入串出、并入并出四种形式。

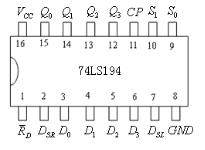

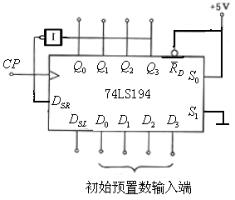

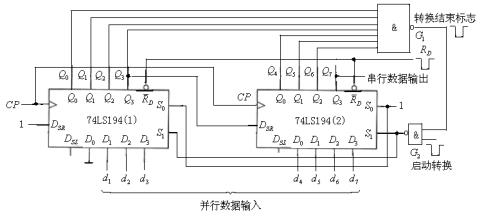

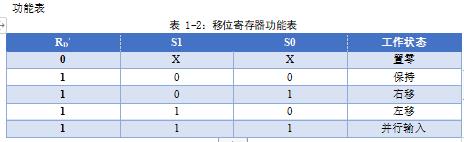

本实验选用4位双向移位寄存器74LS194,它的最高时钟频率为36MHz。它具有清零、左移、右移、预置数(并入/并出)和保持功能,其引脚排列如图1所示,功能表如表1。

图1 74LS194引脚排列图

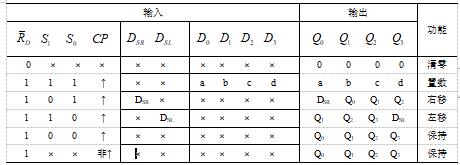

表1 74LS194的逻辑功能表

管脚符号说明:D3、D2、D1、D0 :并行数据输入端;Q3、Q2、Q1、Q0:并行数据输出端;DSR :右移串行输入端;DSL :左移串行输入端;S1、S0:工作模式控制端;:直接清零端;CP:时钟脉冲输入端。

由功能表可知:当=0时,寄存器清零使输出Q0 Q1 Q2 Q3=0000,=1时,寄存器正常工作;当=1,S1S0=11时,且在CP上升沿作用下,并行输入数据送入寄存器,使得Q0 Q1 Q2 Q3=D0D1D2D3=abcd,此时串行数据(DSR、DSL)被禁止;当=1,S1S0=01时,串行输入数据送至右移输入端DSR,在CP上升沿作用下,同步右移,即Q0 Q1 Q2 Q3=DSR Q0 Q1 Q2,Q3串行输出;当=1,S1S0=10时,串行输入数据送至左移输入端DSL,在CP上升沿作用下,同步左移,即Q0 Q1 Q2 Q3= Q1 Q2Q3 DSL,Q0串行输出;当=1,S1S0=00时,在CP上升沿作用下,寄存器内容保持不变;当=1,S1S0=××时,在CP非上升沿作用下,寄存器内容也保持不变。

2、移位寄存器的应用

移位寄存器的应用很广,可构成移位寄存器型计数器、顺序脉冲发生器和串行累加器;可用作数据转换,即把串行数据转换为并行数据,或把并行数据转换为串行数据等。

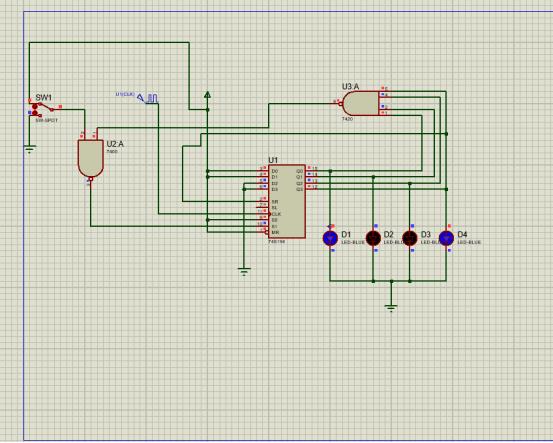

(1)用74LS194构成环形计数器

把移位寄存器的末级触发器的Q输出反馈到它的串行输入端,就可以构成环形计数器。

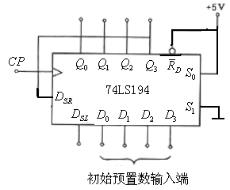

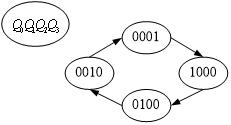

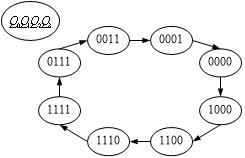

图2是将74LS194的Q3端接到DSR端,即可得模为4的右移环形计数器。首先预置数,假设D0D1D2D3=0001,在循环前,先使S1S0=11,让预置数并行进入寄存器,使得输出Q0Q1Q2 Q3=D0D1D2D3=0001,然后改变S1、S0的电平,使S1S0=01,此时在有效脉冲作用下Q0Q1Q2 Q3将依次右移,其输出状态变化如图3所示。图2所示电路的各个输出端的输出脉冲是在时间上有先后顺序脉冲,因此也可以作为顺序脉冲发生器。

图2 模4环形计数器 图3 输出状态变化图

若将图2中的Q3输出端通过反相器连接到DSR端,则可得到模为8的右移扭环形计数器,其电路如图4所示,输出状态变化如图5所示。Q输出端通过不同的组合电路接到DSR端,还可以得到不同模值的计数器或伪随机序列发生器。

(2)用74LS194实现数据串行/并行转换

①串行/并行转换器

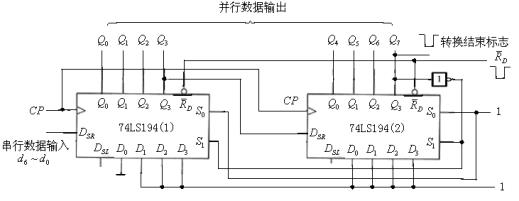

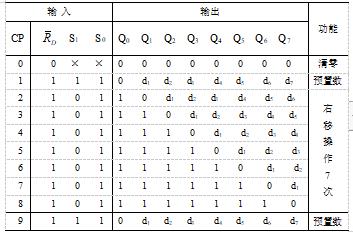

串行/并行转换是指串行输入的数据,经过转换电路之后变成并行数据输出。图6所示电路是用两片74LS194构成的七位串行/并行数据转换电路。

图4 模8扭环形计数器 图5 输出状态变化图

图6 7位串行/并行转换电路

其中:电路中S0端接高电平1,S1受Q7控制,两片寄存器连接成串行输入右移工作方式。Q7是转换结束标志。当Q7=1时,S1为0,使之成为S1S0=01的串入右移工作方式。当Q7=0时,

S1为1,且有S1S0=11,表示串行送数结束,标志着串行输入数据已转换成为并行输出数据。

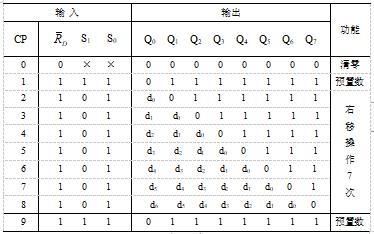

表2 7位串行/并行转换电路输出状态变换表

串行/并行转换的详细过程如下:

转换开始前端加低电平,使芯片(1)和(2)两寄存器被清零,此时S1S0=11,寄存器执行并行输入工作方式。当第一个有效脉冲到来后,寄存器的输出状态Q0~Q7被置数为01111111,与此同时S1S0变为01,转换电路变为执行串入右移工作方式,串行输入数据由芯片(1)的DSR端加入。假设输入数据为d6d5d4d3d2d1d0,则随着CP脉冲的依次加入,输出状态的变化如表2所示。

由表2可知,右移操作7次后,Q7变为0,S1S0变为11,表明串行输入结束。此时,串行输入数据已经转换成为并行数据,从Q0~Q6端输出。

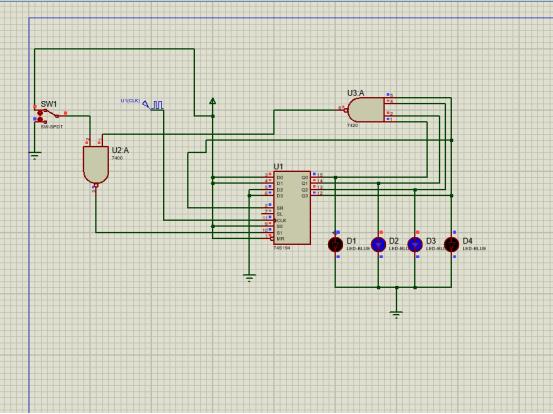

②并行/串行转换器

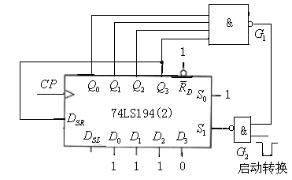

并行/串行转换是指并行输入的数据,经过转换电路之后变成串行输出。图7所示电路是用两片74LS194构成的七位并行/串行数据转换电路,与图6相比,它多了两个与非门,而且还多了一个启动信号(负脉冲或低电平),工作方式同样为右移。

图7 7位并行/串行转换电路

表3 7位并行/串行转换电路输出状态变换表

并行/串行转换的详细过程如下:

转换开始前 端加低电平,使芯片(1)和(2)两寄存器被清零,清零后,当启动转换负脉冲到来时,使得S1S0=11,此时寄存器执行并行输入工作方式。当第一个有效脉冲到来后,寄存器的输出状态Q0~Q7被置数为0d1d2d3d4d5d6d7,并行输入数据存入寄存器,同时使得门G1输出为1,门G2输出为0,S1S0变为01,转换电路变为执行右移串行操作,随着CP脉冲的依次加入,输出状态依次右移,使串行输出Q7端的输出数据依次为d7d6d5d4d3d2d1,待右移操作7次后,Q0~Q6的状态均为高电平1,使得门G1输出为低电平0,门G2输出为高电平1,此时S1S0变为11,表明并行/串行结束。7位并行/串行转换电路的输出状态变换详见表3所示。

端加低电平,使芯片(1)和(2)两寄存器被清零,清零后,当启动转换负脉冲到来时,使得S1S0=11,此时寄存器执行并行输入工作方式。当第一个有效脉冲到来后,寄存器的输出状态Q0~Q7被置数为0d1d2d3d4d5d6d7,并行输入数据存入寄存器,同时使得门G1输出为1,门G2输出为0,S1S0变为01,转换电路变为执行右移串行操作,随着CP脉冲的依次加入,输出状态依次右移,使串行输出Q7端的输出数据依次为d7d6d5d4d3d2d1,待右移操作7次后,Q0~Q6的状态均为高电平1,使得门G1输出为低电平0,门G2输出为高电平1,此时S1S0变为11,表明并行/串行结束。7位并行/串行转换电路的输出状态变换详见表3所示。

对于中规模的集成移位寄存器,其位数往往以4位居多,当所需要的位数多于4位时,可以把几片集成移位寄存器用级连的方法来扩展位数。

四、实验设备与器件

1、TH-SZ型数字系统设计实验箱;

2、双踪示波器;

3、74LS00 四2输入与非门,74LS20 双4输入与非门,74LS04 六反相器,74LS194;

4、导线/插接线若干。

五、实验内容与步骤

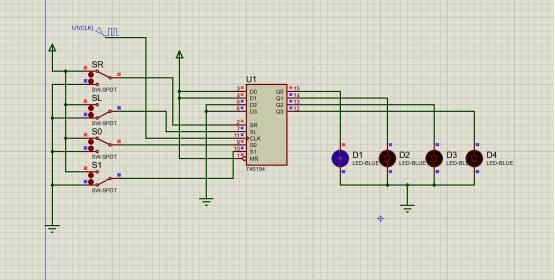

1、测试74LS194的逻辑功能

将、S1、S0、DSL、DSR、D0、D1、D2、D3分别接至逻辑开关的输出插孔;Q0、Q1、Q2、Q3分别接至逻辑电平显示输入插孔;CP接单次脉冲源。自拟表格,逐项进行测试。并与给出的功能表做对比。

移位寄存器(向右移动)

移位寄存器(向左移动)

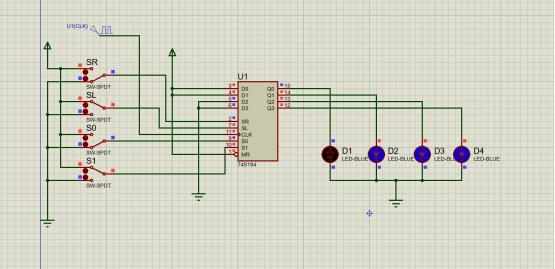

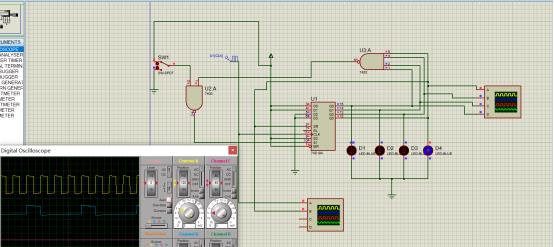

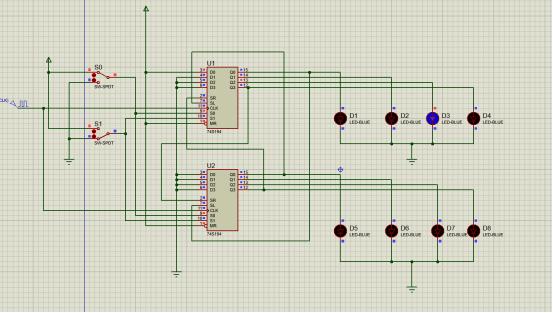

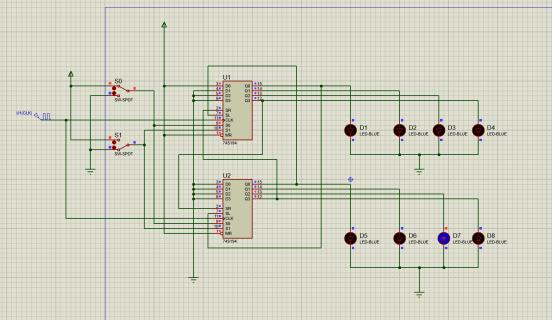

2、用74LS194和74LS20构成一个右移环形计数器(脉冲分配器)。要求:利用加在G2门上的负脉冲,使电路处于“送数”状态,设初始状态为Q0Q1Q2Q3=1110;启动信号撤出后,电路进入“右移”并保持这种模式。试按图8所示电路进行连接实验,测试环形计数器的CP与输出Q0Q1Q2Q3的计数时序及输入与各输出的波形关系,用示波器观察输入输出波形,并画出输出状态变化图和波形。CP输入为1HZ 连续脉冲,信号输出用发光二极管进行监测。

图8 环形计数器脉冲分配器

输入波形

各个输出波形

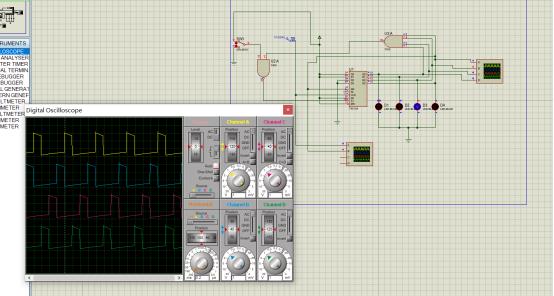

3、使用两片74LS194设计一彩灯控制电路,共有8只彩灯,使其7暗1亮(或7亮1暗)且这一亮灯(或一暗灯)循环右移,CP输入为1HZ 连续脉冲,信号输出用发光二极管进行监测。

向右移动

向左移动

六、实验报告要求

1、分析实验结果,总结移位寄存器74LS194的逻辑功能。

2、根据实验内容,画出相关实验连接电路,记录各测试结果,画出环形计数器状态转换图及所观察到的有关实验波形。

更多相关文章点这里哦

以上是关于实验六 移位寄存器及其应用的主要内容,如果未能解决你的问题,请参考以下文章