FPGA综合实验 03 - | 8位硬件乘法器设计

Posted Neutionwei

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了FPGA综合实验 03 - | 8位硬件乘法器设计相关的知识,希望对你有一定的参考价值。

一、实验目的和任务

1、学习应用移位相加原理设计8 位乘法器。

2、了解移位相加原理构成乘法器与用组合逻辑电路直接设计的同样功能的

电路优势。

二、设计代码(或原理图)、仿真波形及分析

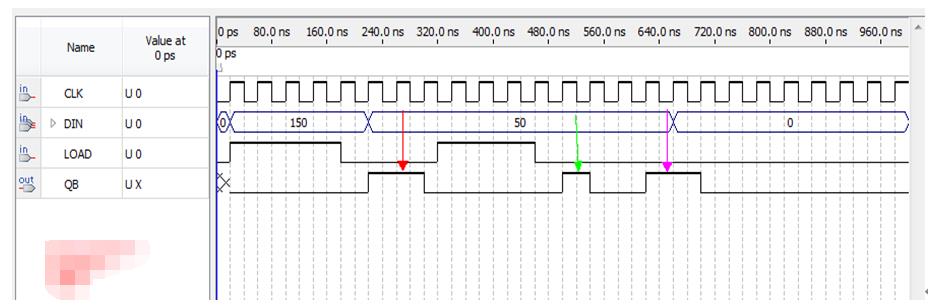

1、SREG8BT的仿真图及分析

如图所示,当给LOAD高电平之时,该8位移位寄存器把DIN中的150(二进制为10010110)读入寄存器然后当给LOAD低电平的之后的CLK上升沿,输出QB为0(150的第0位),在红色剪头处QB的高电平表示150第1位和第2位,绿色剪头与紫色剪头也是同理。

2、REGSHT的仿真图及分析

如图所示,在第一个上升沿之时,D=0,而在第二个上升沿,即红色剪头处的D=12,此时输出Q=1536,其二进制表示为0000 0110 0000 0000,由VerilogHDL代码可知R16S[6:0]<=R16S[7:1]即R16S[6:0] = 0,R16S[15:7] = 12,此结果与Q输出结果一致绿色剪头与紫色剪头也是同理。

如图所示,在第一个上升沿之时,D=0,而在第二个上升沿,即红色剪头处的D=12,此时输出Q=1536,其二进制表示为0000 0110 0000 0000,由VerilogHDL代码可知R16S[6:0]<=R16S[7:1]即R16S[6:0] = 0,R16S[15:7] = 12,此结果与Q输出结果一致绿色剪头与紫色剪头也是同理。

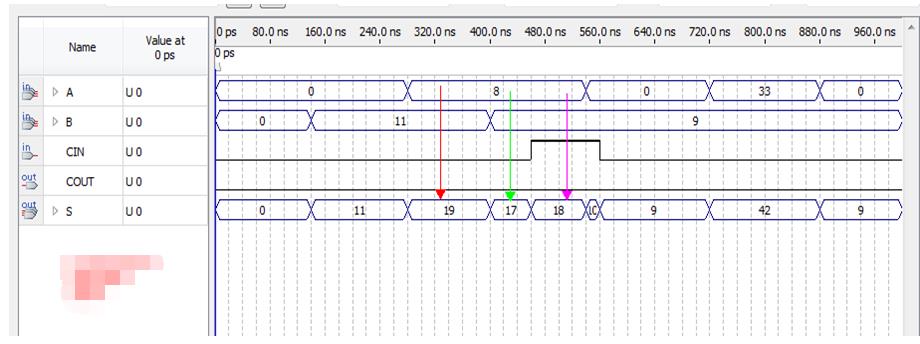

3、ADDER8BT的仿真图及分析

如图所示,红色剪头表示8+11=19,绿色剪头表示8+9=17,紫色剪头表示8+9+1=18,这说明S=A+B+CIN。

如图所示,红色剪头表示8+11=19,绿色剪头表示8+9=17,紫色剪头表示8+9+1=18,这说明S=A+B+CIN。

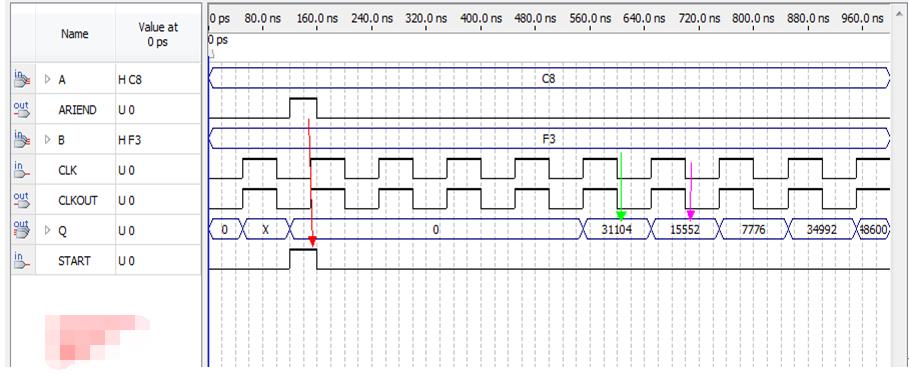

4、完整乘法器的仿真图及分析

如图所示,红色剪头表示外部按键START按下(给SREG8BT的LOAD高电平)时给ARIEND一个高电平输出,绿色剪头处的Q为31104,而31104<<1结果为0xF300,此处最高位为0xF3,即相乘的结果为0xF3,这里表示B的数值0xF3乘以A的数值0xC8第4位再加上前3位的结果,因为前3位相乘后的结果为0,因此这里相乘的结果为0xF3,紫色剪头也是同理。

如图所示,红色剪头表示外部按键START按下(给SREG8BT的LOAD高电平)时给ARIEND一个高电平输出,绿色剪头处的Q为31104,而31104<<1结果为0xF300,此处最高位为0xF3,即相乘的结果为0xF3,这里表示B的数值0xF3乘以A的数值0xC8第4位再加上前3位的结果,因为前3位相乘后的结果为0,因此这里相乘的结果为0xF3,紫色剪头也是同理。

以上是关于FPGA综合实验 03 - | 8位硬件乘法器设计的主要内容,如果未能解决你的问题,请参考以下文章