实验五 触发器及其应用

Posted 毛_三月

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了实验五 触发器及其应用相关的知识,希望对你有一定的参考价值。

目录

一、实验预习要求

1、复习触发器的相关内容,掌握触发器的各种表示方法及逻辑功能。

2、理解各触发器之间的相互转换原理。

3、掌握由JK 触发器转换成D 触发器、T 触发器、T’触发器的基本方法。

二、实验目的

1、掌握本RS、JK、D和T触发器的逻辑功能及测试方法,了解它们的触发方法。

2、熟悉常用集成触发器的型号及外引脚排列。

3、熟悉触发器之间相互转换的方法。

4、掌握和熟练应用各种集成触发器。

5、学会用JK 和D触发器构成简单时序逻辑电路的方法。

三、实验原理

触发器是一个具有记忆功能的二进制信息存储器件,是组成时序电路的最基本单元,也是数字电路中另一种重要的单元电路,它在数字系统和计算机中有着广泛的应用。触发器具有两个稳定状态,用以表示逻辑状态“1”和“0”,在一定的外界信号作用下,可以从一个稳定状态翻转到另一个稳定状态。触发器有集成触发器和门电路组成的触发器。按其逻辑功能分,有RS触发器,JK触发器,D触发器,T触发器,T’触发器等。

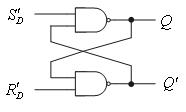

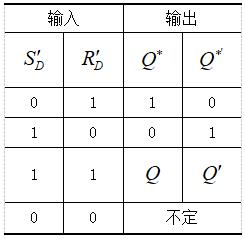

1、基本SR触发器

图5.1为由两个与非门交叉耦合构成的基本SR触发器,这是无时钟控制低电平直接触的触发器。它有两个输出端、和两个输入端、,输入信号名称的小标“D”,表示输入信号直接(Direct)控制触发器的输出。通常称为置“1”端,因为()时触发器被置“1”; 为置“0”端,因为()时触发器被置“0”,当时状态保持;当时,触发器状态不定,应避免此种情况发生。基本SR触发器的

图5.1基本SR触发器 表5.1基本RS 触发器的特性表

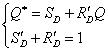

特性表如表5.1所示,它具有置“0”、置“1”和“保持”三种功能,其特性方程为

式中, 是约束条件,它表示两个输入端不允许同时为0(至少一个为1)。

是约束条件,它表示两个输入端不允许同时为0(至少一个为1)。

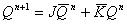

2、集成JK触发器

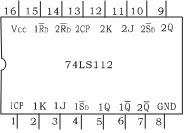

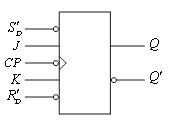

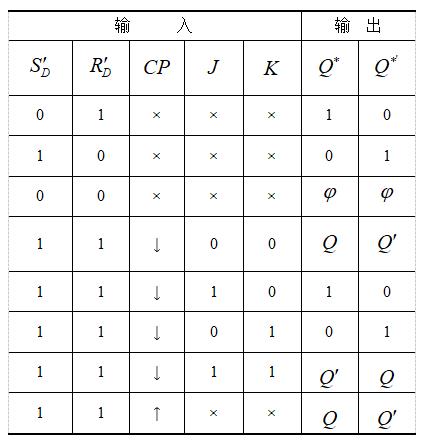

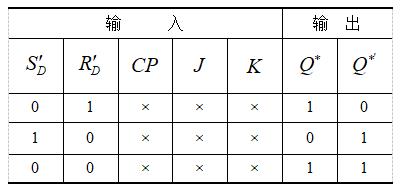

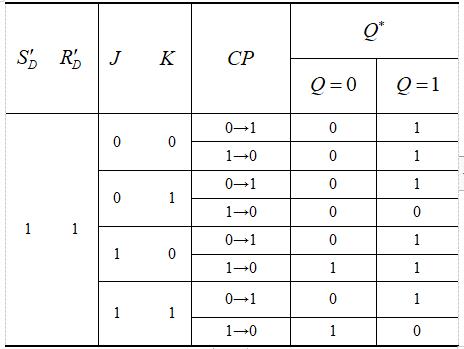

集成JK触发器有主从结构和边沿结构两种类型,本实验采用的是TTL型中速边沿结构的双下降沿JK触发器74LS112,其引脚排列及逻辑符号如图5.2。在图5.2逻辑符号图中,CP输入端加小圆圈代表低电平有效、小三角代表边沿触发,即在时钟脉冲CP的后沿(负跳变)发生翻转,它具有置0、置1、计数和保持功能,其特性表如表5.2所示。JK触发器的特性方程为

图5.2双JK触发器74LS112引脚排列及逻辑符号图

表5.2集成JK触发器74LS112功能表

另外,JK触发器和D触发器一般都有异步置位端,低电平有效。异步复位端,低电平有效,其作用是可预置触发器的初始态。和的优先权高于J、K和CP,当不使用时,必须接高电平(或接到电源+5V上),不允许悬空,否则容易引入干扰信号,使触发器误动作,GND为接地端。JK触发器常被用作缓冲存储器,移位寄存器和计数器。

3、集成D触发器

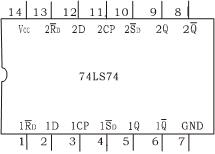

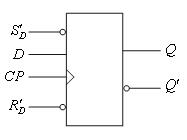

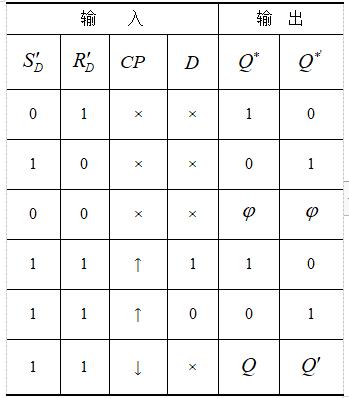

本实验采用的是集成双D触发器74LS74,其引脚排列及逻辑符号如图5.3。在图5.3中,D为输入端,、为输出端,为时钟脉冲输入端。为异步置位端,低电平有效。为异步复位端,低电平有效。和的优先权高于D和CP,当不使用时,必须接高电平(或接到电源+5V上),不允许悬空,否则容易引入干扰信号,使触发器误动作,GND为接地端。这种D触发器的输出状态更新发生在脉冲的上升沿,故又称为上升沿触发的边沿触发器,触发器的状态只取决于时钟到来前输入端D的状态,其特性方程为

D触发器的应用很广,可用作数字信号的寄存,移位寄存,分频和波形发生等。

图5.3双D触发器74LS74引脚排列及逻辑符号图

表5.3集成D触发器74LS74功能的表

4、T触发器和T’触发器

T触发器具有计数和保持功能,T’触发器具有计数功能,它们可以通过D触发器或JK触发器转换来实现。D触发器的D端与Q’端相连即构成T’触发器,在时钟脉冲CP的前沿(正跳变)发生翻转。利用下降沿JK触发器在其JK两端都接1时即成为T’触发器,在时钟脉冲CP的后沿(负跳变)发生翻转。

四、实验设备与器件

1、TH-SZ型数字系统设计实验箱;

2、74LS00 四2输入与非门,74LS112 双下降沿JK触发器,74LS74 双上升沿D触发器,74LS08 四2输入与门;

3、导线/插接线若干。

五、实验内容与步骤

1、集成JK触发器的逻辑功能测试

(1)测试 、的复位、置位功能

从下降沿触发的集成双JK触发器74LS112上任取一只JK触发器,其中 、、 、端接十六位逻辑电平开关的输出插口(任选其中四个开关输出插口即可),端接单次脉冲源,输出端和接十六位逻辑电平显示的输入插口(任选其中两个输入插口即可),

接实验箱上的+5V电源,接实验箱上的地。要求在或时任意改变 、及的状态,将测试结果记录在表5.4中。

表5.4 JK触发器的复位、置位功能测试实验记录表

(2)测试JK触发器的逻辑功能测试

按表5.5的要求改变 、、端的状态,观察和状态变化,观察触发器状态更新是否发生在脉冲的下降沿(即由1→0),并将测试结果记录在表5.5中。

表5.5 JK触发器的逻辑功能测试表

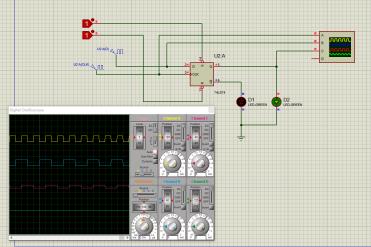

(3)将JK触发器的J、K端连在一起,作为一个输入端构成触发器。

在CP端输入1KHz连续脉冲,在端加入500Hz的连续脉冲信号,通过分析试画出、、、端的波形,注意其相位关系。

黄线接的是CLK,频率为1000HZ;蓝线接的是D,频率为500HZ,周期为黄线的二倍;红线接的是Q,周期为蓝线的二倍。

2、集成D触发器的逻辑功能测试

(1)测试 、

、 的复位、置位功能

的复位、置位功能

测试方法同实验内容2、(1),自拟表格并记录测试结果。

(2)测试D触发器的逻辑功能

按表4.5要求进行测试,并观察触发器状态更新是否发生在CP脉冲的上升沿(即由0→1),并将测试结果记录在表4.5中。

表4.5 D触发器的逻辑功能测试表

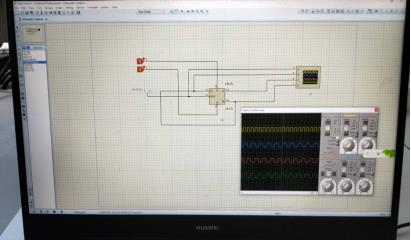

(3)将D触发器的端与D端相连接,构成T’触发器。

测试方法同实验内容2、(3),并绘出相关波形。

黄线接是CLK,频率1000HZ;蓝线接的是D,周期为黄线的二倍

3、触发器的应用

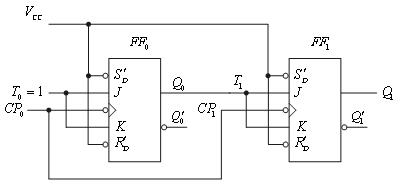

用JK触发器组成二分频和四分频电路。

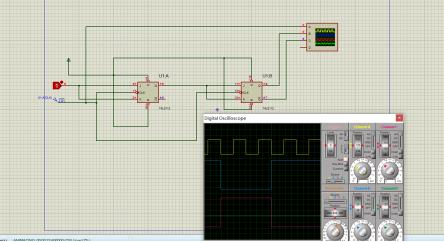

下图4.8所示是将两个JK 触发器分别接成T’和T触发器后进行连接组成二分频和四分频电路,即第一个JK触发器的J、K端连在一起接高电平“1”,第二个JK 触发器的J、K 端连接在一起,接到第一个JK 触发器的输出端Q,输入1kHz 的方波,用示波器分别观察和记录CP0、Q0、Q1 的波形,理解二分频,四分频的概念。

六、实验报告要求

1、列写D触发器、JK触发器的逻辑功能及应用测试结果。

2、绘出观测到的对应波形,并说明触发器的触发方式。

3、体会触发器的应用。

4、整理实验记录,并对结果进行分析。

更多相关文章点这里哦

以上是关于实验五 触发器及其应用的主要内容,如果未能解决你的问题,请参考以下文章