FPGA开发入门

Posted badman250

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了FPGA开发入门相关的知识,希望对你有一定的参考价值。

关于FPGA

具体概念不展开,本章主要是偏实践。

-

- 相比GPU

FPGA(现场可编程逻辑阵列),是可反复编程的数字电路。ASIC是专用集成电路,一旦设定完成就无法更改功能和性能。FPGA适用于小批量、定制化、实时性要求高的应用。

峰值性能:FPGA<GPU

灵活性:FPGA>>GPU

功耗:GPU>>FPGA

-

- 开发流程

FPGA的开发流程总体按照下图进行。

- 设计输入

- 创建工程,添加设计源文件,如原理图等

- 设计综合

- 约束输入

- 指定时序、布局布线等

- 设计仿真

- 设计实现

- 分析实现结果

- 设计优化

- 板级调试

-

-

- 细化到工具

-

写代码(编写源文件 Add or Create Design Sources)

看电路(查看原理图 Schematic)

写仿真(新建仿真文件 Add or Create Simulation Sources)

跑仿真(仿真分析Run Simulation)

加约束(添加引脚/时序约束文件 Add or Create Constraints)

跑综合(设计综合 Run Synthesis)

跑实现(设计实现 Run Implementation)

看资源(综合/实现资源 Report Utilizatioin)

看时序(综合/实现时序 Report Timing Summary)

看功耗(综合/实现功耗 Report Power)

比特流(生成比特流文件 Generate Bitstream)

跑板子(下载比特流文件到 FPGA:Program Device)

在Altera开发流程中,编译、映射过程合称综合,而在Xilinx开发流程中,由设计输入得到门级网表的过程叫做综合,而映射过程归结到其叫做实现的步骤中。

约束在综合和布局布线这两个流程环节里都出现了,规定其为约束一和约束二,或者说综合约束和布局布线约束,布局布线约束又可以分为位置约束、时序约束。约束,就是对这些环节操作定制规则。

testbench,即测试平台,是给待验证的设计添加激励,同时观察输出响应是否符合设计要求。测试平台,测试平台在做功能仿真、静态仿真和时序仿真的时候都需要用到。

RTL级仿真,属于第一道检测,有些场合称作功能仿真,为了突出和静态仿真的区别,是对工程在寄存器转送级进行的描述时进行测试,查看其在RTL级描述的时候实现的功能的正确性。

静态仿真,也叫门级仿真,是综合后的LUT门级网表。有些开发平台下将静态仿真具体又分为编译仿真和映射仿真,静态仿真的目的就是验证工程用LUT门级网表描述的时候,从功能上检查验证工程的正确性。

时序仿真,在布局布线之后做的,布线延时问题影响到了电路的性能的时候可以做时序约束。这个延时问题的获得就可以通过时序仿真获得,还有一种获得延时出现超载情况,这个属于静态时序分析。

静态时序分析,简称STA(Static Timing Analysis),在布局布线后,会生成时序分析报告,该报告是分析工具利用从布线的路劲上提取出寄生参数后精确计算出来的。该报告中会提示出一些关键路径,所谓关键路劲就是指延时信息比较突出的信号节点流,通过分析可以得到不满足时序要求的路径。

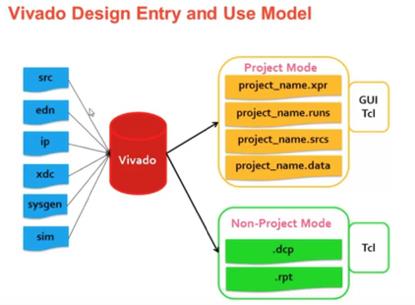

- Vivado

- vivado工具说明

Vivado Design Suite是 Xilinx 开发的用于HDL 设计的合成和分析的软件套件,具有用于片上系统开发和高级综合的附加功能。它取代了之前的Xilinx ISE。 和较新版本的ISE一样,Vivado包含了内置的逻辑仿真器ISIM。

Xilinx用Vivado Design Suite替换有15年的寿命的ISE软件,花费了1000人·年的工作时间及2亿美元。

-

- 安装

安装比州比较傻瓜式,直接使用xsetup命令即可进行安装。

在安装目录执行./install_dir/Vivado/2018.3/settings64.sh

就可以导入变量,然后直接执行vivado即可打开工具即可.

-

- 项目工程文件说明

project_name.cache:Vivado 软件的运行缓存

project_name.hw:波形文件

project_name.ip_user_files:用户关于 IP 的文件

project_name.runs:编译与综合结果,.\\impl_1 文件夹中的.bin 和 .bit 即为编译生成的可执行文件

project_name.sdk:SDK 环境代码,一般是 ZYNQ 设计中关于 PS 端的代码

project_name.sim:仿真结果

project_name.srcs:所有用户编写的源码、仿真文件与约束文件

project_name.tmp:自制 IP 核时的临时工程文件夹,IP 核设计完成后会自动清理。

- Helloworld

- 创建项目

1.创建项目选择RTL Project。(芯片 XCVU9P-L2FLGB2104E,机型上是该型号FPGA卡即是xcvu13p-fhgb2104-2L-e)

2.点击Create Block Design按钮来添加原理图设计文件。

更具需要添加IP。

3.右键选择bd文件,在弹出的菜单中选择Generate Output Products。

4.右键选择sysetm在弹出的框框中选择Create HDL Wrapper。

5.然后点击Generate Bitstreams(图形按钮)

如果是一个.v文件,选择"Part_1_Sim" 文件,取消synthesis 和Implementation ,只保留 Simulation 。

可以直接创建.V文件来设计,也可以.V和BLOCK DESIGN一起设计。

v文件内容:

module top(

input clk;

output reg clk_dev2

);

always@(posedge clk) begin

clk_dlv2 <= ~clk_div2;

end

endmodule

约束文件xdc如下:

set property PACKAGE_PIN AY23 [get_ports clk]

set property PACKAGE_PIN AT22 [get_ports clk_div2]

set property iosTANDARD LVCMOS18 [get_ports clk]

set property IOSTANDARD LVCMOS18 [get_ports clk_div2]

然后就可以:RTL编译,综合,跑实现。

最后通过tools中转换为bin文件即可。

-

- 添加文件

添加Verilog设计文件(Design Source)。

添加Verilog仿真文件(Simulation Source)。

-

- 仿真

在Flow Navigator窗口中点击Run Simulation - Run Behavioral Simulation;或者在菜单中选择Flow - Run Simulation - Run Behavioral Simulation,即可启动行为仿真。

需要添加testbench。

-

- 烧写FPGA

生成比特流文件,这个文件会被直接烧写进板子。类似于编程中的二进制可执行文件。点击Program and Debug->Generate Bitstream。或下图的上面图标即可执行生成比特流的操作。

线上的烧写准备:

(Alifpga-platform-tool/board_test目录中)

#sh reload_safe.sh 5e:00.0 5d:00.0

修改配置文件conf.dat,主要是type和firmware_ver修改,默认bin文件是top开始命名。

(Alifpga-platform-tool目录中)

#sh update_fpga_firmware.sh 5e:00.0 5d:00.0

-

- 说明

对于具有ARM处理器的Xilinx FPGA可以使用SDK工具编写C代码,经过编译之后,通过JTAG接口,将机器码输入到ARM处理器中,控制其运行。

使用Vivado工具,创建自己的工程,可以使用Vivado的Block Design设计方式,导入Zynq处理器,PL部分的可编程逻辑可选可不选。

之后Export Hardware。如果生成了位流文件,则需要勾选Include Bitstream选项,否则不需要选。

之后Launch SDK,在SDK软件下,新建application,并新建BSP,选中Helloworld模板。继而将bitstream 下载到FPGA上。在Helloworld工程处,选择Run as GDB。通过串口调试工具可以看到输出Hello world信息。

- ISE开发

激励文件通常由模块定义、信号初始化、执行模块、例化组成。

- 参考

Xilinx使用介绍

https://www.paincker.com/vivado-basic-usage-1

Xilinx软件下载,https://china.xilinx.com/products/design-tools/vitis/vitis-platform.html

Hello world tutorial vivado:https://www.youtube.com/watch?v=nUzq1KL6J-c

http://www.asic-world.com/verilog/first1.html

以上是关于FPGA开发入门的主要内容,如果未能解决你的问题,请参考以下文章

[从零开始学习FPGA编程-8]:快速入门篇 - FPGA功能开发详细流程与关键步骤解读