在FPGA中,如何实现一个时钟信号的可控延时? (用高频50MHZ的时钟去延时一个22KHZ的信号)

Posted

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了在FPGA中,如何实现一个时钟信号的可控延时? (用高频50MHZ的时钟去延时一个22KHZ的信号)相关的知识,希望对你有一定的参考价值。

22KHZ的一个同步信号,现在需要进行延时,采用FPGA的内部50MHZ时钟取实现

参考技术A 如果是FPGA的话,建议用PLL把时钟提高。然后用这个信号去采样22kHz的信号,用计数器记录信号电平改变的时间,记录相邻几次的值(总时间大于延迟时间就可以了),然后加上延时,从新计数输出。FPGA中信号的跨时钟域处理模板

一、背景

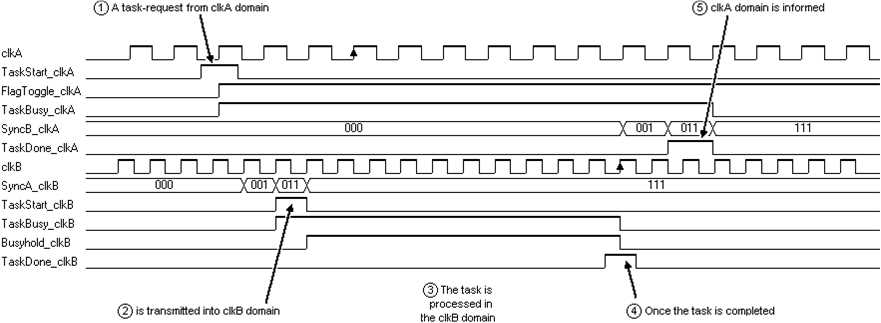

如果clk_a时钟域中的某个任务需要在clk_b时钟域中来完成。则可以采用以下设计:通过框图可知人任务的跨时钟域的处理相当于两个买冲刺你好的跨时钟域的处理。在两个标志信号跨时钟域完成后,在此期间相关任务的跨时钟域。

这只是其中的一种方法。

二、模板

模块 TaskAck_CrossDomain(

输入 clkA,

输入 TaskStart_clkA,

输出 TaskBusy_clkA,TaskDone_clkA,

输入 clkB,

输出 TaskStart_clkB,TaskBusy_clkB,

输入 TaskDone_clkB

);

reg FlagToggle_clkA,FlagToggle_clkB,Busyhold_clkB;

reg [2:0] SyncA_clkB,SyncB_clkA;

总是 @(posedge CLKA)FlagToggle_clkA <= FlagToggle_clkA ^(TaskStart_clkA&?TaskBusy_clkA);

总是 @(posedge CLKB)SyncA_clkB <= {SyncA_clkB [1:0],FlagToggle_clkA};

分配 TaskStart_clkB =(SyncA_clkB [2] ^ SyncA_clkB [1]);

分配 TaskBusy_clkB = TaskStart_clkB | Busyhold_clkB;

总是 @(posedge CLKB)Busyhold_clkB <=?TaskDone_clkB&TaskBusy_clkB;

总是 @(posedge CLKB)如果(TaskBusy_clkB&TaskDone_clkB)FlagToggle_clkB <= FlagToggle_clkA;

总是 @(posedge CLKA)SyncB_clkA <= {SyncB_clkA [1:0],FlagToggle_clkB};

分配 TaskBusy_clkA = FlagToggle_clkA ^ SyncB_clkA [2];

分配 TaskDone_clkA = SyncB_clkA [2] ^ SyncB_clkA [1];

终端模块

三、仿真波形

以上是关于在FPGA中,如何实现一个时钟信号的可控延时? (用高频50MHZ的时钟去延时一个22KHZ的信号)的主要内容,如果未能解决你的问题,请参考以下文章