FPGA中信号的跨时钟域处理模板

Posted lgy-gdeu

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了FPGA中信号的跨时钟域处理模板相关的知识,希望对你有一定的参考价值。

在做项目的时,我们经常会使用到多个时钟。每一个时钟在FPGA内部都会形成一个时钟域,如果一个时钟域中要用到另外一个时钟域的信号,也就形成了跨时钟域的操作,这时候要格外小心。

一、实际使用背景

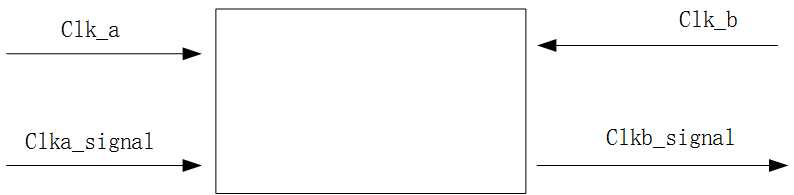

假设在项目中需要在clk_b时钟域中用到用到来自clk_a中的信号。那么此信号就需要从clk_a时钟域跨越到clk_b中因此我们要建立一个同步计数器,该设计器从clk_a 中获取信号,然后再clk_b中创建一个新的信号。并从作为输出。模型如下:

在此设计中、我们假设输入的信号与clk_a和clk_b相比变化缓慢,那么需要做的就是使用两个触发器将信号从clk_a转移到clk_b。

二、模板

模块 Signal_CrossDomain( 输入 clkA,//在该示例中我们实际上不需要clkA,但这是出于完整性的考虑,因为在其他示例中将需要它, 输入 SignalIn_clkA, 输入 clkB, 输出 SignalOut_clkB ); //我们使用两级移位寄存器将SignalIn_clkA同步到clkB时钟域 reg [1:0] SyncA_clkB; 总是 @(posedge CLKB)SyncA_clkB [0] <= SignalIn_clkA; //注意,我们使用CLKB 总是 @(posedge CLKB)SyncA_clkB [1] <= SyncA_clkB [0]; //注意,我们使用clkB 分配 SignalOut_clkB = SyncA_clkB [1]; //同步到新的信号(=准备中使用)CLKB域 endmodule

三、分析

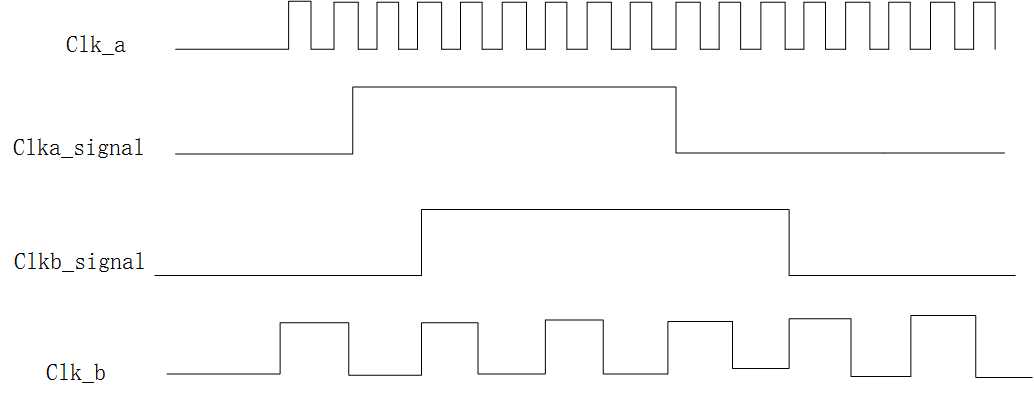

这两个触发器具有延迟信号的副作用,例如在一下波形中,可以看到俩个触发器将慢速运动的信号同步或者说是延迟到clk_b时钟域中。其实这种方法我们在同时钟域中也用过,经常用来数据对齐。

以上是关于FPGA中信号的跨时钟域处理模板的主要内容,如果未能解决你的问题,请参考以下文章