FPGA之时钟规划图解

Posted 知识充实人生

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了FPGA之时钟规划图解相关的知识,希望对你有一定的参考价值。

目录

一、前言

对于vivado这类使用verilog语言的进行工程设计的工具,软件的时钟规划设计是至关重要的一个环节,下面将针对软件时钟规划的设计原理进行一些基础的说明,了解这个也能提高自己程序设计的可靠性,以及问题定位,本文以xilinx的xc7z100ffg900-2器件为例。

二、时钟规划概念

广泛的来说,时钟规划包含了布局,布线流程,布局是将时钟单元在满足设计的要求下放置于可放置的位置,布线是在布局的基础下进行时钟模块间的线路连接。

三、时钟规划的模块

3.1 时钟BUF

常见的时钟单元有全局时钟缓冲器BUFG、水平时钟缓冲器BUFH、区域时钟缓冲器BUFR、IO时钟缓冲BUFIO、跨区域时钟缓冲器BUFMR

BUFG:驱动的时钟范围为整个芯片,通常位于芯片的中央位置;

BUFH:驱动的范围为同水平方向相邻的两个时钟区域,通常位于芯片中央的垂直方向上按区域分布;

BUFR:驱动单个时钟区域的时钟,通常在每个时钟区域内部都有;

BUFMR:驱动垂直方向上相邻的两个时钟区域,通常位于左右两侧区域分界的位置;

IO:只能用于驱动和IO相关的时钟;

3.2 时钟源

对于时钟BUF,如果没有时钟源,将是毫无意义的。FPGA中的时钟源从本质来说都是来源于外部的,通过clk pad输入进来,clk pad位置可在IO Planning中查看,即site_type带SRCC或MRCC的IO,在右侧的Layers中勾选SRCC和MRCC,如下图所示,左侧红色方框中灰白色的IO即为clk pad,即时钟输入端口。

对于输入的时钟,可通过PLL(锁相环)进行分频,倍频,调整相位或占空比生成更多的时钟信号,PLL在每个存在clk pad的区域都有分布,下图红色菱形标注的即为PLL的位置。

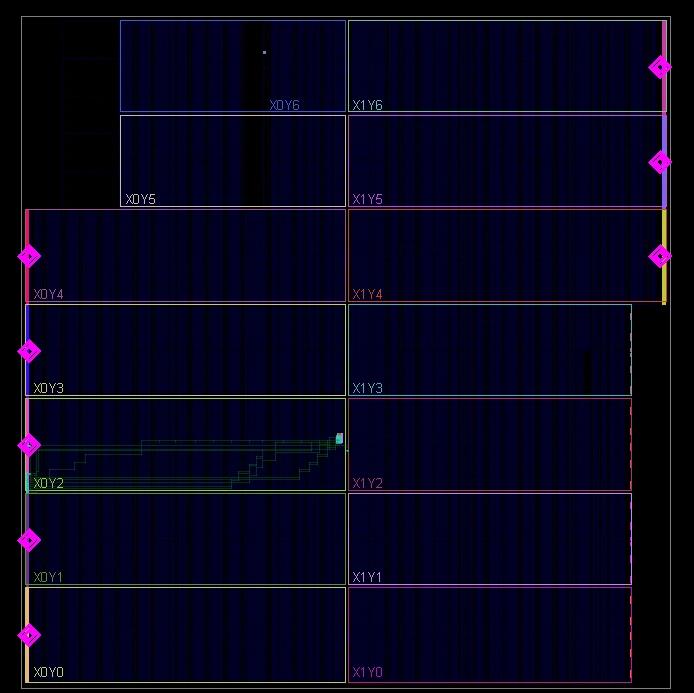

四、时钟规划之时钟单元布局

根据芯片不同时钟缓冲器的驱动范围不同,划分为不同的时钟区域,进入“window->Device”,查看时钟区域划分,如下图,图中共有14个时钟区域,每个区域的范围为对应方框的范围,每个时钟区域的边界用不同颜色的线条来进行区分,每个方框内如X0Y6为时钟区域的坐标。

时钟区域划分图

4.1 BUFG

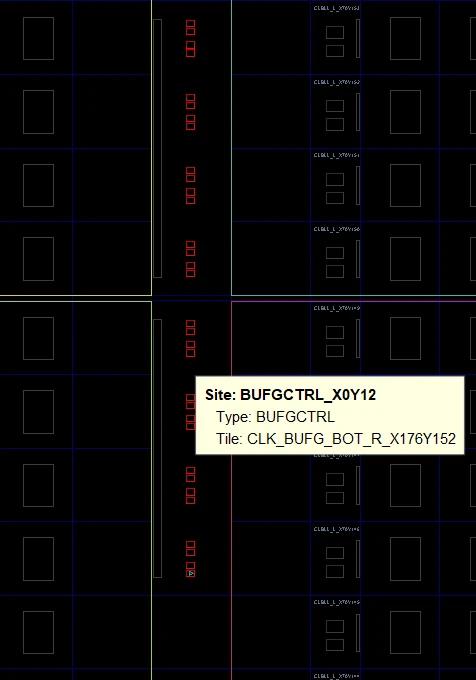

在device的中间位置,可以看到bufg是垂直分布的,每个红色小方格为一个bufg,共32个,并且BUFG不属于任何一个时钟区域。

BUFG分布图

4.2 BUFH

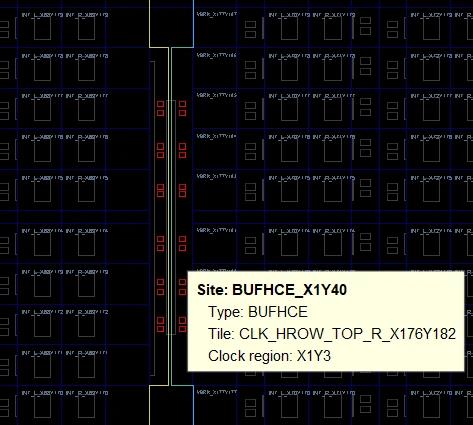

在芯片中间垂直方向,BUFH分为左右两列,每列各12个,每列的驱动范围为邻近的时钟区域。

BUFH分布图

下图为上图针对BUFH位置放大图,可看出左右两个时钟区域的分界线是将左右两列的BUFH包含进去了。

BUFH归属区域

4.3 BUFR

图中选定的四个白色小方块位置即为BUFR的位置,左侧的AD28/AE28是IO 的位置,每个时钟区域都有4个BUFR

BUFR分布图

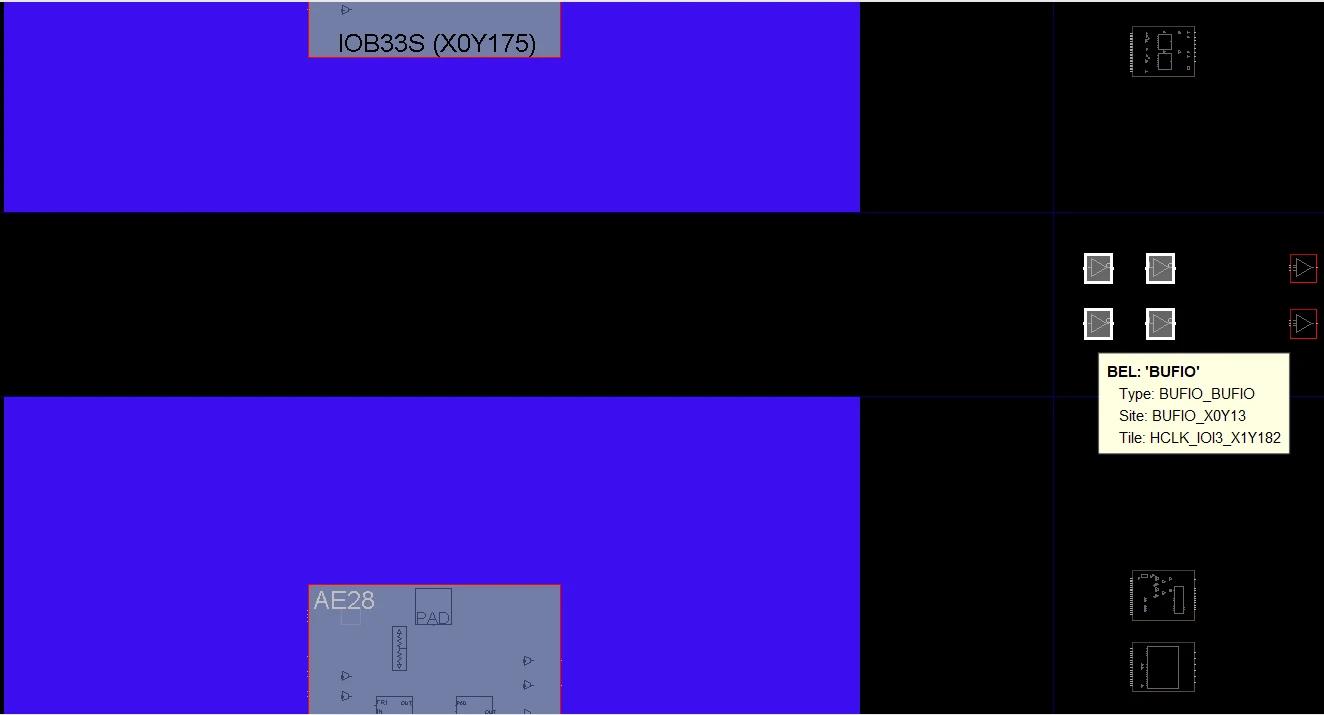

4.4 BUFIO

下图四个白色方框的位置即为BUFIO,在其右侧的红色小方框为BUFR

BUFIO分布图

在整个芯片范围内,如下图用粉红色菱形标注的为BUFIO的分布位置,每个区域4个BUFIO,7个区域共28个BUFIO

BUFIO全局分布图

五、时钟规划之时钟单元走线

5.1 BUFG->BUFH

大体的时钟驱动方向为BUFG->BUFH->SWITHBOX->时钟端口,Switchbox是芯片上的布线资源,下图即为BUFG通过BUFH驱动FF的图

BUFG驱动FF

5.2 BUFR->FF

BUFR驱动FF

5.3 BUFIO->FF

BUFIO可直接通过时钟路径驱动FF的clk端口

BUFIO驱动FF

FPGA技巧篇四FPGA设计的四种常用思想与技巧之四 :数据同步化

欢迎大家关注我的微信公众账号,支持程序媛写出更多优秀的文章

1 输入数据同步化的原则

(1)如果输入数据的节拍和本级芯片的处理时钟同频,可以直接用本级芯片的主时钟对输入数据寄存器采样, 完成输入数据的同步化;

(2)如果输入数据和本级芯片的处理时钟是异步的,特别是频率不匹配的时候,则只有用处理时钟对输入数据做同步化处理,才能完成输入数据的同步化。

2 同步化方式

复位:

异步复位同步释放

数据:

1. 单比特数据:打两拍进行同步

2. 多比特数据:2.1 采用握手机制保证数据稳定

2.2 RAM 或 FIFO

3 详述

数据打两拍的方法

需要说明的是,用寄存器对异步时钟域的数据进行两次采样,其作用是有效防止亚稳态 ( 数据状态不稳定 ) 的传播,使后级电路处理的数据都是有效电平。但是,这种做法并不能保证两级寄存器采样后的数据是正确的电平,这种方式处理一般都会产生一定数量的错误电平数据。所以仅仅适用于对少量错误不敏感的功能单元。

为了避免异步时钟域产生错误的采样电平,一般使用 RAM 、 FIFO 缓存的方法完成异步时钟域的数据转换。最常用的缓存单元是 DPRAM ,在输入端口使用上级时钟写数据,在输出端口使用本级时钟读数据,这样就非常方便的完成了异步时钟域之间的数据交换。

把数据存放在 RAM 或 FIFO 的方法

将上级芯片提供的数据随路时钟作为写信号,将数据写入 RAM 或者 FIFO ;然后使用本级的采样时钟将数据读出来即可。

这种做法的关键是数据写入 RAM 或者 FIFO 要可靠。

如果使用同步 RAM 或者 FIFO ,就要求应该有一个与数据相对延迟关系固定的随路指示信号,这个信号可以是数据的有效指示,也可以是上级模块将数据打出来的时钟。

对于慢速数据,也可以采用异步 RAM 或者 FIFO ,但是不推荐这种做法。

以上是关于FPGA之时钟规划图解的主要内容,如果未能解决你的问题,请参考以下文章

我想问一下 我的FPGA开发板晶振 是50m(外部时钟) 我想用50m作为我fpga设计电路的时钟 是直接把这个外部