Cadence画版图时改变全部金属层

Posted

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了Cadence画版图时改变全部金属层相关的知识,希望对你有一定的参考价值。

参考技术A 1.实现功能在使用Cadence画版图时,需要大面积铺金属层地,那么有了第一层金属框架后,在铺第二层金属会不会又简便的方法呢?也就是从左边变化成右边,而不需要自己一个个的去改变呢?

2.实现方法

第一步:打开需要改变金属层的layout文件。

第二步:Crtl+A,全选整个版图,然后点击小写Q

第三步:点击M1drw,变成M2drw。

第四步:选择右上角的【Common】,将其点亮。会弹出窗口,选择【YES】

第五步:将【AS IS】改变成【M2drw】。

第六步:然后点击OK,即可将所有金属层转换成另一层金属。

集成电路版图设计

文章目录

前言

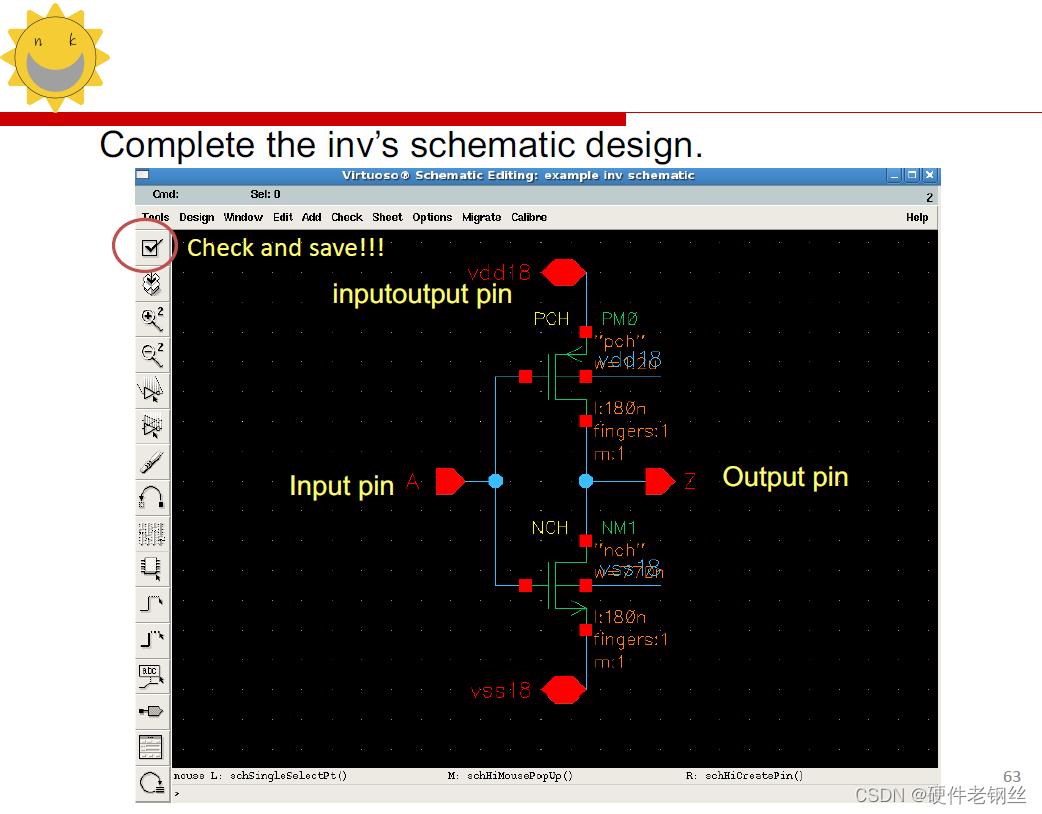

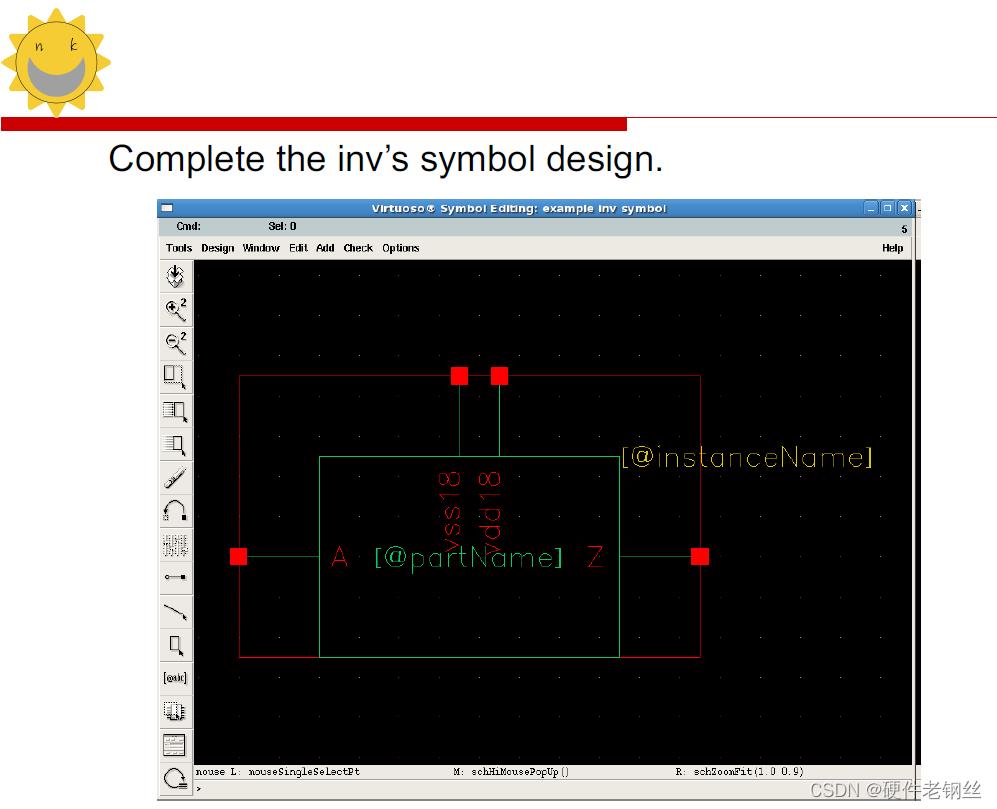

只会设计电路而对版图设计没有详细的认知是不行的,因此开始学习版图知识。

提示:以下是本篇文章正文内容,下面案例可供参考

一、版图设计的介绍

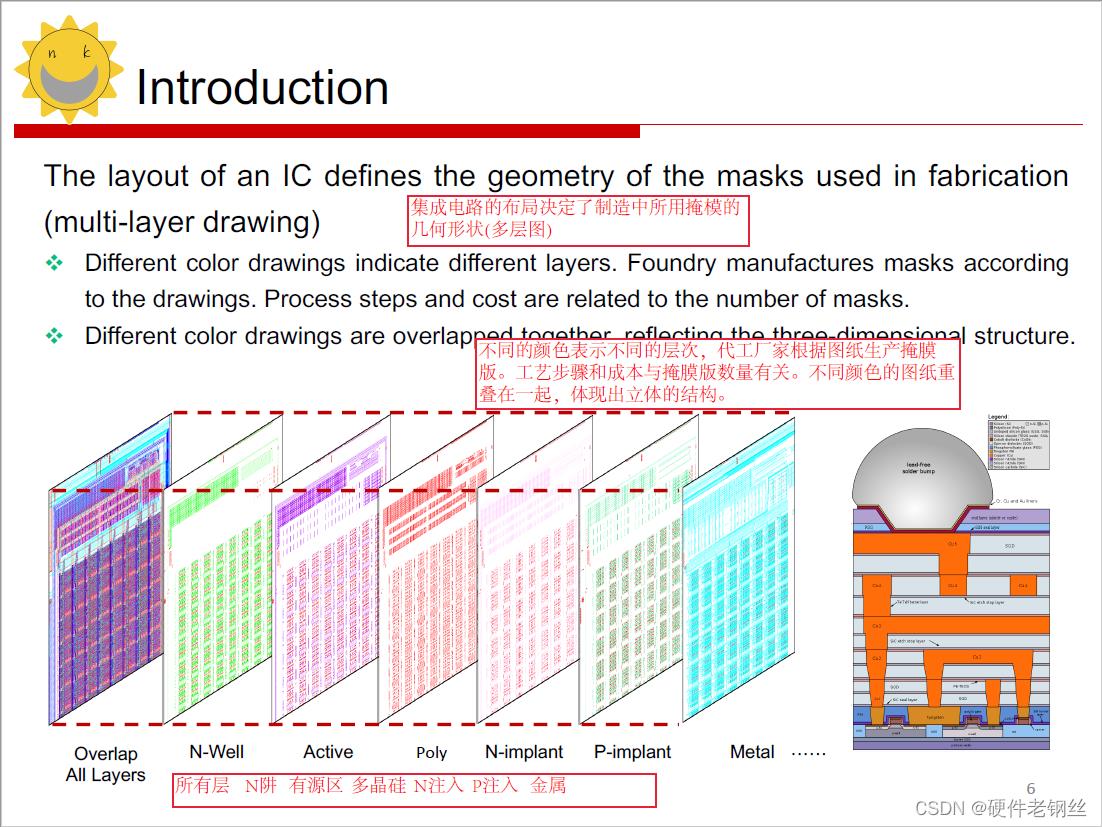

介绍

集成电路或单片集成电路(也被称为IC、芯片或微芯片)是在半导体材料(通常是硅)的一个小平面上的一组电子电路。大量微小的mosfet(金属氧化物半导体场效应晶体管)集成到一个小芯片中。

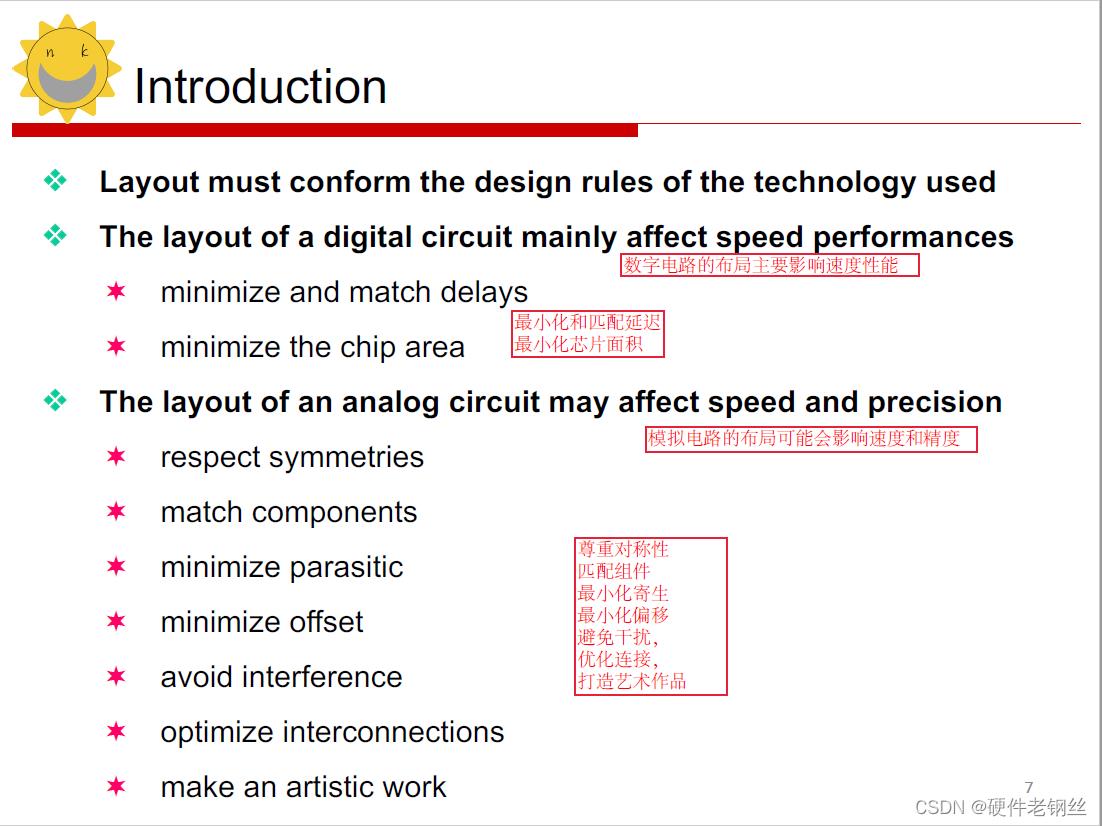

数字电路和模拟电路布局的要求

数字电路杂乱无章,主要关注面积。

模拟电路要充分考虑匹配、寄生,所以看着比较规整。

流片过程

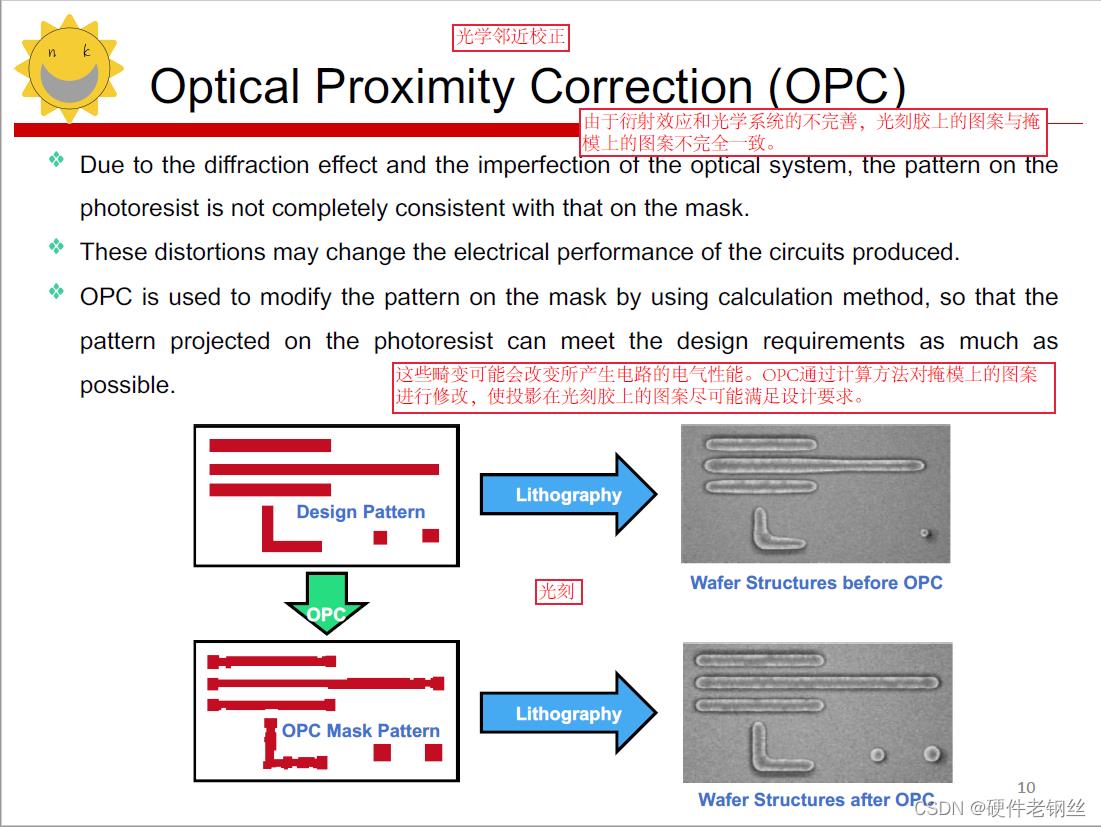

OPC技术(光学邻近矫正)

数字集成电路设计流程

模拟集成电路设计流程

绘制版图需要的

二、MOS管的流片流程

MOS管尺寸指数

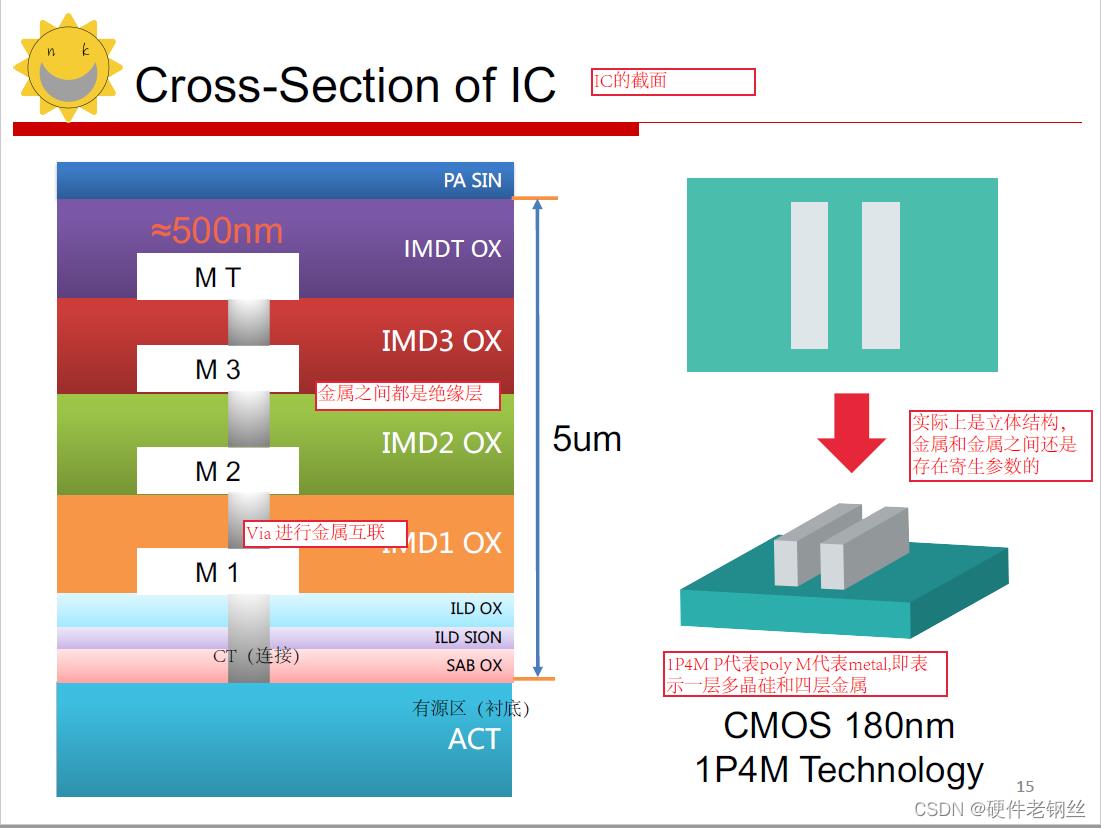

1P4M芯片构成

流片工艺立体图

流片的简单过程

三、流片的实际设计过程

1、N阱光刻

2、氧化层刻蚀

3、N阱注入

4、氮化硅奠基

5、有源区光刻

6、氮化硅光刻

7、生产场氧层

8、薄的栅氧化层生长

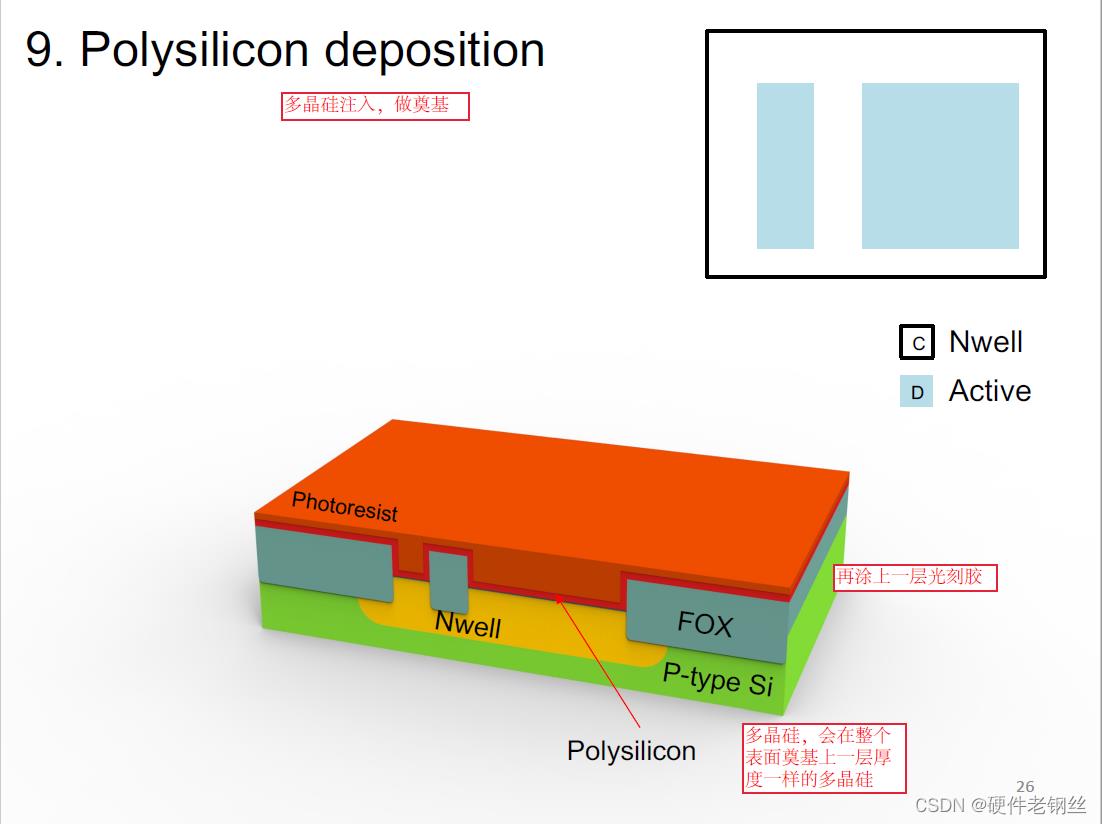

9、多晶硅注入做奠基

10、栅极光刻

11、多晶硅刻蚀

进行多晶硅刻蚀,就可以留下我们需要的栅极部分,并最后洗掉光刻胶

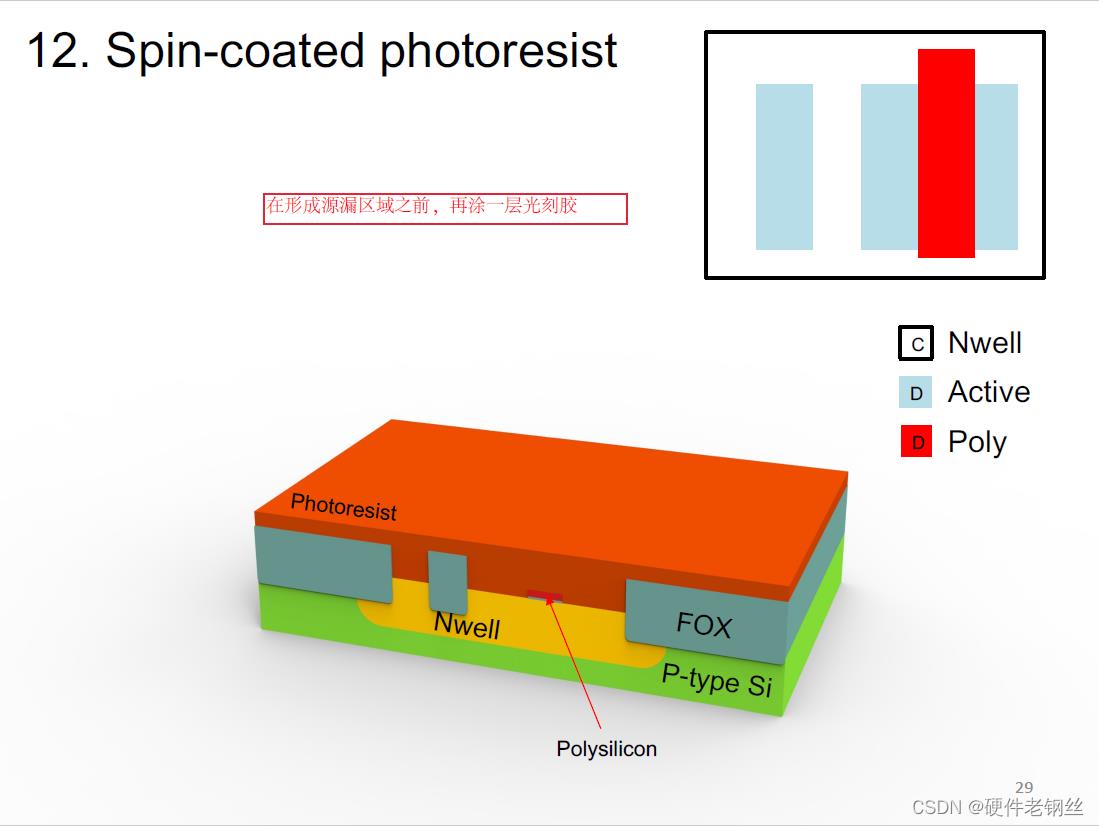

12、形成源漏区准备

在形成源漏区之前,要进行衬底接触的设计,以保证后期电位的上拉和接地。

先涂一层光刻胶。

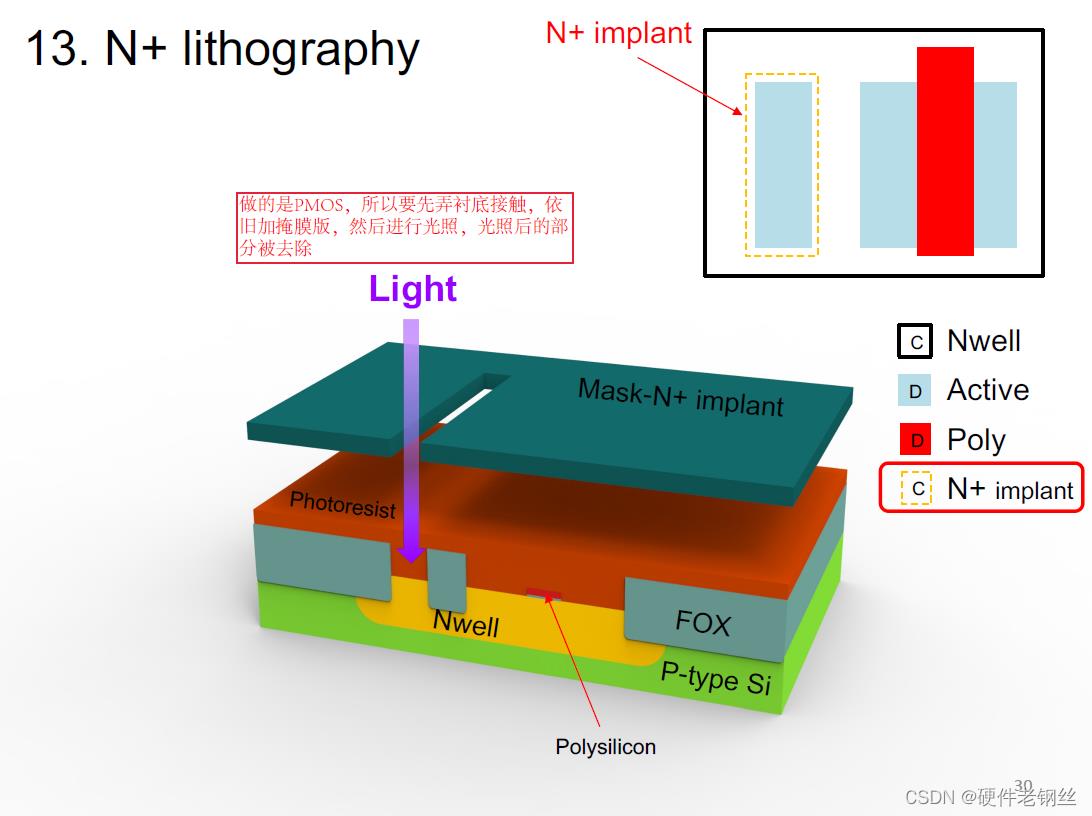

13、N+光刻

添加掩膜版进行光照,空缺的部分被去除,其余部分得到了保留。

14、N+注入

全范围N+离子注入,只有刚才光刻去除的部分可以打入,其余部分都被挡住,不会进行注入,至此,便形成了N+的衬底接触。从右上角图可以看到版图的平面结构示意图。

15、N+区完成

在N+完成注入后,清除掉多余的光刻胶,便要开始进行之后的源漏区设计。

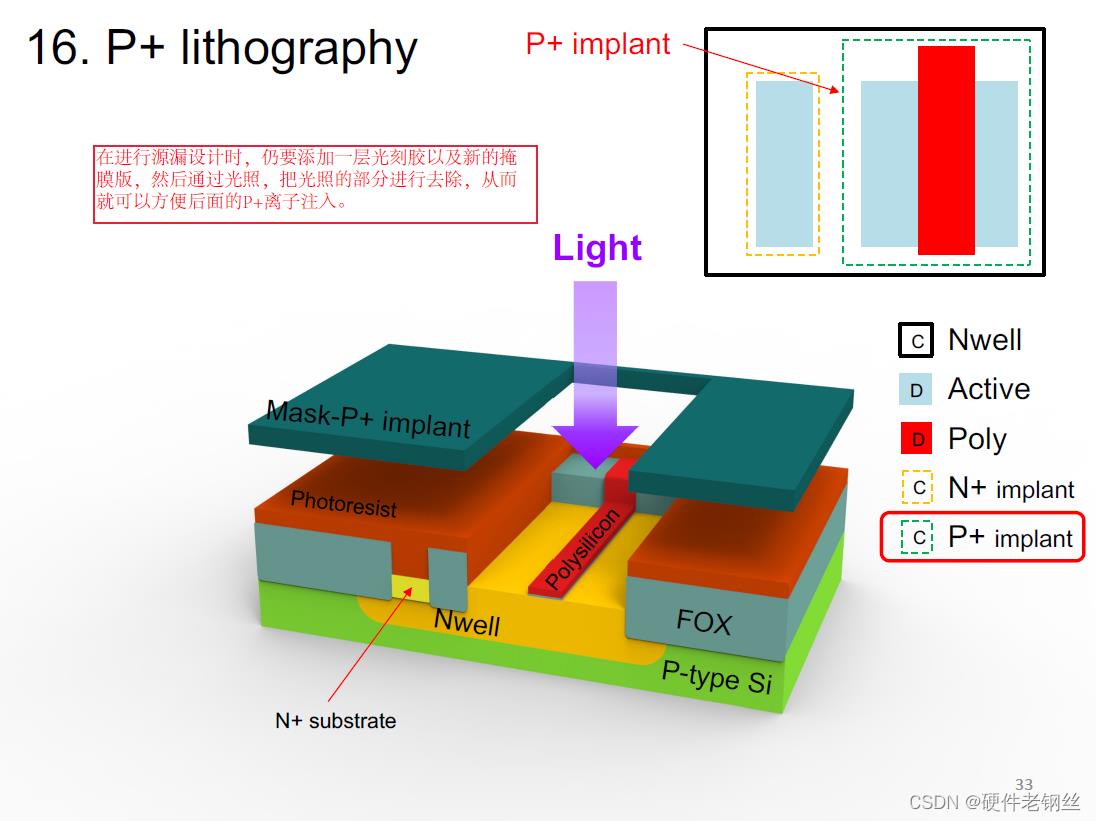

16、P+区光刻

为了实现PMOS,我们需要在N阱内进行P+的离子注入来形成PMOS的源漏区,同样涂上光刻胶,然后用一块新的掩膜版进行光刻(至此已经用了5块掩膜版)。

17、P+区注入

全范围P+离子注入,没有被光刻胶隔离和栅极多晶硅隔离的部分可以直接P+注入。

18、P+衬底形成(注入完全)

至此,在清洗掉光刻胶之后,栅源漏都形成,还有衬底接触部分,也就是B。

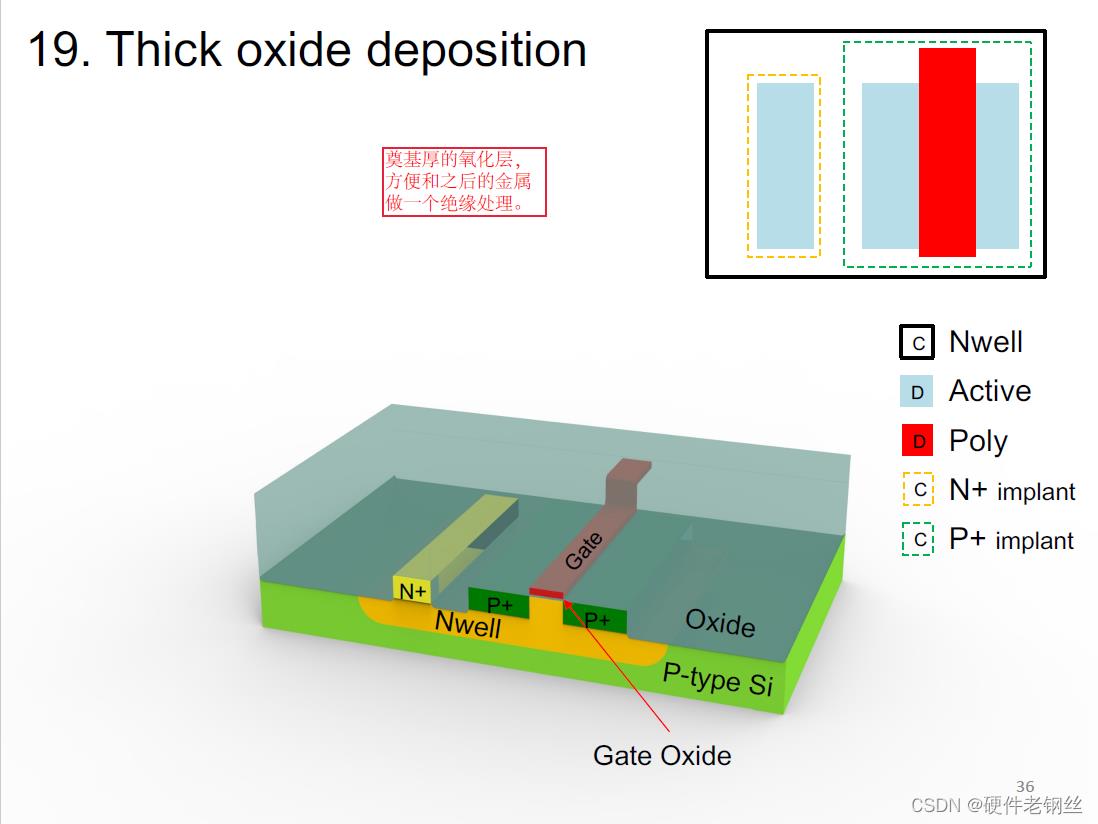

19、奠基厚的氧化层做绝缘处理

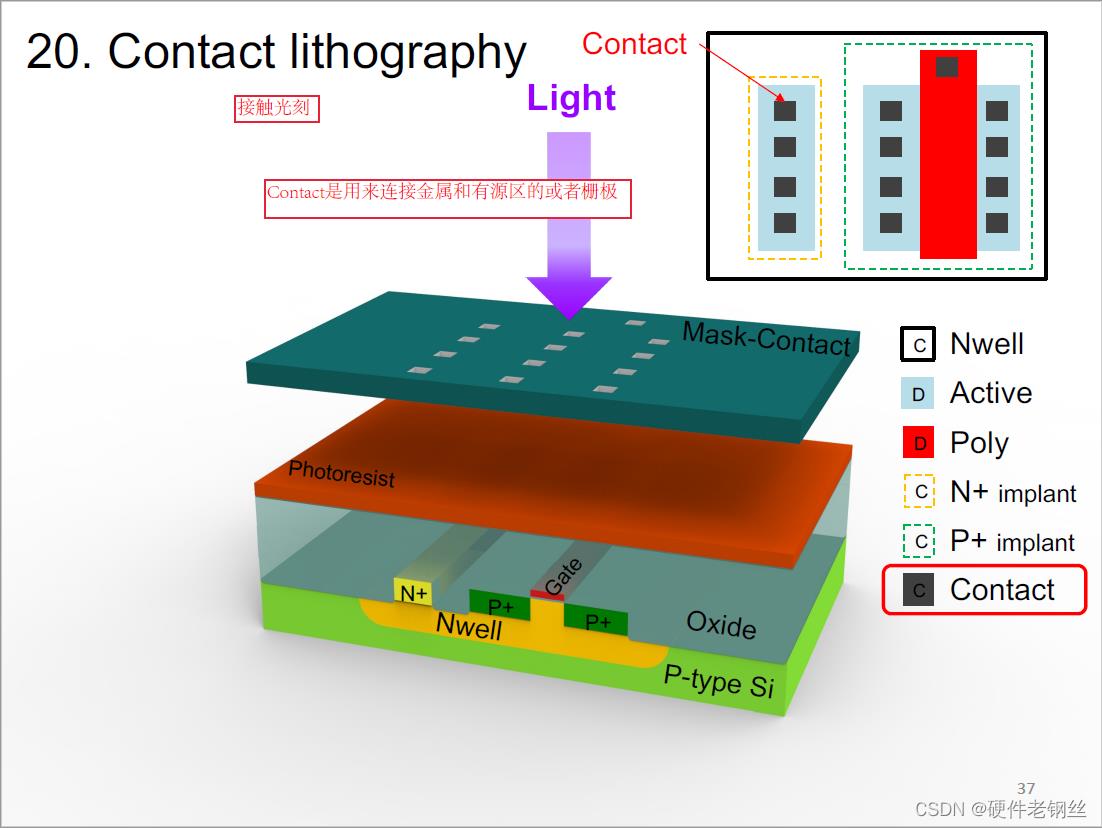

20、接触光刻

为之后的金属柱做准备,需要做Contact连接处理,涂上光刻胶,然后用新的掩膜版进行光照,中间空余的部分被留下

21、厚的氧化层光刻

光照后,就会在光刻胶上留下我们之后准备注入金属的孔洞

22、注入金属钨

在孔洞内注入金属钨当Contact,至此就将我们的四个电极,即源级S 漏极D 栅极 G 衬底B分别引出了。

23、金属一层光刻

从版图中可以看出,四个端口的外围都有了金属一·边界

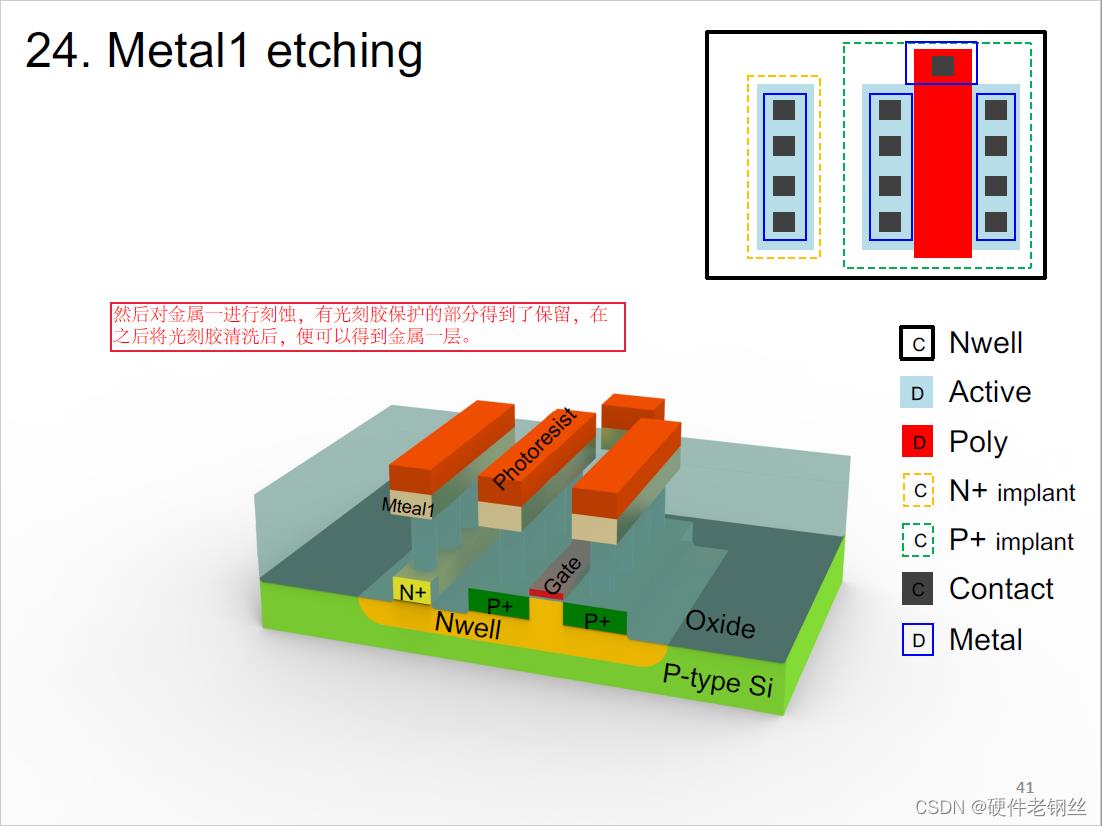

24、金属一层刻蚀

25、金属一互联

得到了PMOS管

26、多层金属互联的立体结构

四、实际案例

1、CMOS晶体管的横切片图和版图

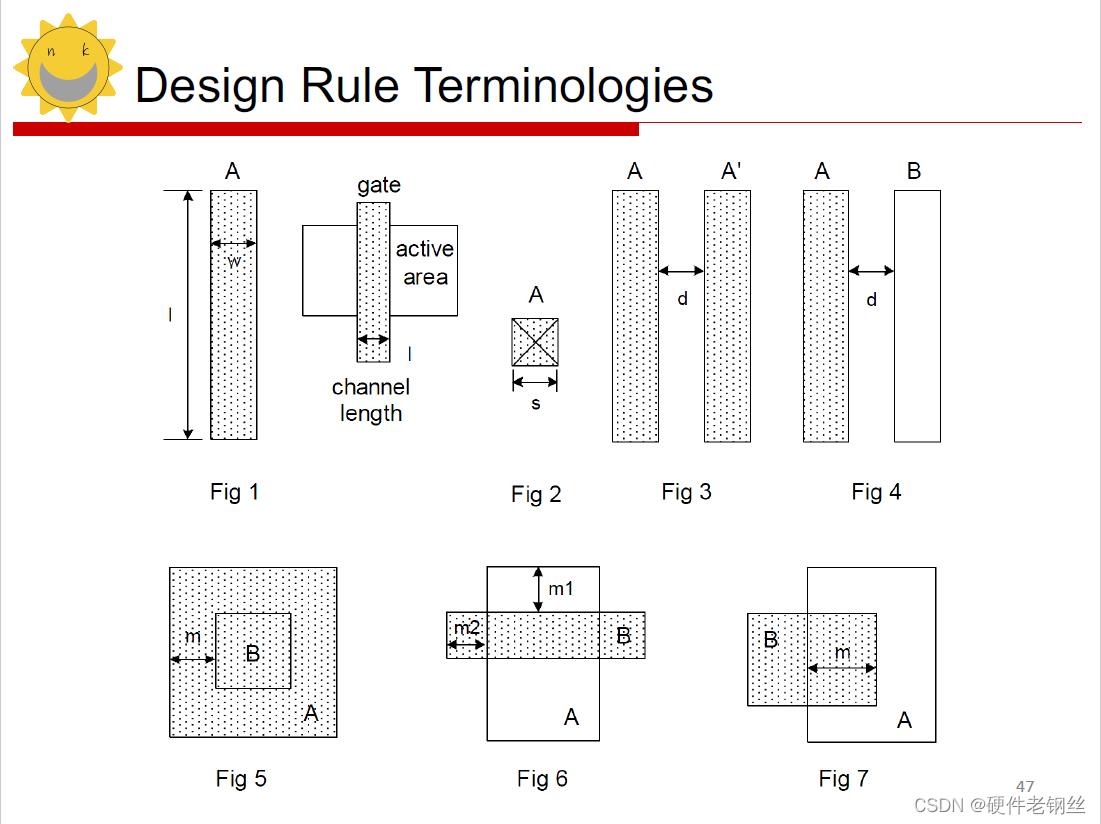

2、设计规则技术

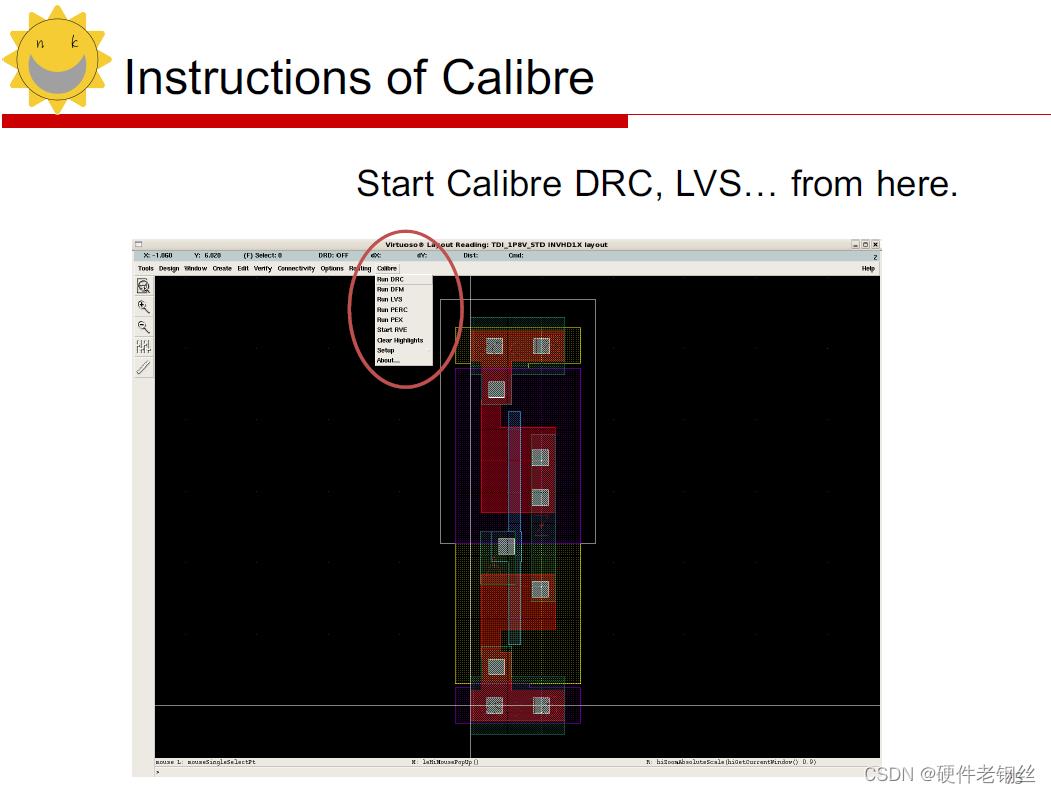

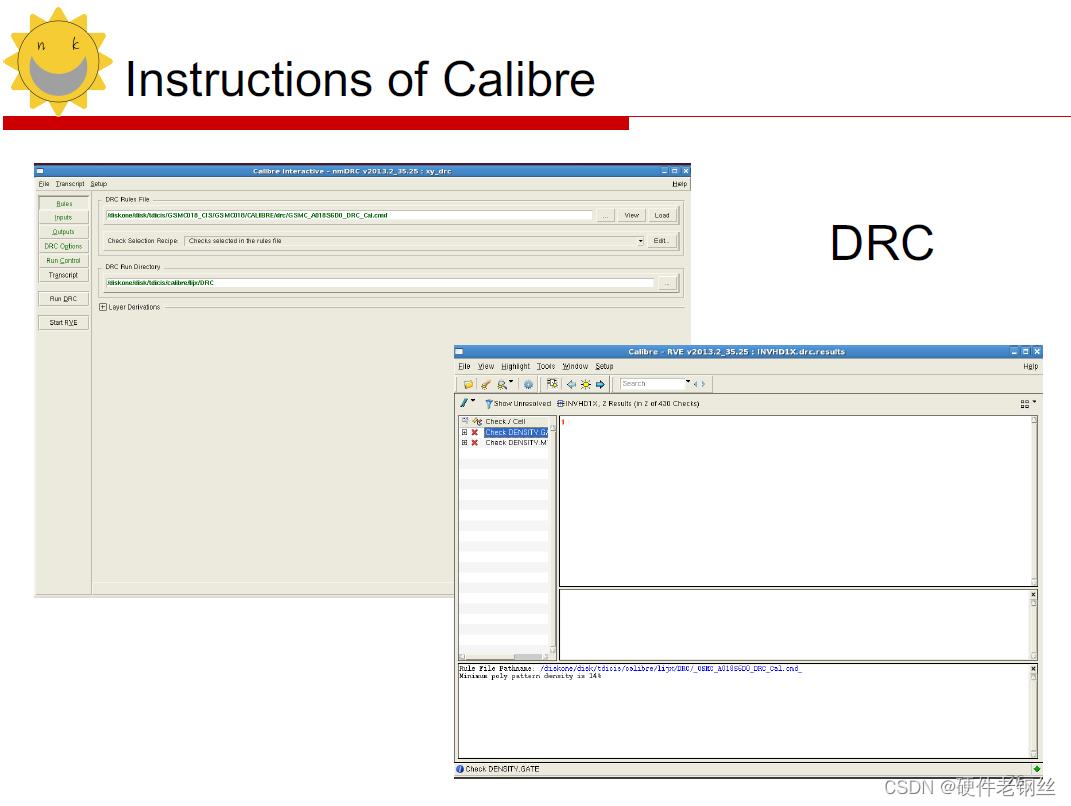

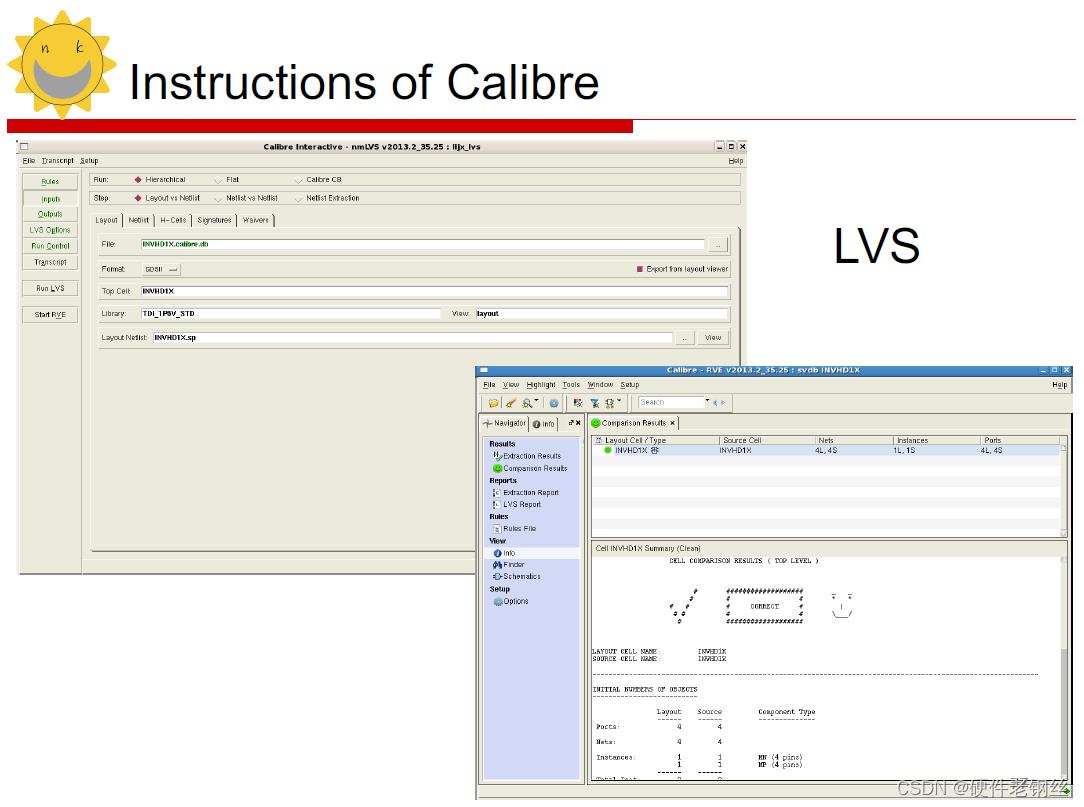

3、DRC检查和LVS

4、Post Simulation

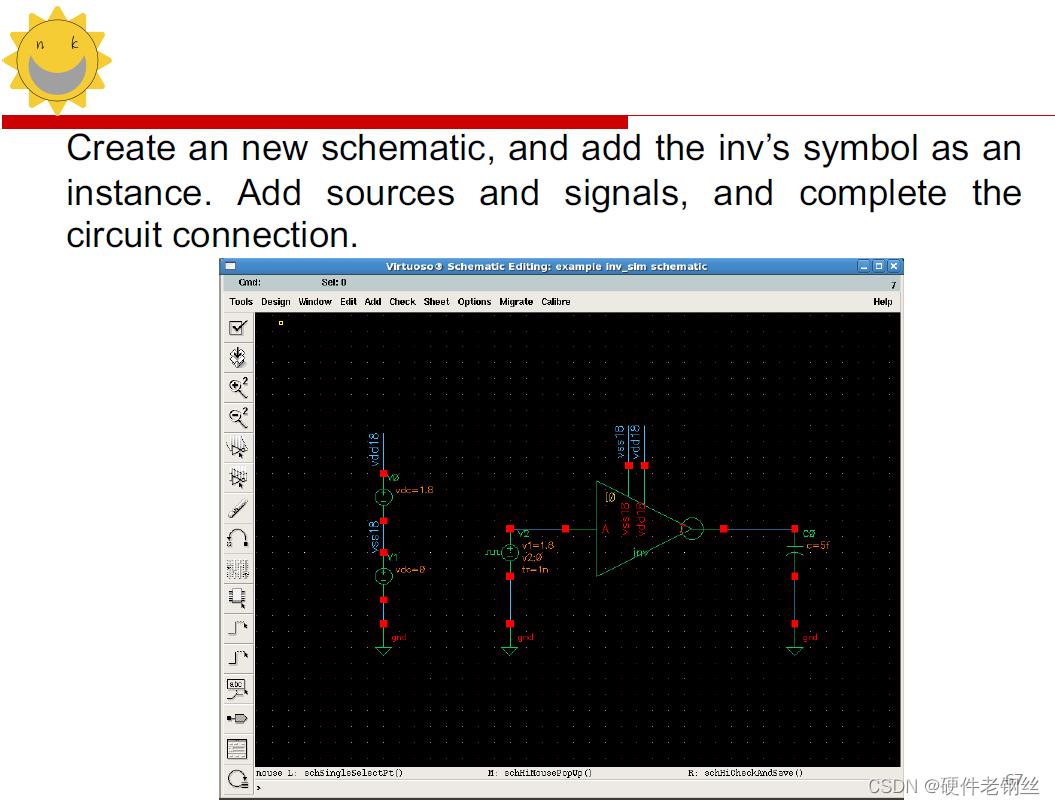

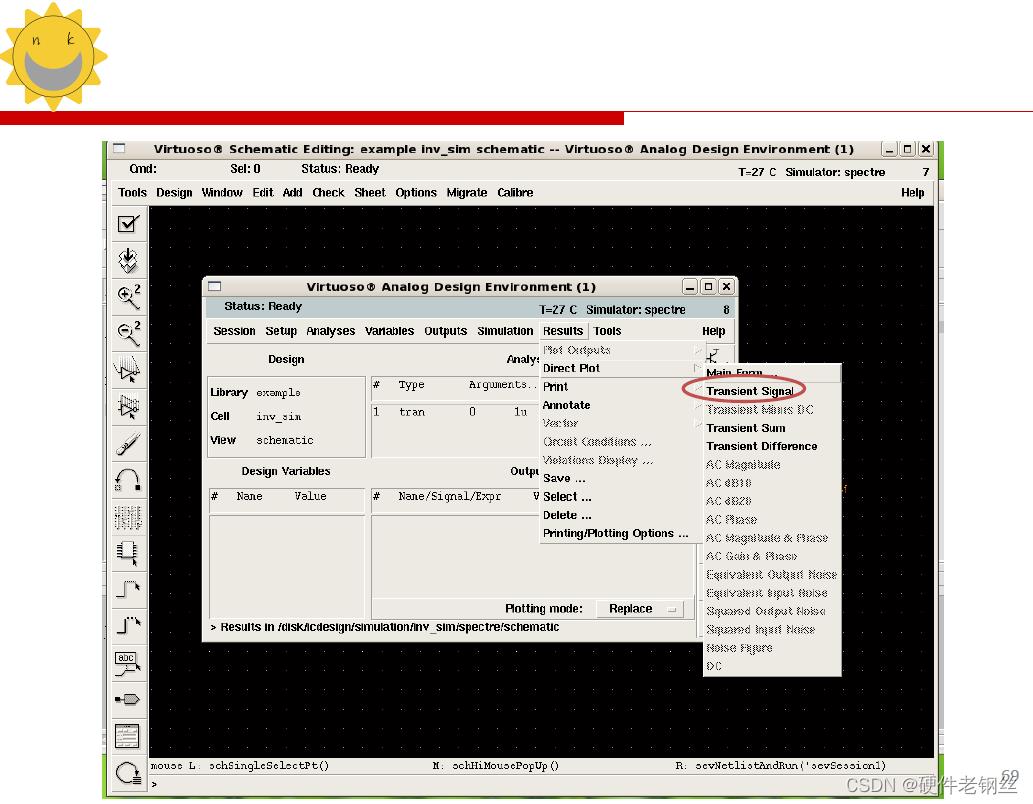

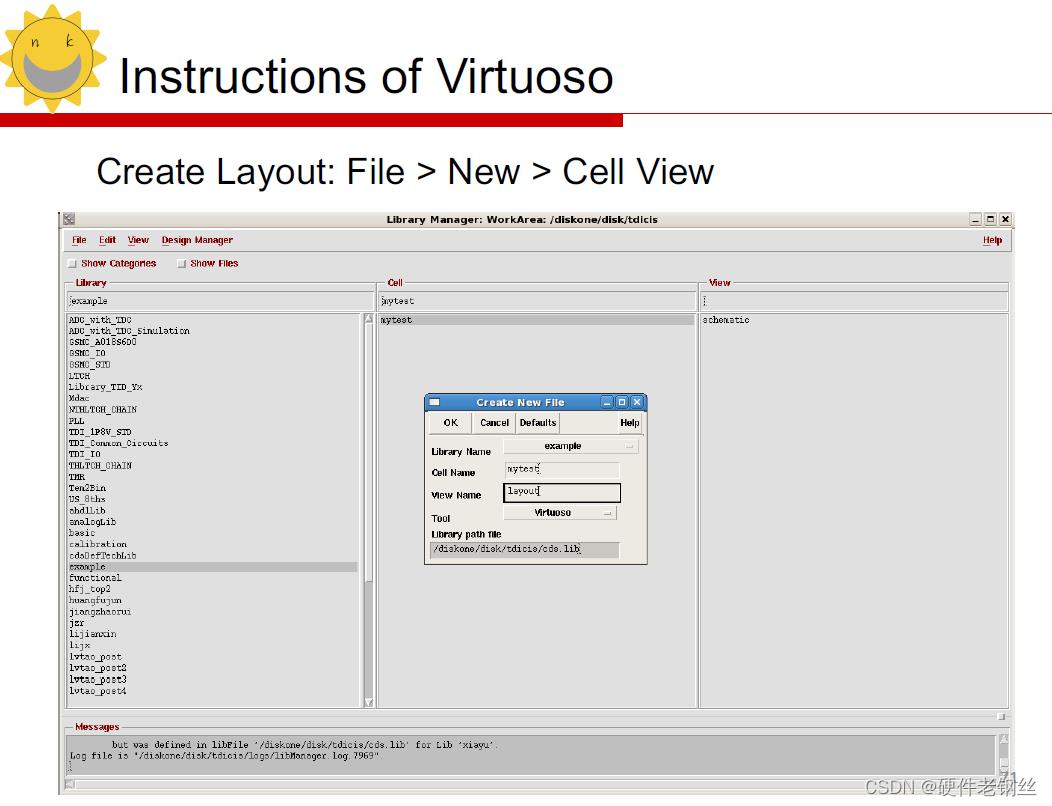

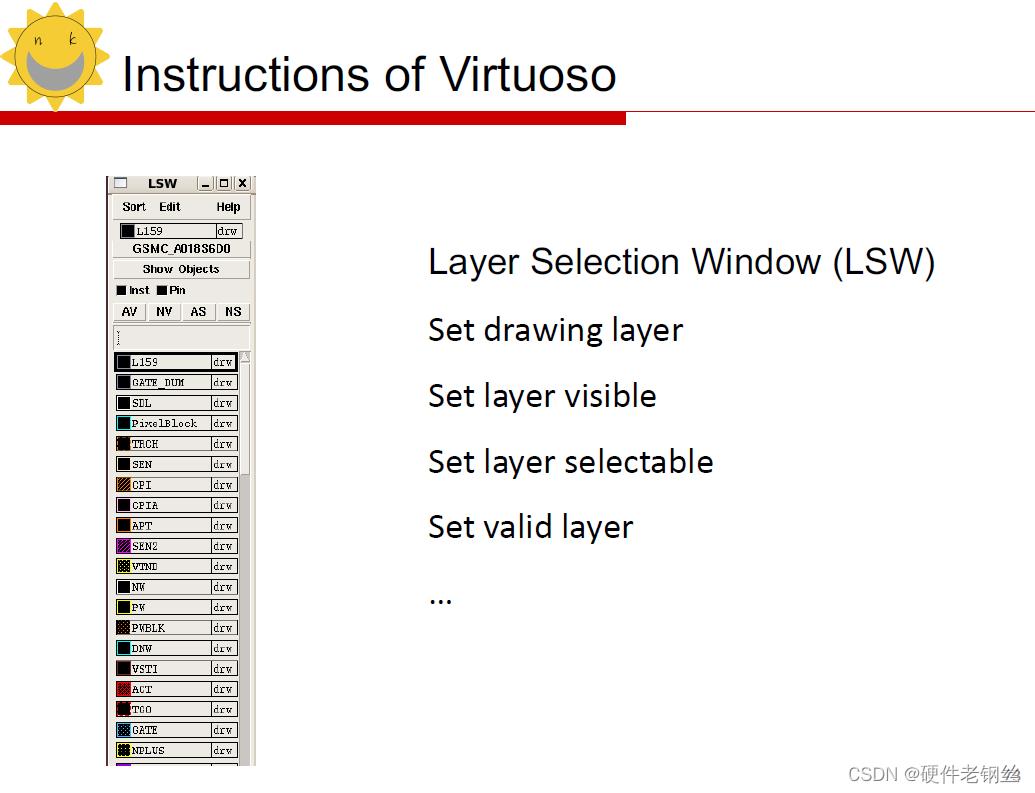

五、软件仿真的一些简单步骤

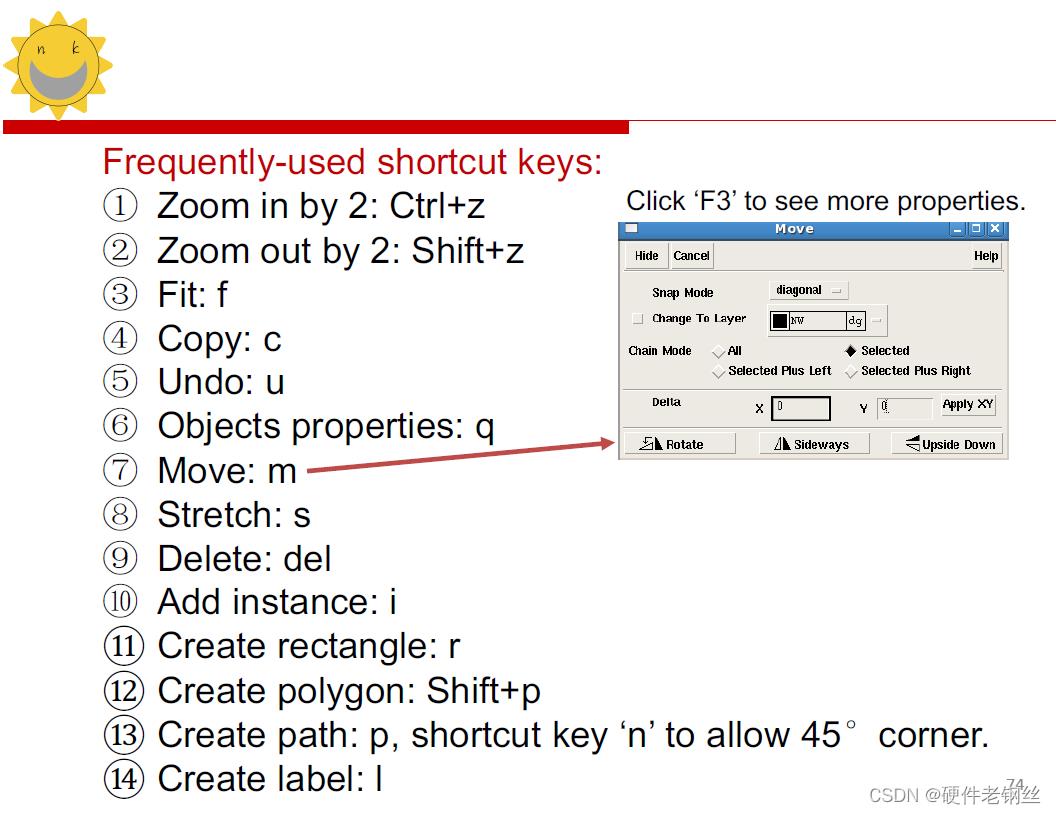

版图操作技巧

以上是关于Cadence画版图时改变全部金属层的主要内容,如果未能解决你的问题,请参考以下文章

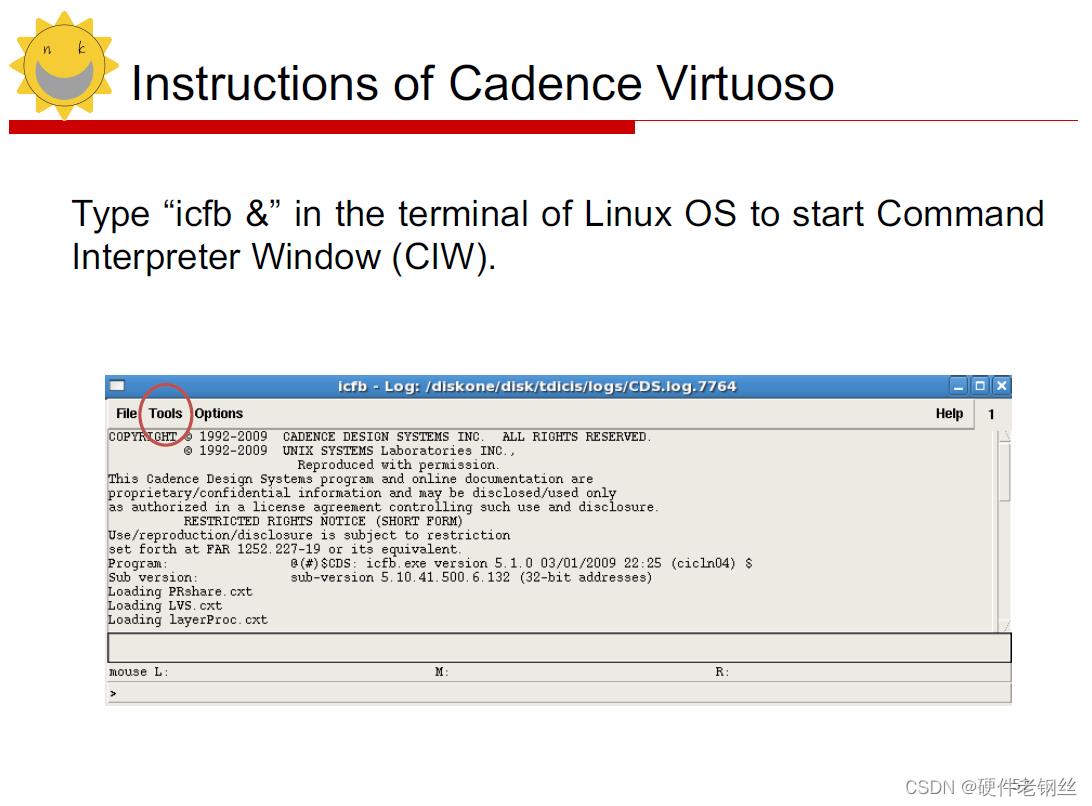

跪求在LINUX下安装 cadence的详细步骤!记住要详细额.