求TTL电平转485电平的电路图,谢谢!!

Posted

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了求TTL电平转485电平的电路图,谢谢!!相关的知识,希望对你有一定的参考价值。

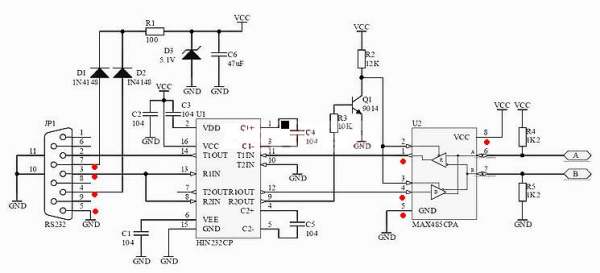

自制RS232-485转换器电路图:

RS232-485转换器主要包括了电源、232电平转换、485电路三部分。本电路的232电平转换电路采用了NIH232或者也可以直接使用MAX232集成电路,485电路采用了MAX485集成电路。为了使用方便,电源部分设计成无源方式,整个电路的供电直接从PC机的RS232接口中的DTR(4脚)和RTS(7脚)窃取。PC串口每根线可以提供大约9mA的电流,因此两根线提供的电流足够供给这个电路使用了。经实验,本电路只使用其中一条线也能够正常工作。使用本电路需注意PC程序必须使串口的DTR和RTS输出高电平,经过D3稳压后得到VCC,经过实际测试,VCC电压大约在4.7V左右。因此,电路中要说D3起的作用是稳压还不如说是限压功能。

MAX485是通过两个引脚RE(2脚)和DE(3脚)来控制数据的输入和输出。当RE为低电平时,MAX485数据输入有效;当DE为高电平时,MAX485数据输出有效。在半双工使用中,通常可以将这两个脚直接相连,然后由PC或者单片机输出的高低电平就可以让MAX485在接收和发送状态之间转换了。由于本电路DTR和RTS都用于了电路供电,因此使用TX线和HIN232的另外一个通道及Q1来控制MAX485的状态切换。平时NIH232的9脚输出高电平,经Q1倒相后,使MAX485的RE和DE为低电平而处于数据接收状态。当PC机发送数据时,NIH232的9脚输出低电平,经Q1倒相后,使MAX485的RE和DE为高电平而处于数据发送状态。

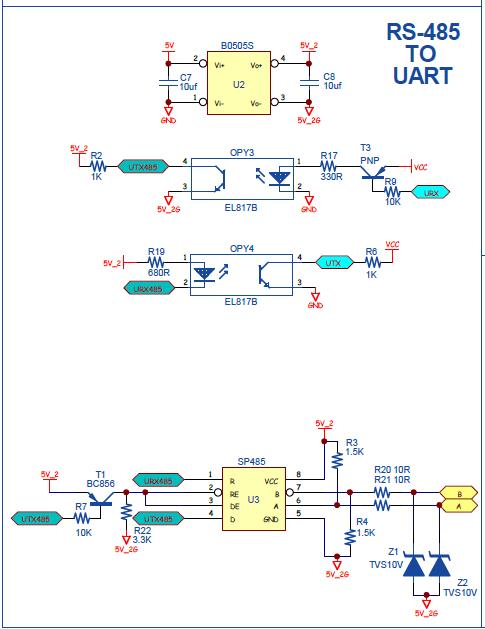

参考技术A也可以用这个电路,这个电路不需要单独接RE端。

powerbus手册

【电路出处:EV721手册】

如果对通讯可靠性有要求和大规模布线的需求,可以看一下二总线技术。无极性,任意拓扑,任意线缆,无需隔离。兼容MODBUS通讯协议。

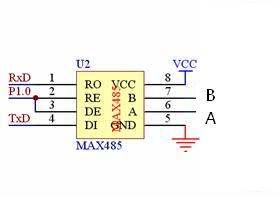

参考技术B如图:

图中,P1.0可与单片机任意IO口连接,P1.0为高电平时,RS485处于发送状态,单片机将串行数据送至Txd引脚。P1.0为低电平时,RS485处于接收状态,单片机从Rxd引脚接收串行数据。

分离比较麻烦不如用485芯片方便稳定,建议用485芯片

RS485转ttl 电路图的原理: RS485转TTL电平这俩是相互转换的,就是这么一个芯片实现功能就是电平转换,TTL是直接连接单片机

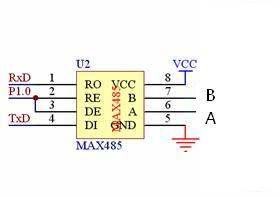

如下图:

图中,P1.0可与单片机任意IO口连接,P1.0为高电平时,RS485处于发送状态,单片机将串行数据送至Txd引脚。P1.0为低电平时,RS485处于接收状态,单片机从Rxd引脚接收串行数据。

追问那这样在传输的过程中还要一直变换P1.0的高低电平,这样太麻烦吧,我看过一个电路图,也是485芯片,还加了3个TLP521-1的光耦,着几个光耦是控制输出高低电平吗?

追答光耦是起隔离作用的。三个光耦分别隔离Rxd、P1.0和Txd。

上图是总线结构的RS485中常用的控制方式。485为半双工传输模式,也就是说,总线上的设备,同时只允许一个设备在发送,因此,发送和接收的控制非常重要,平时,P1.0置0,RS485处于接收状态,接收到本机指令时,若需要应该,P1.0置1,开始发送数据,发送完毕,P1.0置0.

还有一种控制方式,就是将RE一直置0,也就是一直允许接收,另外,将Txd经过反向器接DE。

这样,Txd发送高电平时,实际上发送是禁止的,总线输出为空闲(高电平),Txd发送低电平时,发送允许,低电平出现在总线上。

作为总线设备时,一般建议用第一种,作为转换器时(无处理器模式,如RS232/RS485模块),采用第二种模式。

您是高手,说的太专业了,我是初学者,我不做软件,你说的第一种的方式,是不是我还的在软件里控制,我想做一块TTL砖485的转换板,所有的电路,只要是TTL电平,都可以经过这个转换板进行转换。我是想把ARM(SAMSUNG2440)的TTL电平转换成485电平,现在ARM上已经给我留出一个串口(TXD.RXD,GND,VCC)我只有这4个引脚可以用,求大侠帮助

追答那就只能用第二种方式了。

追问那样还用光耦吗?求大侠给个电路图吧。谢谢啊

追答光耦的目的是隔离,一般情况下,用不用都可以。

电路就是2脚接地,4脚经过一般非门连接3脚。

能给个你的邮箱吗?我画了个图,你看对不对?

追答AnyWay_cn@126.com

本回答被提问者和网友采纳 参考技术D 分离比较麻烦不如用485芯片方便稳定,建议用485芯片100分求助,LVTTL和TTL电平之间如何转换?

100分求助,希望能得到大家的帮助,谢谢!

我在做一个实验,用C51单片机驱动AD芯片做电压采样。AD是TI公司的TLC0820AIN,电源电压是5V,输出信号的电平是TTL电平。这个电平驱动51单片机足够了。

现在我们要往一个FPGA中烧C51核,然后用FPGA来驱动AD,但FPGA的IO电平是LVTTL的,3.3V;AD的控制线和数据线都是TTL电平,5V。所以我想这两个器件不能直接连在一起吧,否则AD的输出会把FPGA烧坏,而FPGA的输出电压太低,AD也不会认可吧?

所以我在想,有什么东西可以实现LVTTL对TTL之间电平的互换,比如某个芯片,这样我可以直接在两个器件的IO之间接上这个芯片,转换电平,而不必再用电阻做上拉或者分压之类的吧?

TTL使用注意:TTL电平一般过冲都会比较严重,可能在始端串22欧或33欧电阻; TTL电平输入脚悬空时是内部认为是高电平。要下拉的话应用1k以下电阻下拉。TTL输出不能驱动CMOS输入。

ECL、PECL、LVPECL使用注意:不同电平不能直接驱动。中间可用交流耦合、电阻网络或专用芯片进行转换。

以上三种均为射随输出结构,必须有电阻拉到一个直流偏置电压。(如多用于时钟的LVPECL:直流匹配时用

130欧上拉,同时用82欧下拉;交流匹配时

用82欧上拉,同时用130欧下拉。但两种方式工作后直流电平都在1.95V左右。) 参考技术A TTL输出高电平>2.4V,输出低电平<0.4V。在室温下,一般输出高电平是3.5V,输出低电平是0.2V。最小输入高电平和低电平:输入高电平>=2.0V,输入低电平<=0.8V,噪声容限是0.4V。

TTL使用注意:TTL电平一般过冲都会比较严重,可能在始端串22欧或33欧电阻;

TTL电平输入脚悬空时是内部认为是高电平。要下拉的话应用1k以下电阻下拉。TTL输出不能驱动CMOS输入。

ECL、PECL、LVPECL使用注意:不同电平不能直接驱动。中间可用交流耦合、电阻网络或专用芯片进行转换。

以上三种均为射随输出结构,必须有电阻拉到一个直流偏置电压。(如多用于时钟的LVPECL:直流匹配时用

130欧上拉,同时用82欧下拉;交流匹配时

用82欧上拉,同时用130欧下拉。但两种方式工作后直流电平都在1.95V左右。) 参考技术B TTL输出高电平>2.4V,输出低电平<0.4V。在室温下,一般输出高电平是3.5V,输出低电平是0.2V。最小输入高电平和低电平:输入高电平>=2.0V,输入低电平<=0.8V,噪声容限是0.4V。

TTL使用注意:TTL电平一般过冲都会比较严重,可能在始端串22欧或33欧电阻;

TTL电平输入脚悬空时是内部认为是高电平。要下拉的话应用1k以下电阻下拉。TTL输出不能驱动CMOS输入。

ECL、PECL、LVPECL使用注意:不同电平不能直接驱动。中间可用交流耦合、电阻网络或专用芯片进行转换。

以上三种均为射随输出结构,必须有电阻拉到一个直流偏置电压。(如多用于时钟的LVPECL:直流匹配时用

130欧上拉,同时用82欧下拉;交流匹配时

用82欧上拉,同时用130欧下拉。但两种方式工作后直流电平都在1.95V左右。) 参考技术C FPGA的输出电压AD是可以认可的,应为3.3V已经可以识别为高。我用cyclone2来驱动AD7821,完全没问题,为了可靠,你也可以用非门整下形。

FPGA的输入管脚只要不是负的,一般就不会烧坏,你在烧程序前设置一下内部上拉电阻,注意输入信号都是正的,就可以直接用。 参考技术D 用74LVC16245来进行电平转换就行了吧?你看看这芯片的资料。

以上是关于求TTL电平转485电平的电路图,谢谢!!的主要内容,如果未能解决你的问题,请参考以下文章

下面是我画的MAX485转TTL电平电路原理图,求大神帮忙看看能实现正常通信吗? 另外:这个PA0我应该怎么写程序

232转rs485芯片,电路求分析,R2OUT在PC机发送数据时不是时高时低么,那485发送使能不是就一会开一会关么