VIVADO HLS数组的优化

Posted 朽月

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了VIVADO HLS数组的优化相关的知识,希望对你有一定的参考价值。

VIVADO HLS数组的优化

参考文献

[1]、lauren的FPGA(微信公众号)

[2]、Xilinx暑期学校

项目简述

前面一篇文章,我们已经进行了讲解软件程序中最重要的两个指标是时间复杂度、空间复杂度。上面循环语句的优化主要体现在时间复杂度的优化,那么这篇文章我们将着重于空间复杂度的优化。时间复杂度体现在循环语句上面,而空间复杂度则体现在数组上面,所以这篇文章我们将讲解VIVADO HLS数组的优化。但是需要注意的是,我们并不是为了少使用FPGA的资源,而是为了设计更高的性能,因为HLS最主要的贡献也在加速上面,如果速度上不来,就失去了原来的意义。

数组的分割

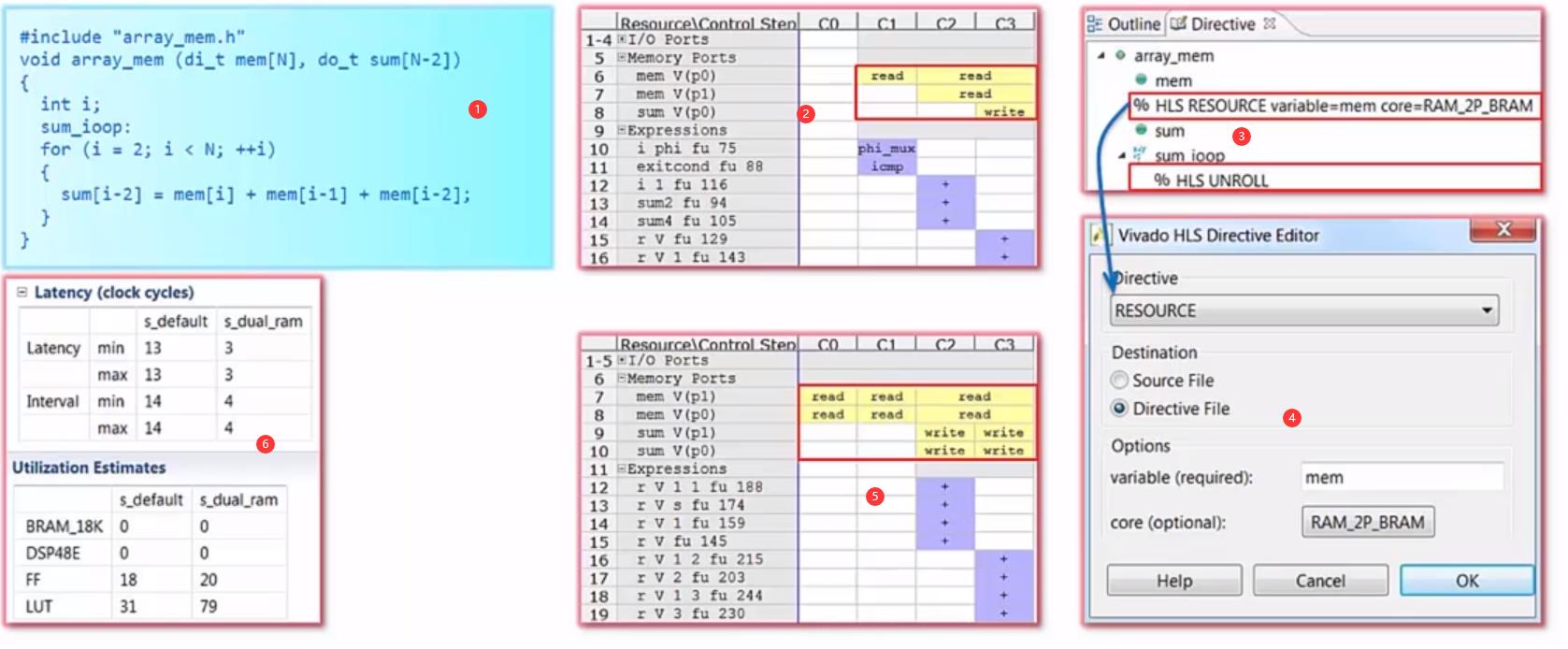

这里首先从一个例子说明数组优化的重要性,

首先从1中的代码可以看出是对数组的累加赋值操作,从2中分析的结果可以看出HLS软件将数组mem自动优化成双端口ram,但是输出sum依然是单端口ram,这就严重限制了编译之后的latency,但是将输出sum的单端口ram改成了双端口ram,同时将loop循环展开,可以看出HLS的性能得到了很大程度的改善。由此可见,HLS中数组时大多数编译中性能的瓶颈,决定了HLS跑的快慢。

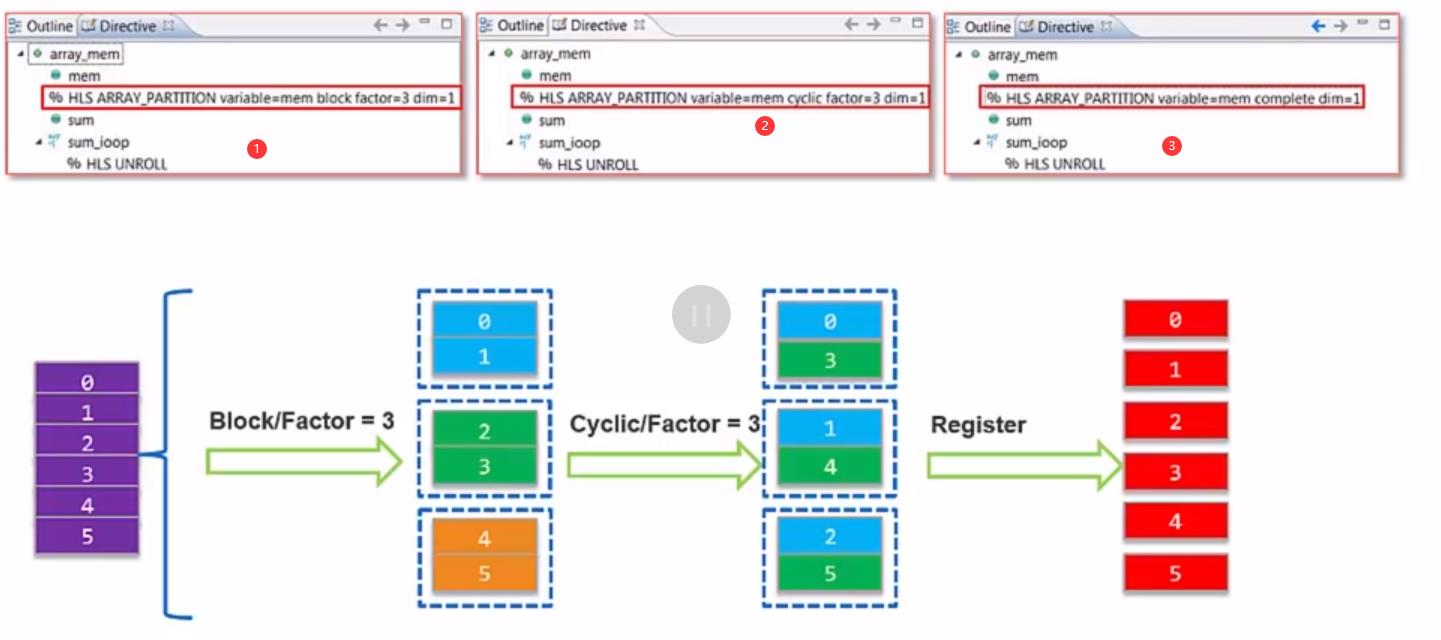

对数组采用Partition展开操作

对一维数组采用Partition展开操作

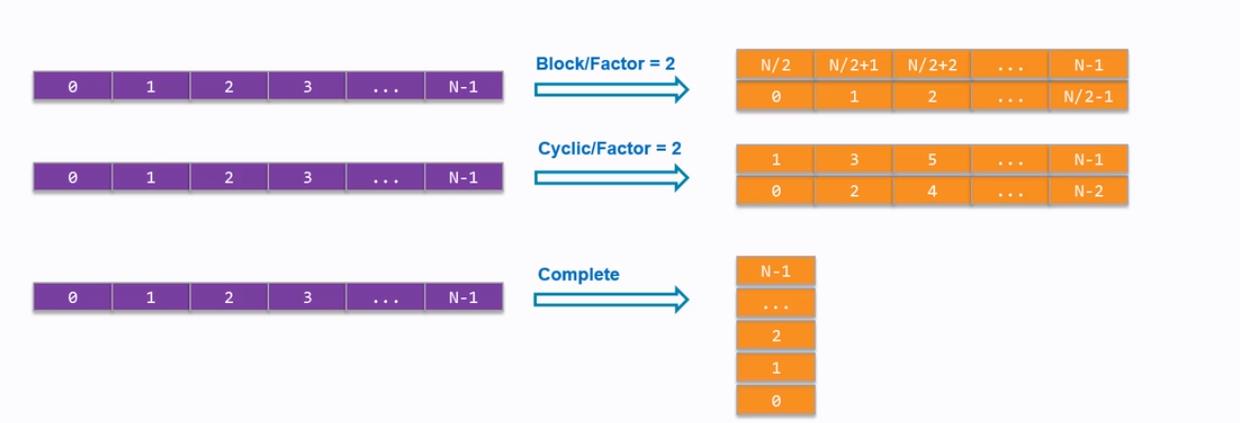

如下图:

1,2,3都采用了Partition对数组进行了展开,这里主语对于多维数组,dim的设置哦很重要,由于这里是一维数组只能选择为1.也要注意Block与Cyclic的作用,这里Cyclic是比较常用的。进行编译之后的比较如下:

上面Partition的个数取决于数据流的个数。

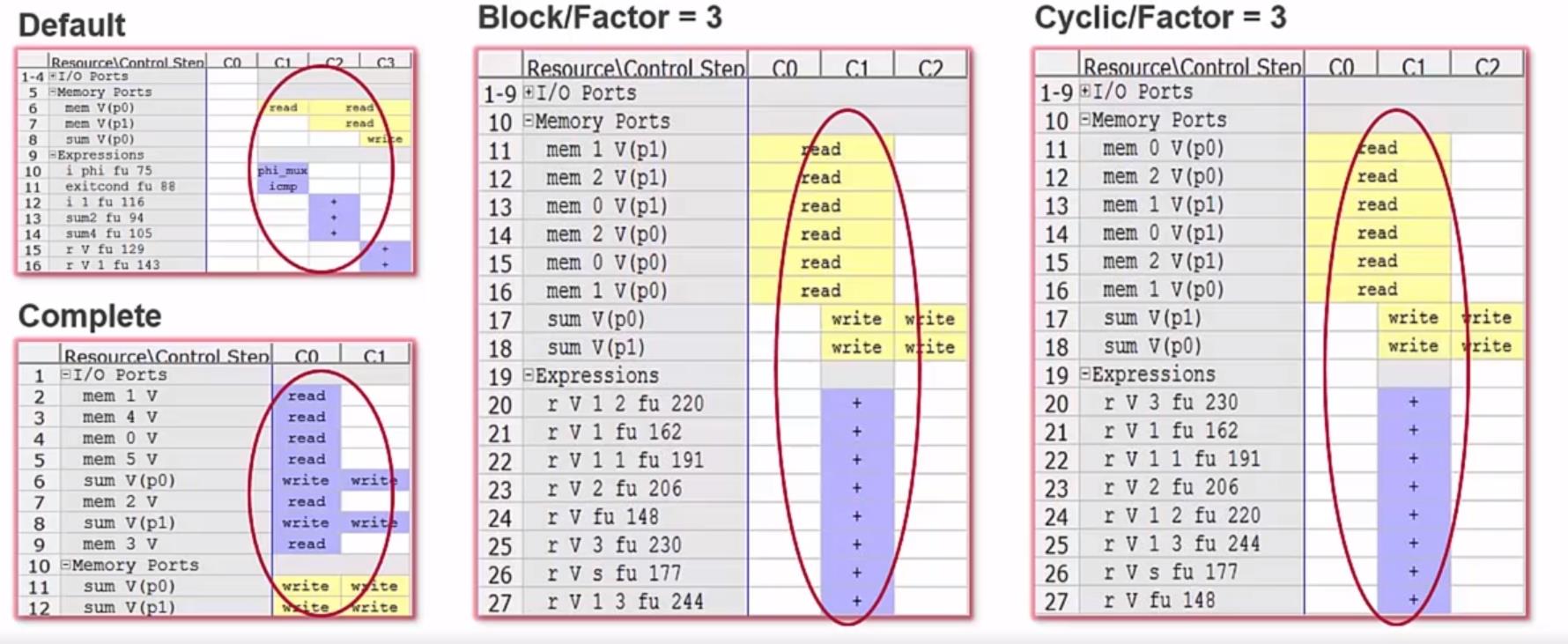

对多维数组采用Partition展开操作

对于多维数组dim的指定如下:

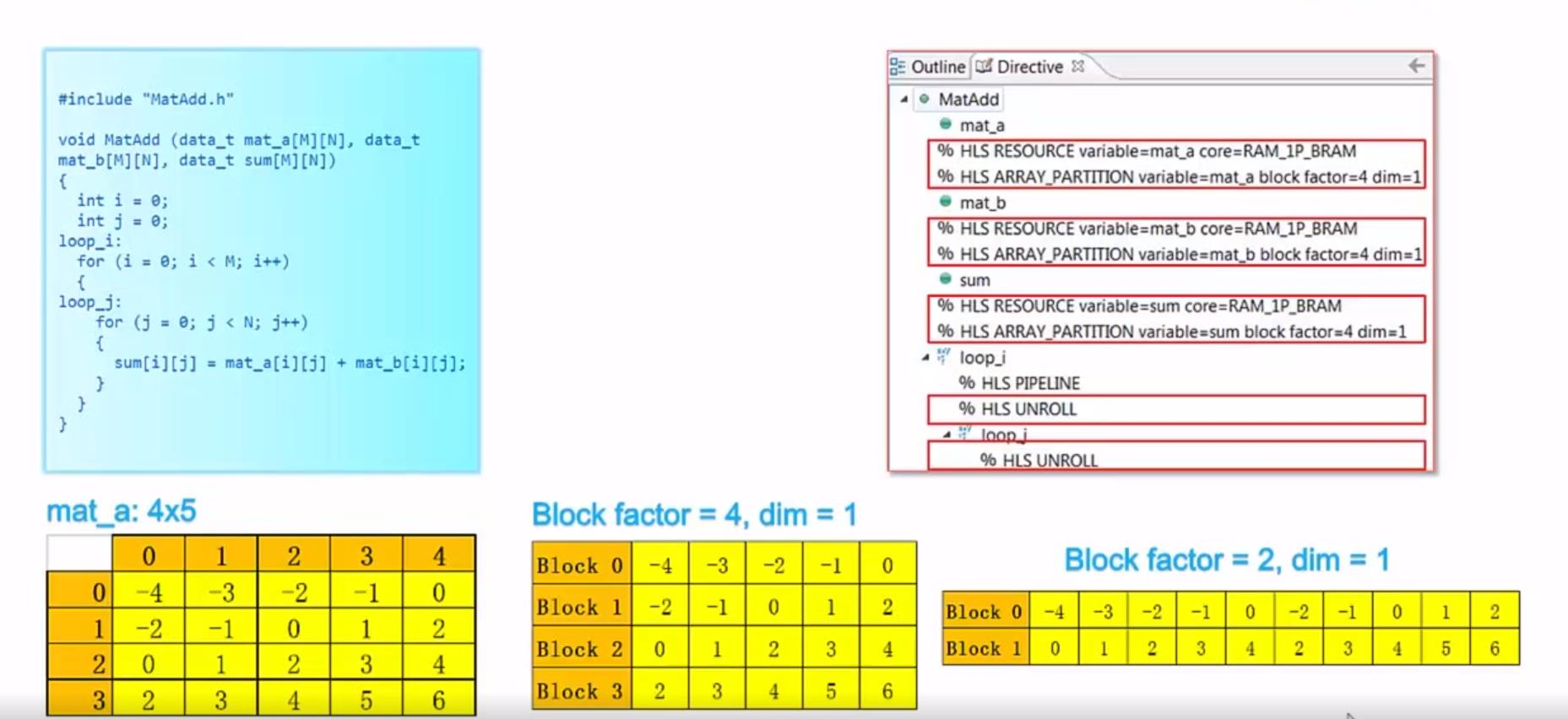

举一个使用Partition优化多维数组的例子如下:

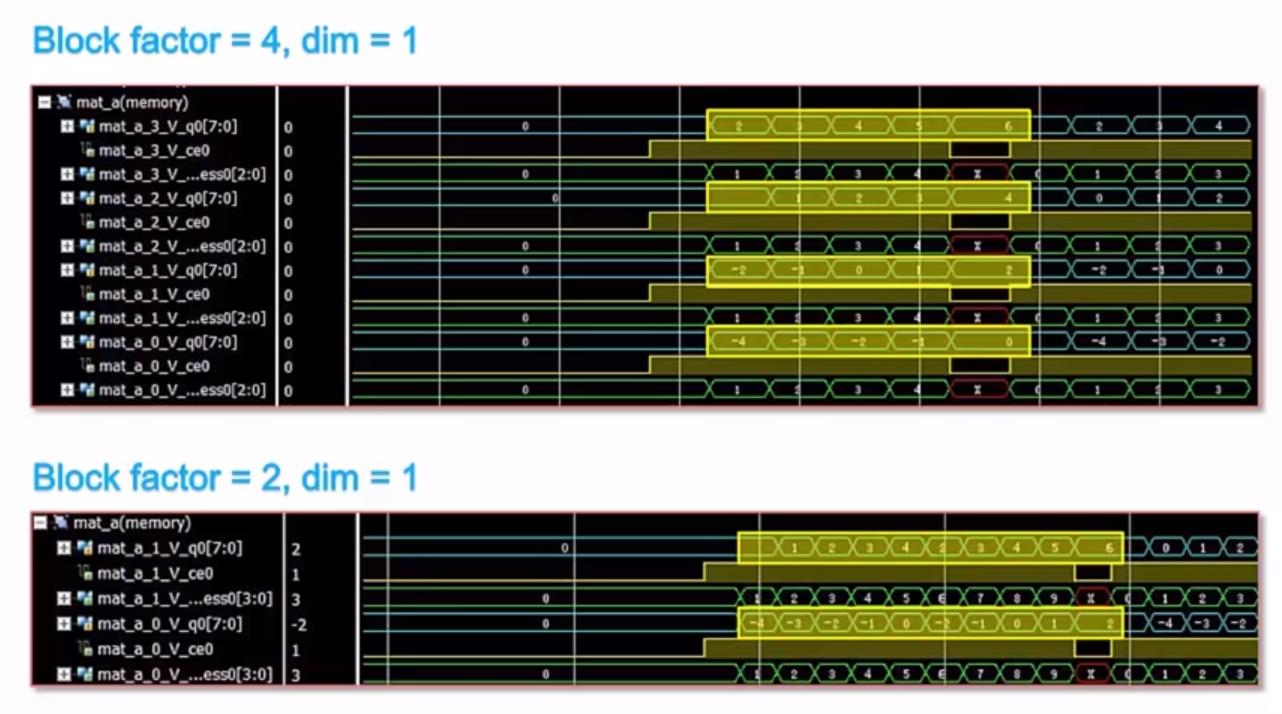

结果如下:

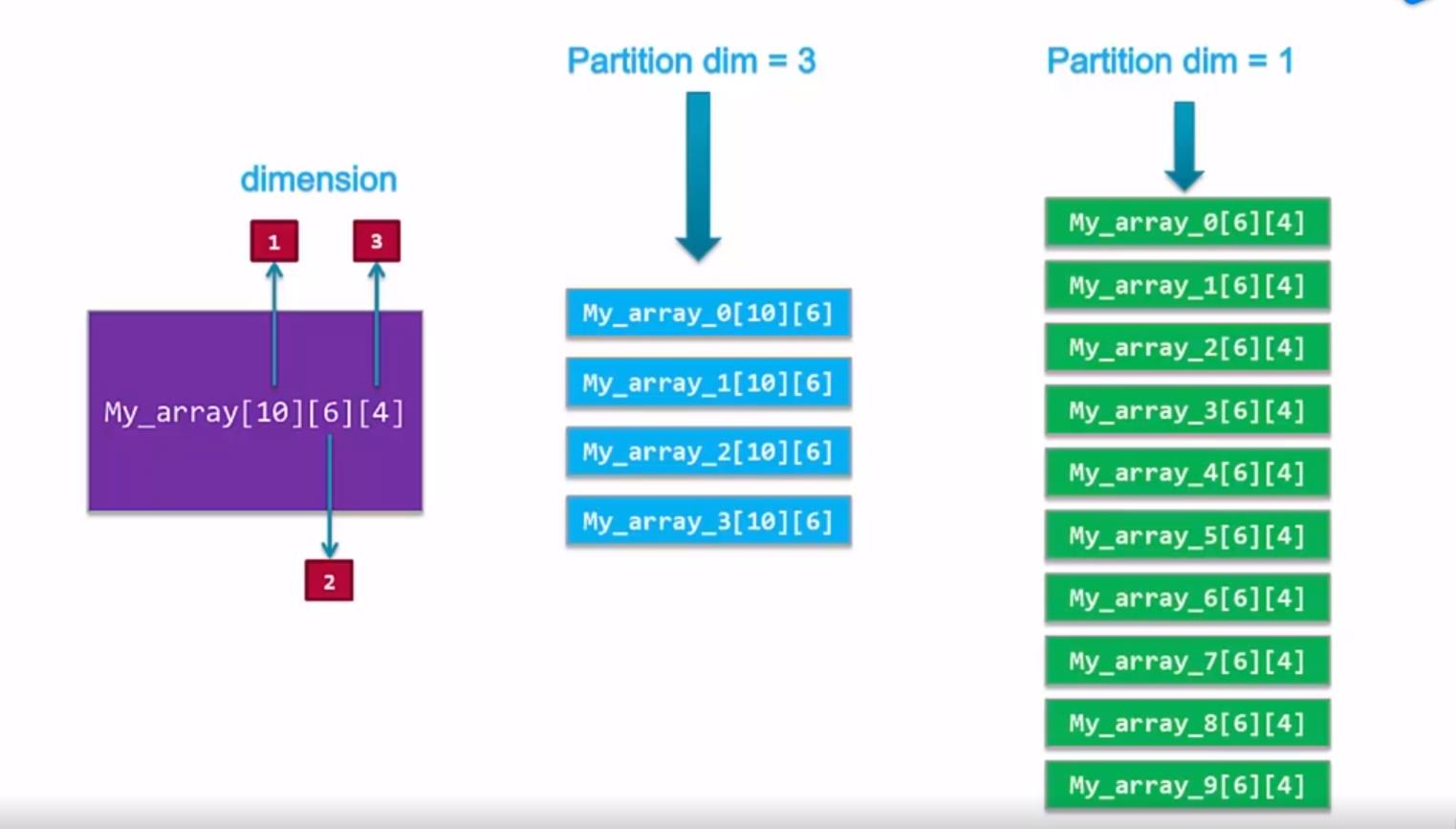

数组的映射和重组

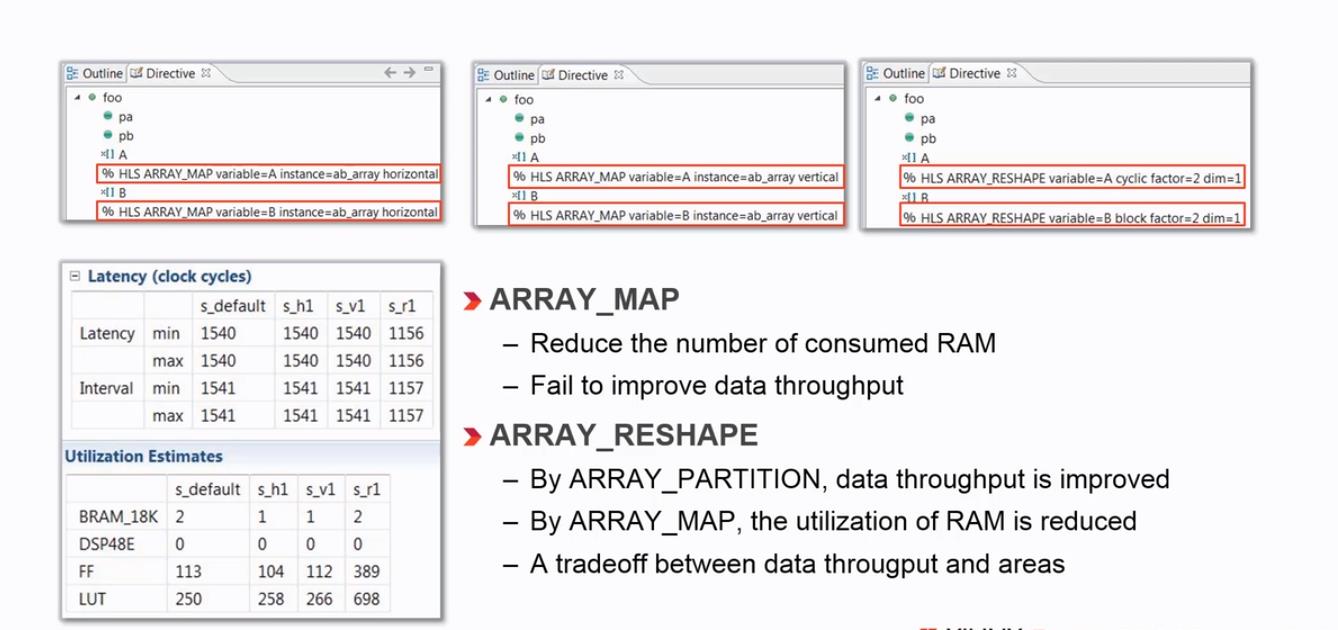

数组的MAP

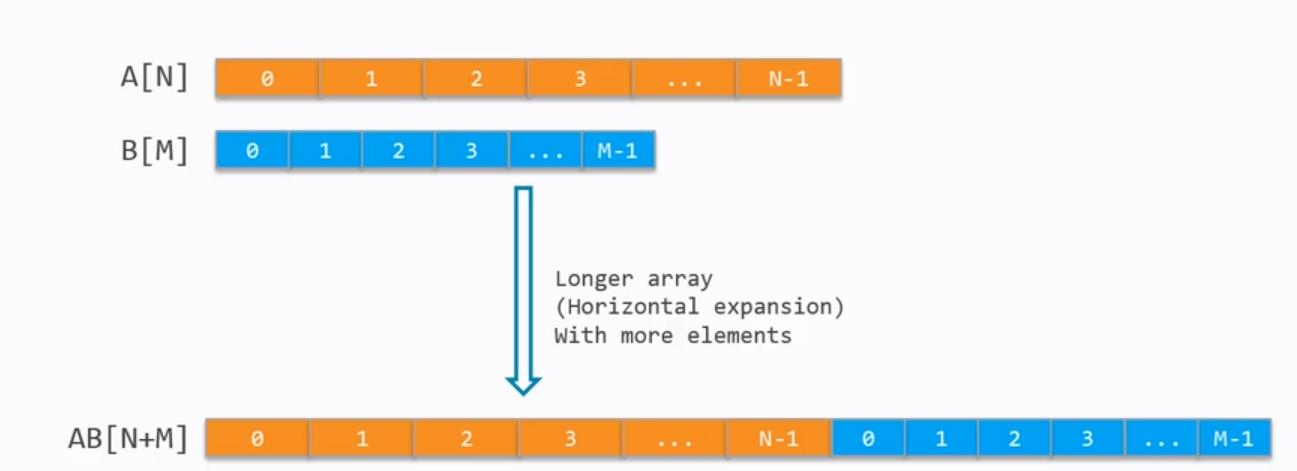

MAP:意思是将C语言中比较小的数组映射成一个数组,从而减少FPGA内部资源的用量。

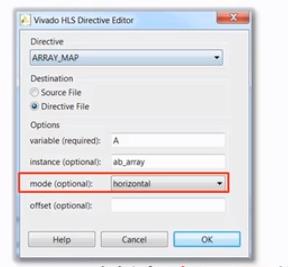

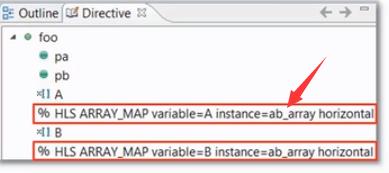

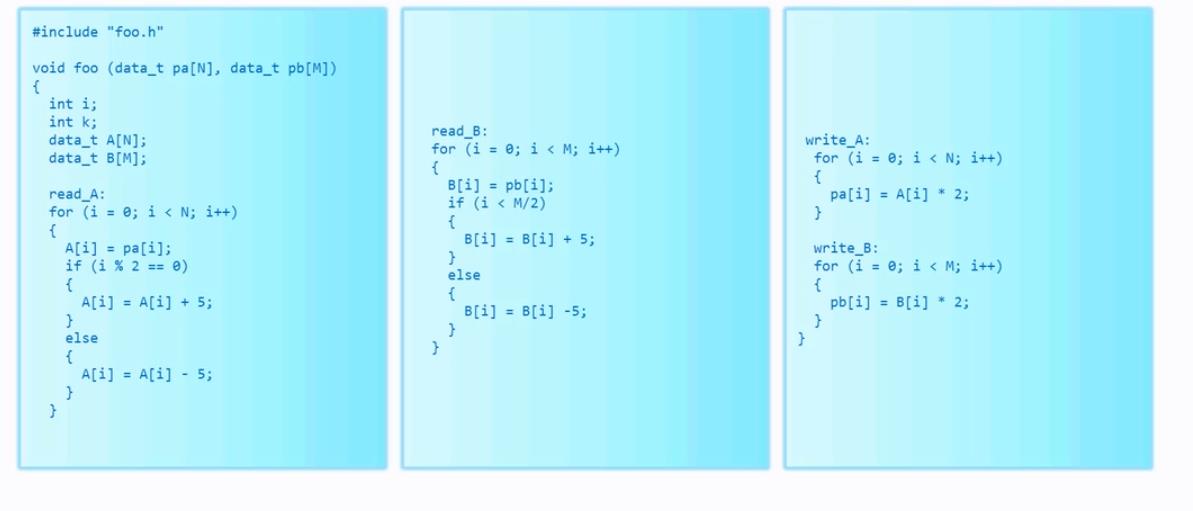

Horizontal Mapping示意图如下:

这里的名字很重要。

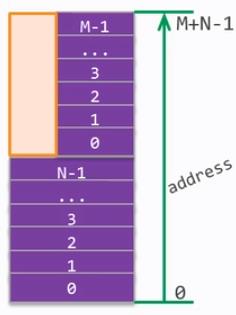

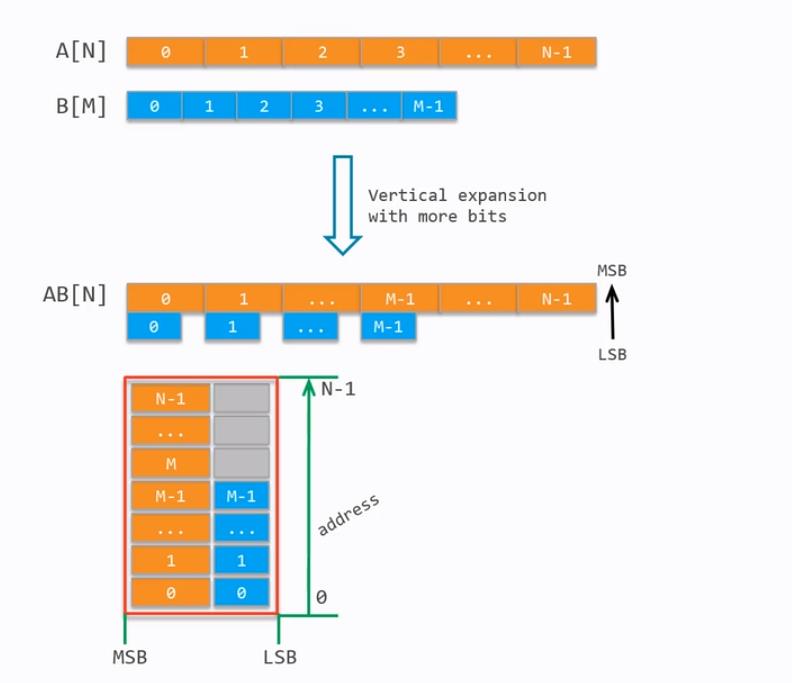

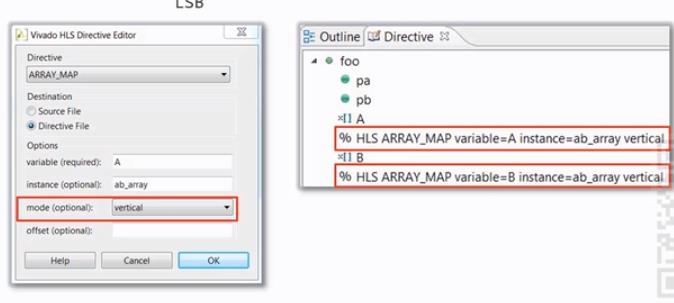

Vertical Mapping示意图如下:

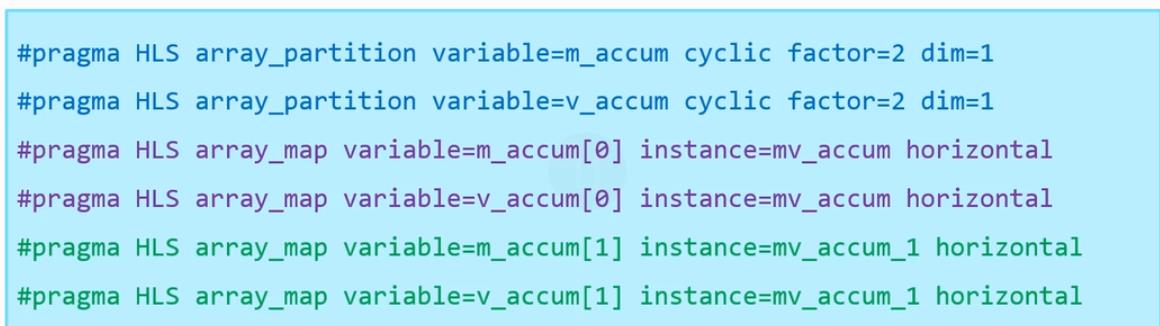

数组的MAP与Partition一起使用的例子如下:

这样一拆一和可以让数组节省资源的条件下获得一定的数据吞吐率。

数组的ARRAY_RESHAPE

ARRAY_RESHAPE:将数组的Partition与纵向的MAP结合在一起。

原理如下:

举一个实际的例子如下:

从上面可以看出MAP可以获得资源的节省,ARRAY_RESHAPE可以获得吞吐率的提高。

总结

创作不易,认为文章有帮助的同学们可以关注、点赞、转发支持。为行业贡献及其微小的一部分。对文章有什么看法或者需要更近一步交流的同学,可以加入下面的群:

以上是关于VIVADO HLS数组的优化的主要内容,如果未能解决你的问题,请参考以下文章