如何新建Quartus工程

Posted

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了如何新建Quartus工程相关的知识,希望对你有一定的参考价值。

第一步:从开始菜单启动Quartus II 13.1(64 bit)第二步:菜单栏选择File—>New Project Wizard,新建工程。

第三步:弹出新建工程对话框,点击Next,下一步。

依次设置工程的存放路径,工程名称,顶层文件名称,如图依次设置好,这里我们将所有工程相关的文件放在prj文件夹内,便于工程文件与源码文件的管理,同时要保持工程名称与顶层实体名称一致,继续Next。

第四步:添加设计文件,这一步我们不需要添加,后续我们会新建相应的代码文件。这里继续Next。

第五步:选择FPGA器件,如图所示,这里我们选择器件家族是CycloneIV系列的,封装是FBGA,管脚数为256,速度等级为8。这里速度等级越小,速度越快。这里我们FPGA的具体型号为EP4CE6F17C8。大家通过这个对话框了解这个器件的基本资源。这里我简单介绍一下这些资源的名称,在后面的章节里我们还会详细讲解FPGA内部资源与结构。

1、CoreVoltage是内核电压,Cyclone IV的内核电压是1.2V。

2、LE是Altera最基本的逻辑单元,LEs表示FPGA的所有的逻辑资源, 我们这款芯片的逻辑资源数为6272。

3、User I/Os表示用户IO数,这里共有180个IO可以供用户使用。

4、Memory Bits与embedded multiplier 9-bit elements实际是一回事,后者简称M9K,M9K就是指位宽为9bit,深度为1K的RAM。这里一共有30个M9K,大家计算一下9*1024*30=276480就是Memory Bits。

5、PLL锁相环,内部一共有两个锁相环。

6、Global clocks全局时钟网络数,这里一共有10个。

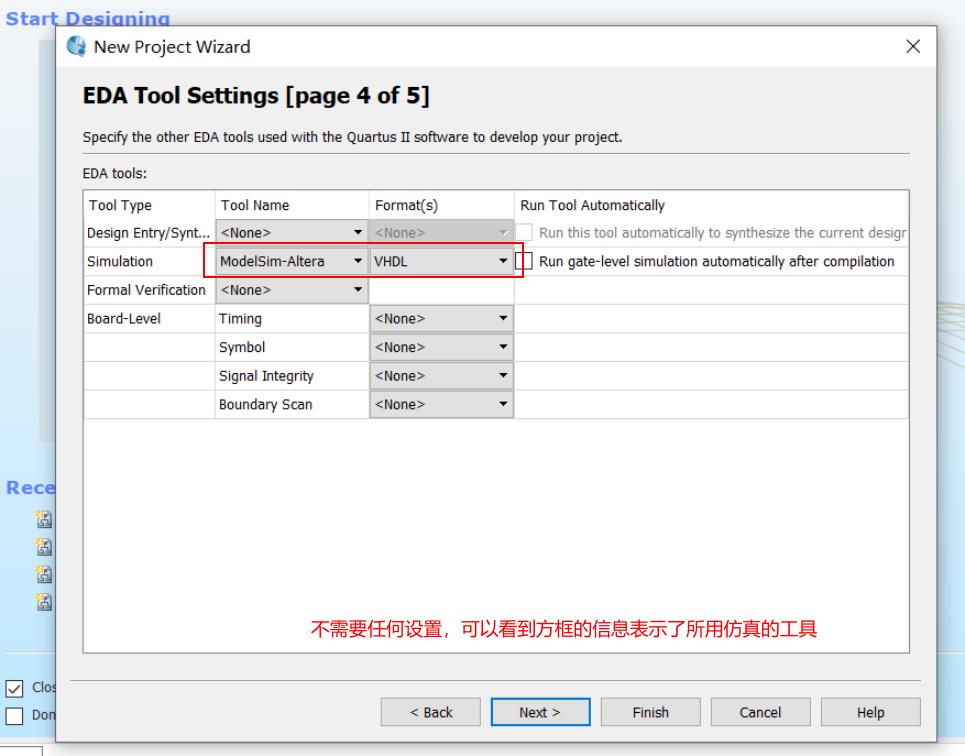

第六步:设置EDA工具,这里我们就设置一下仿真工具,使用默认Modelsim

-Altera,语言选择Verilog。实际后面我们不建议大家使用Modelsim-Altera。我们会推荐大家在直接使用Modelsim-SE,后者的通用性更强。继续Next。

第七步:总结新建工程的基本信息。到这里就完成工程的建立。 参考技术A 1

相对于VC,VB,Protel等软件的新建工程来说,新建quartus II工程不是一件简单的事,quartus的工程建立起来要复杂的多,因为它不仅仅是填写文件名和存储地址这么简单,还包括选择器件和设置仿真,时钟等一些列的问题。

2

3

启动QuartusⅡ软件后默认的界面主要由标题栏、菜单栏、工具栏、资源管理窗口、编译状态显示窗口、信息显示窗口和工程工作区等部分组成。

4

标题栏:标题栏中显示当前工程的路径和工程名。

5

菜单栏:菜单栏主要由文件(File)、编辑(Edit)、视图(View)、工程(Project)、资源(Assignments)、 操作(Processing)、工具(Tools)、窗口(Window)和帮助(Help)等菜单组成。

6

工具栏:工具栏中包含了常用命令的快捷图标。

7

资源管理窗:资源管理窗口用于显示当前工程中所有相关的资源文件。

8

工程工作区:当QuartusⅡ实现不同的功能时,此区域将打开对应的操作窗口,显示不同的内容,进行不同的操作,如器件设置、定时约束设置、编译报告等均显示在此窗口中。

9

编译状态显示窗口:此窗口主要显示模块综合、布局布线过程及时间。

10

信息显示窗口:该窗口主要显示模块综合、布局布线过程中的信息,如编译中出现的警告、错误等,同时给出警告和错误的具体原因。追答

步骤/方法

1

执行菜单命令【File】-【New Project Wizard…】,创建工程向导。

2

3

设置工程文件夹及工程名,在What is the working directory for this project?下选择项目存储地址工作目录,What is the name of this project?下填写工程名,最后一栏填写顶层文件名。

4

5

添加已存在文件(可选),在【File name】下选择已经存在的工程项目,利用【Add】或【Add all】命令添加文件到新工程,点击【Next】

6

7

选择器件,【Device family】-【Family】下选择你要使用的FPGA芯片系列,这里我选择ALtera公司的Cyclone系列,并在【devices】下选择具体芯片型号,点击【Next】

8

9

设定第三方工具,【Design Entry/Synthesis】选择逻辑综合工具,这里可以不填,直接使用Quartus默认工具,【Simulation】下选择仿真工具,这里一般需要配套安装Modelsim,点击【Next】

10

11

显示设置信息,显示了项目路径,项目名,顶层文件,芯片系列型号等设置信息,在检察符合需要后点击【Finish】,完成向导新建工作。

12

13

工程建立完成,可以再【资源管理窗口】查看刚刚新建的工程项目。

14

注意事项

一般的FPGA开发 需要将你要实现的模块,按照功能划分成一个一个子模块,顶层文件就是将这些小的功能模块连接起来的,以实现最终的功能。底层文件就是各个子模块的实现。

EDA初学,新建工程,Quartus软件应用

一、本文内容

内容:掌握Quarters工程的建立方法

版本:Quartus II 13.1(64-bit)

二、建立步骤

1、 打开软件

2、 工程设置

工程名字和后边文件的顶层模块名字以及顶层模块所在文件的名字要保持一致,需要注意,后边会有具体说明

3、新建工程文件

4、结果

三、代码编译、仿真

1、示例代码

module FenPin(

input clk,

input rst,

output wire clk_10k

);

parameter f=8; //偶分频的分频数

reg [11:0] count=0; //存储分频计数

reg clk_10k_tmp=0;

assign clk_10k = clk_10k_tmp;

// ret未被按下,为高电平;按下为低电平,后回复为高电平

always @(posedge clk, negedge rst)

begin

if (!rst)

begin

clk_10k_tmp = 0;

count = 0;

end

else

begin

if (count == f/2-1) //分频系数确定:偶分频数/2 - 1

begin

clk_10k_tmp = ~clk_10k_tmp;

count = 0;

end

else

begin

count = count + 1;

end

end

end

endmodule

2、文件保存

所以在新建工程的时候要注意工程的名字!!!

3、代码编译

4、简单的仿真

新建文件

早期版本的Quartus软件没有提供这种文件,也就无法用此方法进行简单仿真

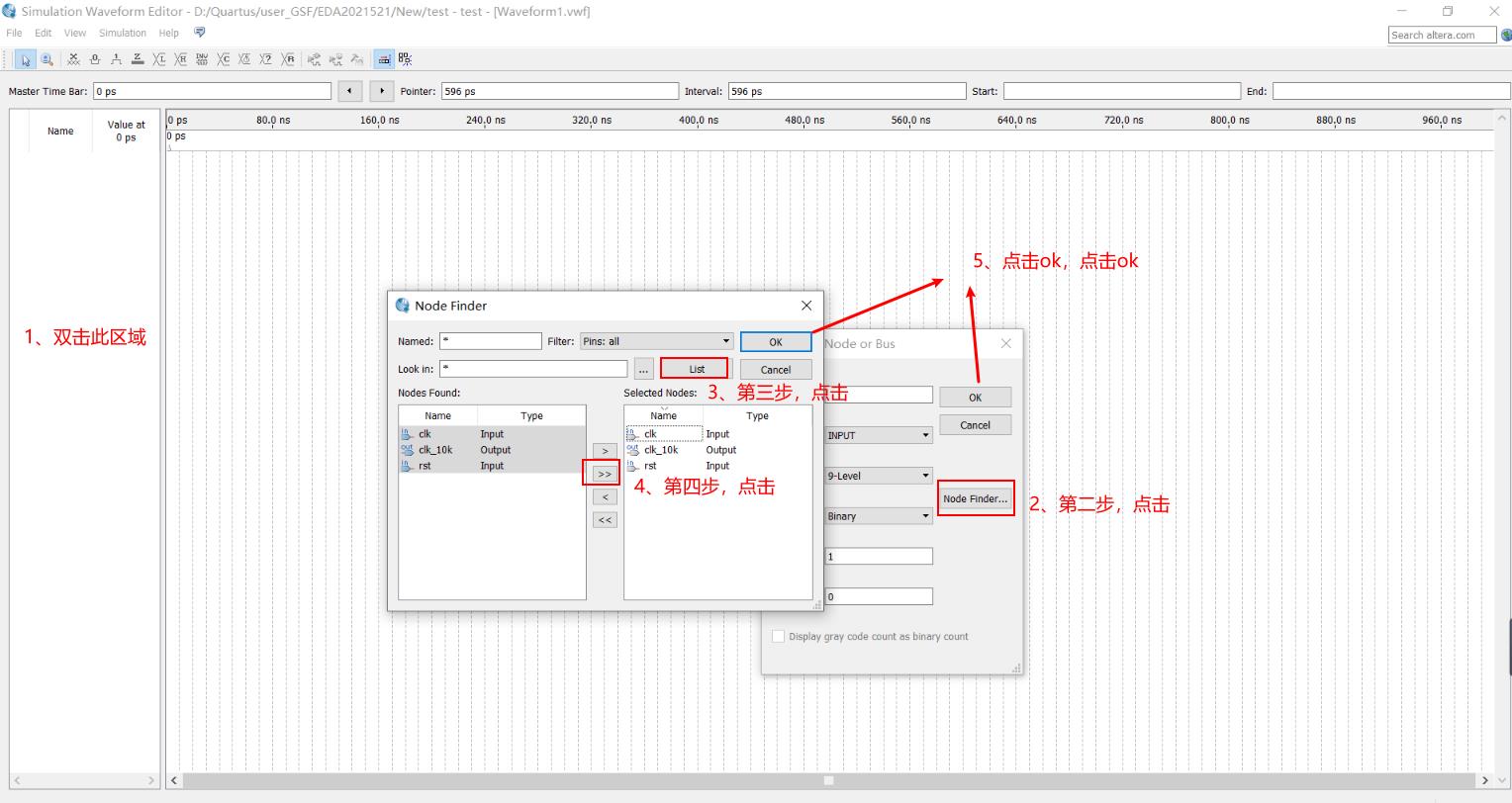

添加输入输出信号

设置输入信号的格式

1、功能介绍

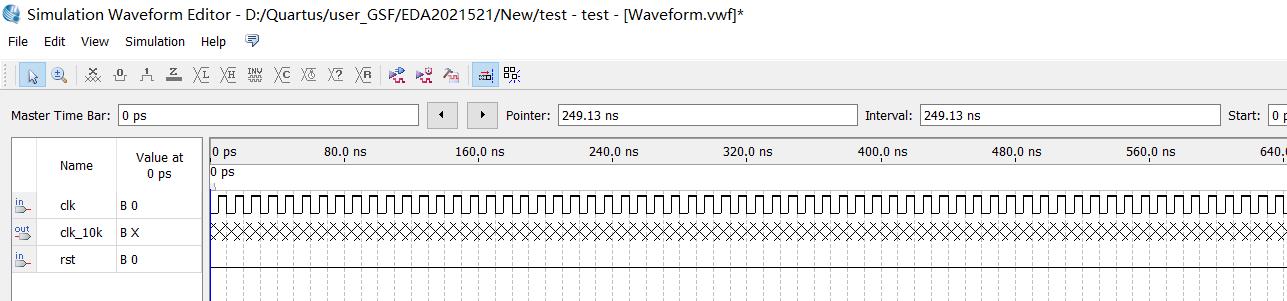

2、设置时钟频率

3、时钟信号设置结果

4、设置rst复位信号

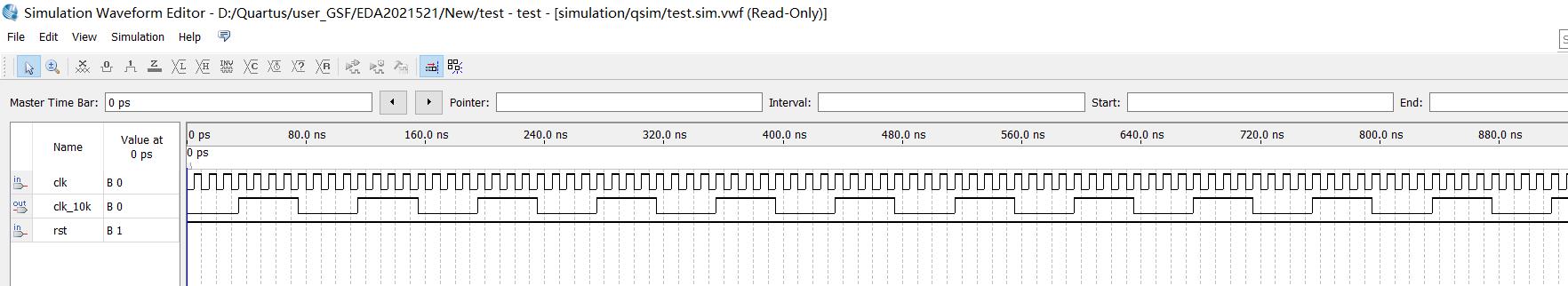

仿真结果

可以看到输出信号clk_10k的时钟频率是clk时钟信号的1/8,正确实现分频功能

总结

这种形式的仿真过于简单,只能在初始时候,设置输入信号的格式,后续就不能更改

再更改信号的格式就需要重新设置,重新仿真

更为广泛的仿真方式:Modelsim仿真

以上是关于如何新建Quartus工程的主要内容,如果未能解决你的问题,请参考以下文章

Quartus系列:Quartus II 调用ModelSim仿真调试