FPGA实验0Quartus建立工程文件以及仿真

Posted 刘一五

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了FPGA实验0Quartus建立工程文件以及仿真相关的知识,希望对你有一定的参考价值。

FPGA的第一课,学习Quartus编程运行仿真烧录的这一个流程,以一个十位的计数器为例。

芯片商家:ALTERA

编程软件:Quartus II

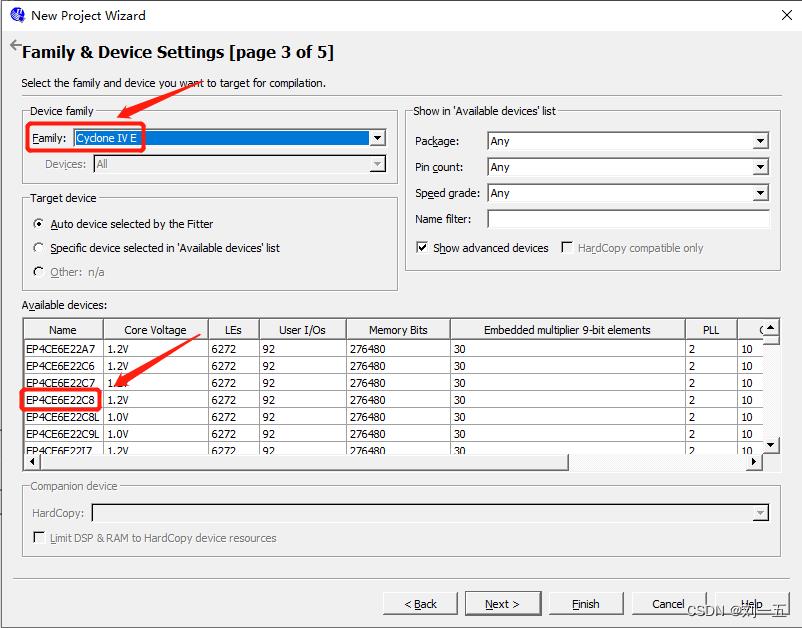

试验箱上的芯片型号:EP4CE6E22C8N

目录

一、新建一个工程

打开软件后会会弹出一个窗口,点击【创建向导】

第一步:设置工程名和顶层硬件模块名

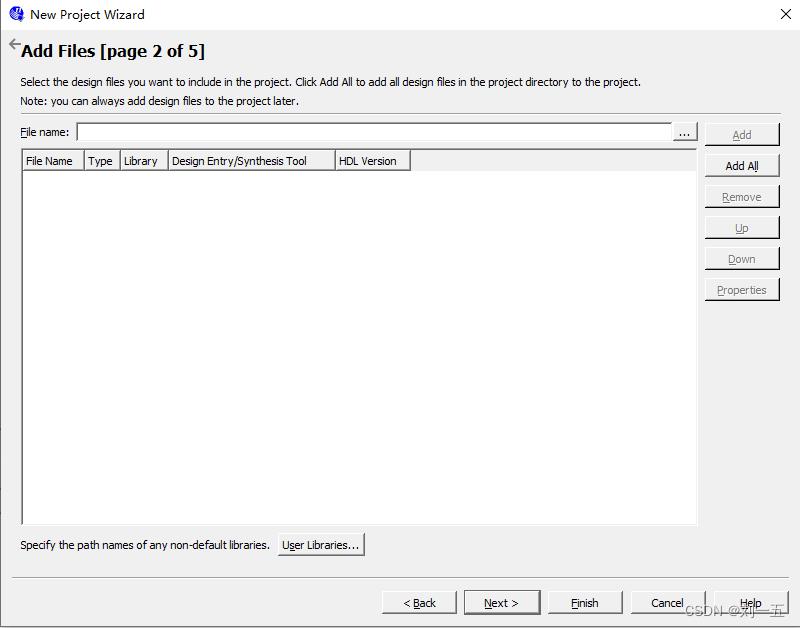

第二步:加入原先写好的文件,如若没有就直接点击下面的【next】即可

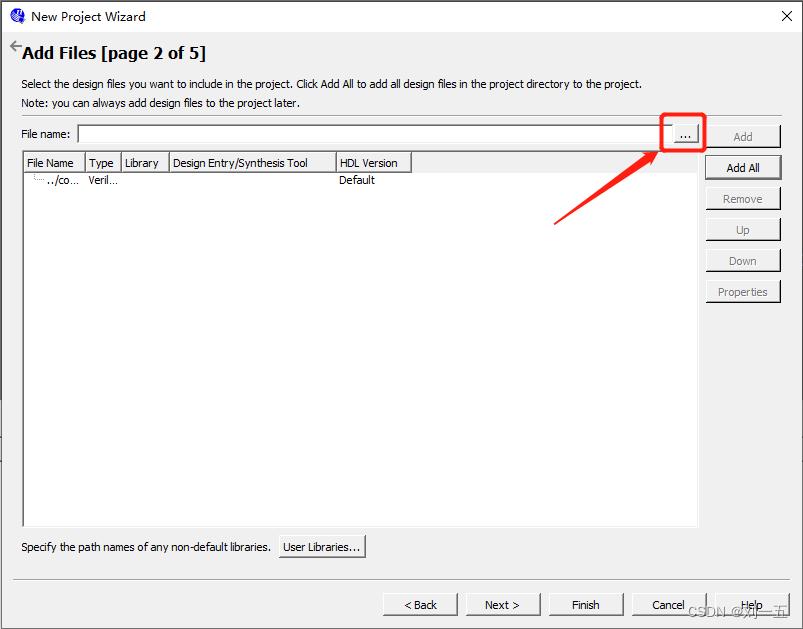

若要添加文件,则点击这个按钮

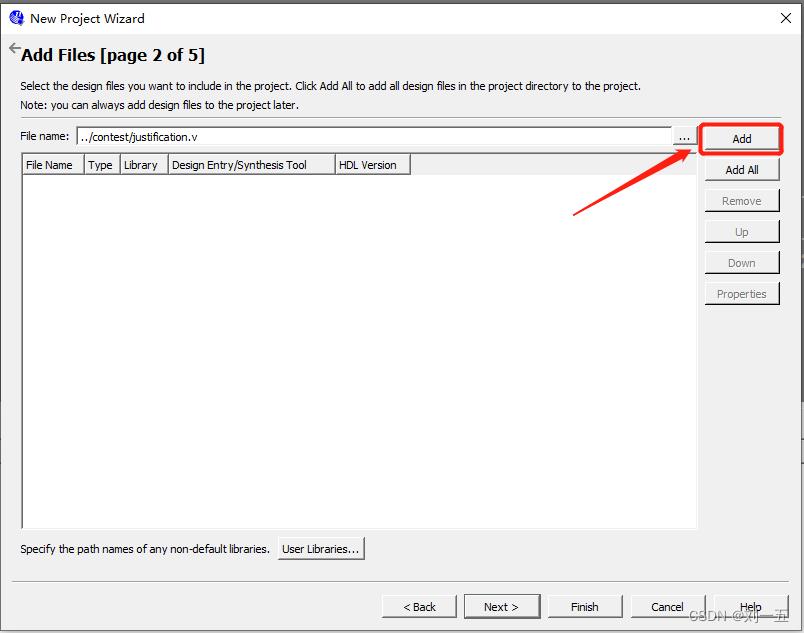

然后要记得点击【Add】不然添加进去的是一个只有文件名的空文件

第三步:根据试验箱上芯片的型号我选择【Cydone IV E】系列,设备型号【EP4CE6E22C8】。

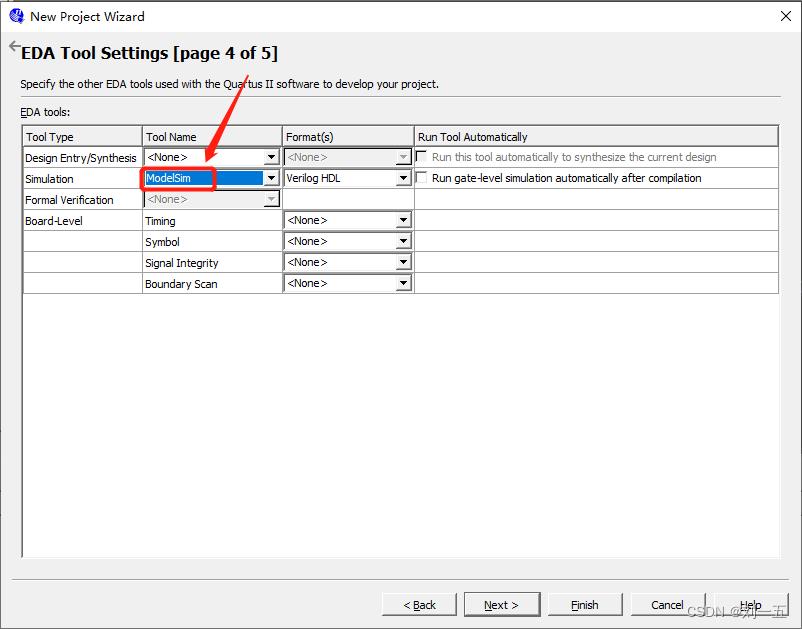

第四步:选择仿真模式为【ModelSim】

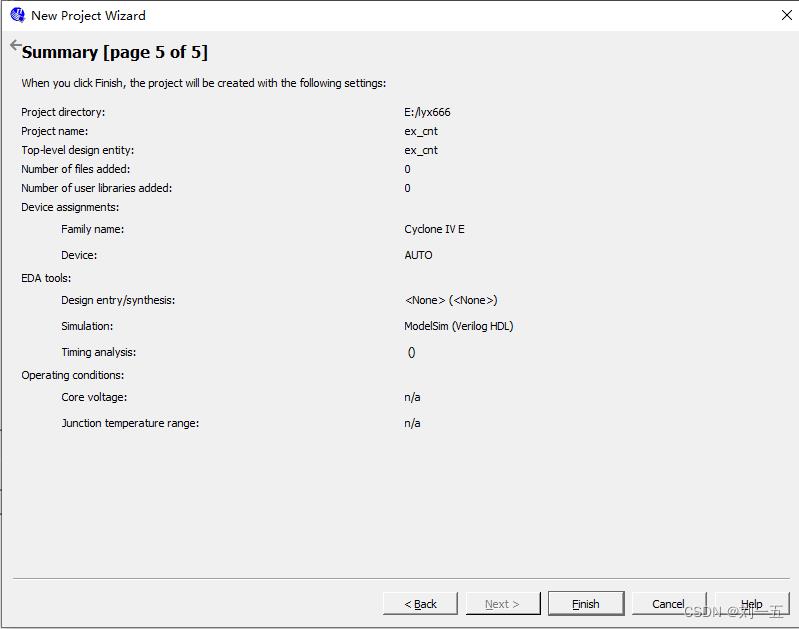

第五步:列出来刚刚的选择,确认无误后,点击【Finish】

到此,就完成了工程的新建。

二、编写程序

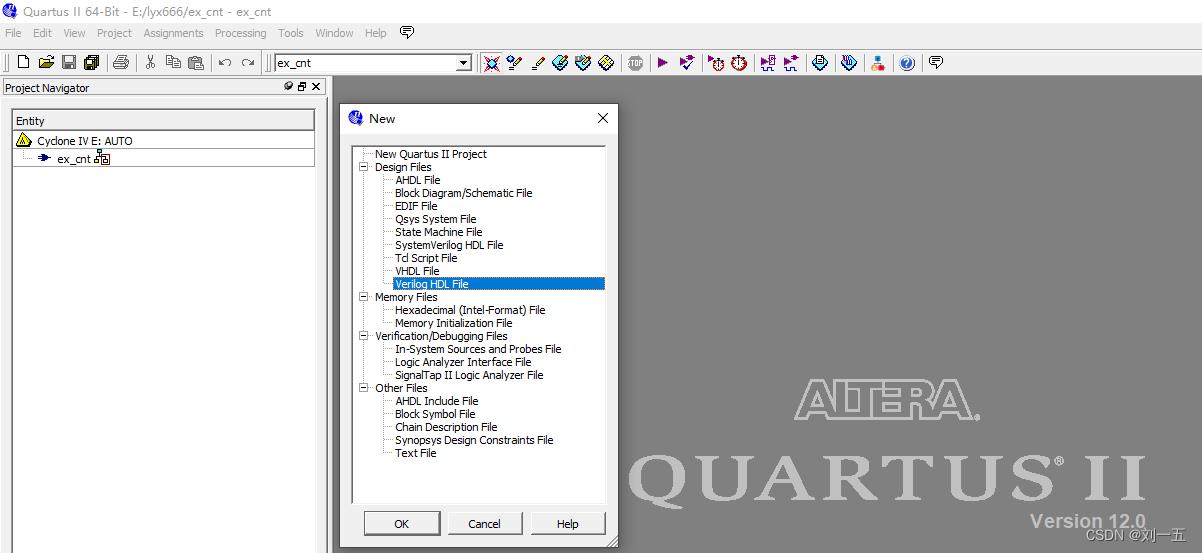

1、新建一个【Verilog HDL File】文件

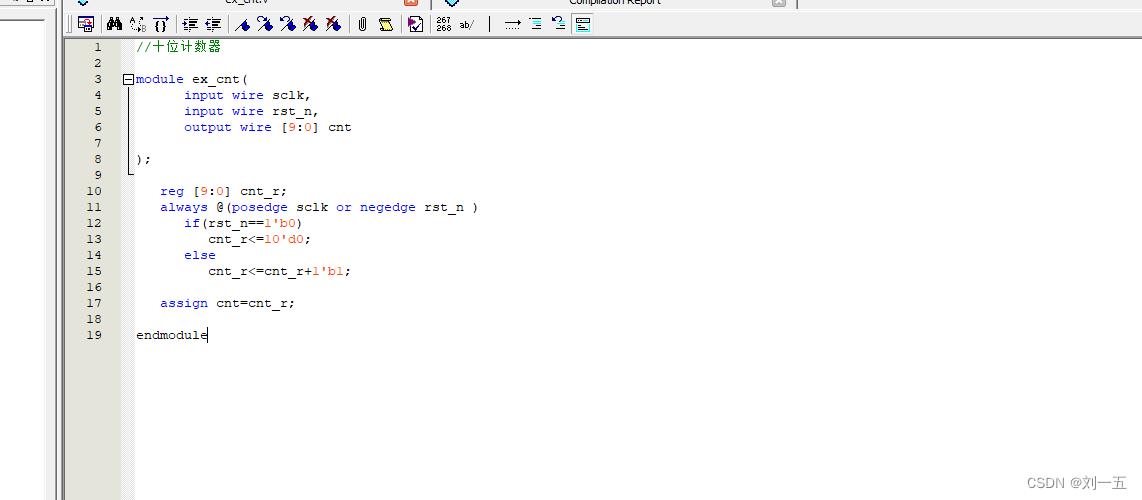

然后就开始码代码,以一个十位的计数器为例

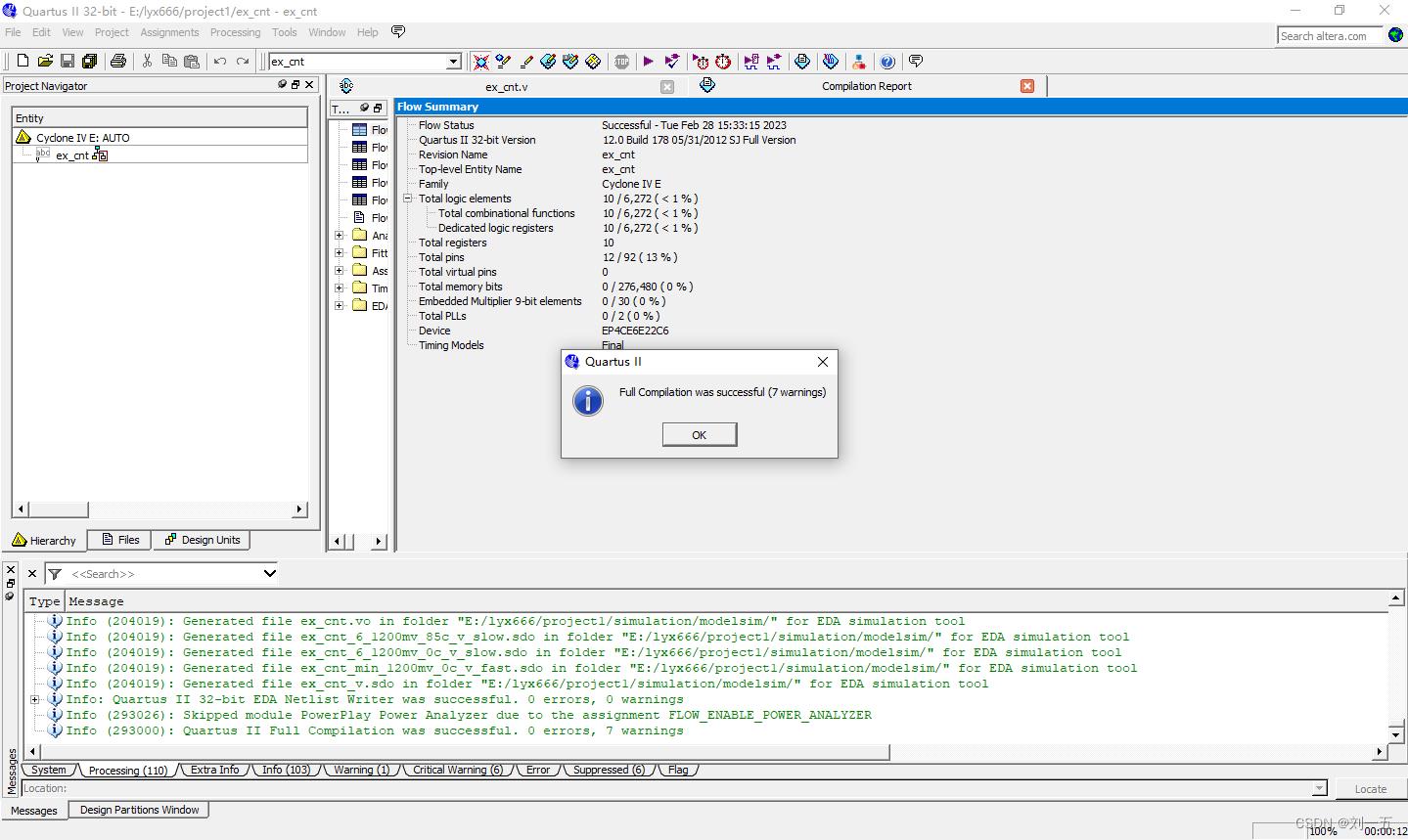

三、编译

点击菜单栏中的三角形进行编译

若编译无误则会弹出如下提示:

1、可以查看所用到的资源:

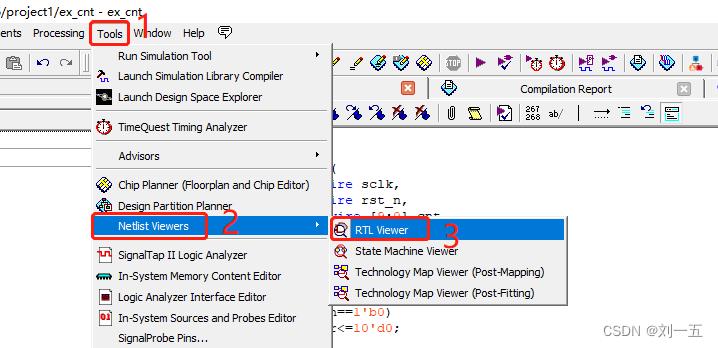

2、如何看生成的电路

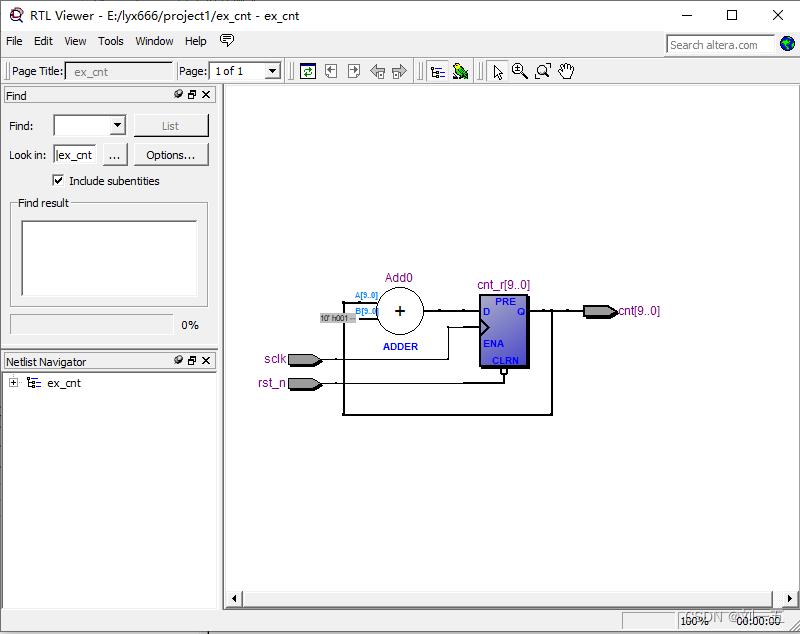

可以看到新建的电路如下:

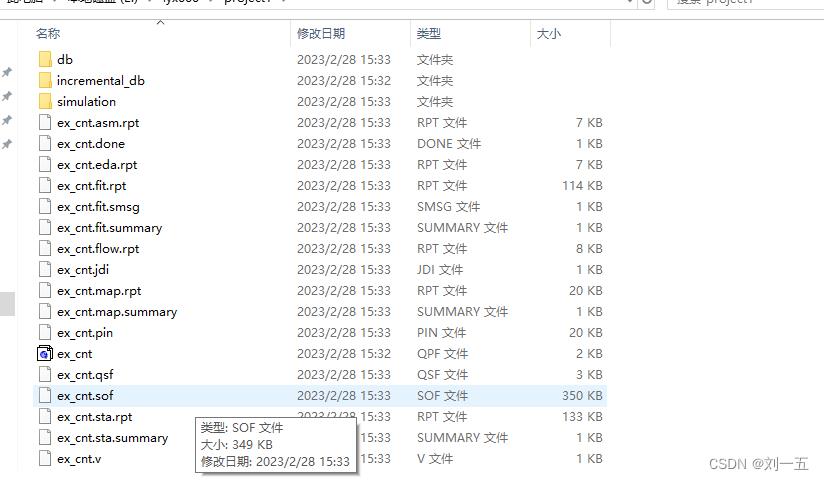

3、打开文件夹,可以看到需要烧录的文件

FPGA -- 实验一:闪烁灯

第一个实验就简单的实现一个灯闪烁的程序(主要也是为了回顾一下语法,仿真以及下载的流程)

基本思路是:利用计数器去计数0.5s,然后每隔0.5s改变以下LED输出引脚的电平状态

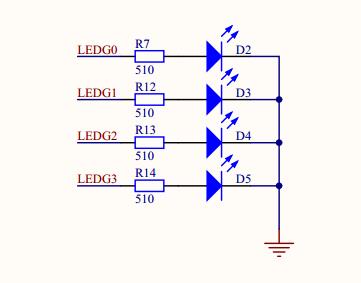

硬件电路如下:(与FPGA中的对应连接,在代码注释中给出)

1.在上次建立的那个设计文件里输入以下内容

(这个实验主要做一个演示,以后建工程等步骤不再赘述)

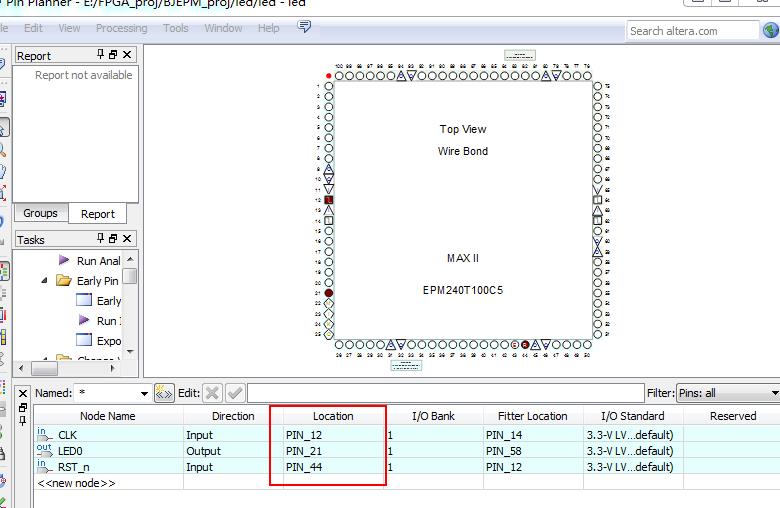

1 /********************************************* 2 *文件名:led.v 3 *功能:实现开发板上LED灯闪烁(闪烁频率为1s) 4 *平台:win7 64 quartus ii 64bit 5 *连接:CLK -- 12 6 RST_n -- 44 7 LED0 -- 21 8 *********************************************/ 9 10 module led( 11 CLK,RST_n, 12 LED0 13 ); 14 15 input CLK; 16 input RST_n; 17 output LED0; 18 19 //************************************ 20 //因为板子晶振为50M,0.5秒也就是要 21 //0.5*50*1000_000 = 25_000_000次计数 22 parameter half_sec = 25\'d25_000_000; 23 //************************************ 24 25 //************************************ 26 reg [24:0]count; 27 28 always @(posedge CLK or negedge RST_n) 29 begin 30 if(!RST_n) 31 count <= 25\'d0; 32 else if(count == half_sec) 33 count <= 25\'d0; 34 else 35 count <= count + 1\'b1; 36 end 37 38 //*********************************** 39 reg rLED0; 40 41 always @(posedge CLK or negedge RST_n) 42 begin 43 if(!RST_n) 44 rLED0 <= 1\'b0; 45 else if(count == half_sec) 46 rLED0 <= ~rLED0; 47 end 48 49 assign LED0 = rLED0; 50 51 52 endmodule

2.保存文件,并对该设计进行综合

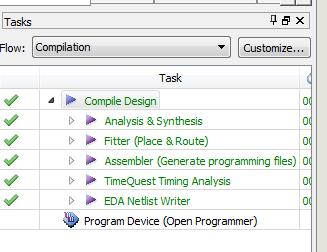

综合完成后,任务窗口会出现如下显示:

3.接下来分配引脚

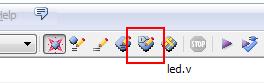

点击下列图标

显示如下:然后直接在图中标注部分,修改成开发板上的连接即可

修改完成后,关闭此界面。

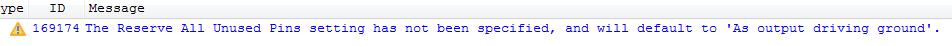

3.注意到,综合之后有一个警告:

这个是指对于没有用到的引脚的设置,一般我们要设置不用的引脚为:输入三态状态!

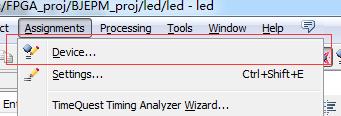

打开assignments--device

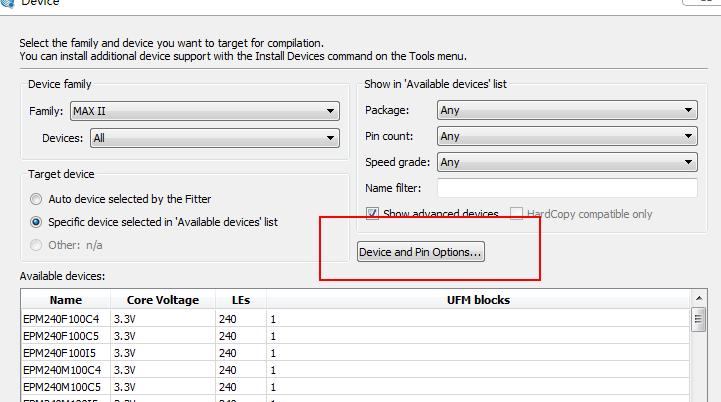

显示如下:点击device and pin options

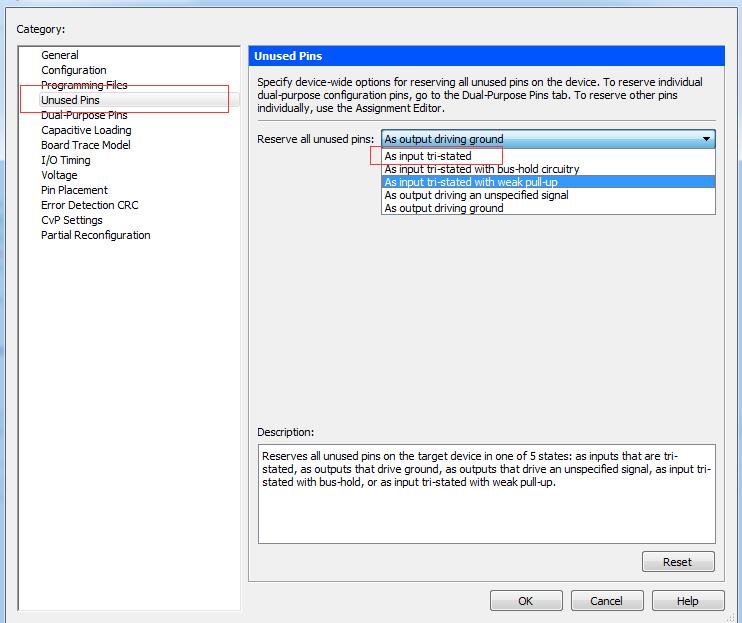

显示如下:选择unused pins里面的as input tri-stated

最后点击ok即可

以上是关于FPGA实验0Quartus建立工程文件以及仿真的主要内容,如果未能解决你的问题,请参考以下文章