STA:时序检查 - input2output型

Posted Starry丶

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了STA:时序检查 - input2output型相关的知识,希望对你有一定的参考价值。

目录

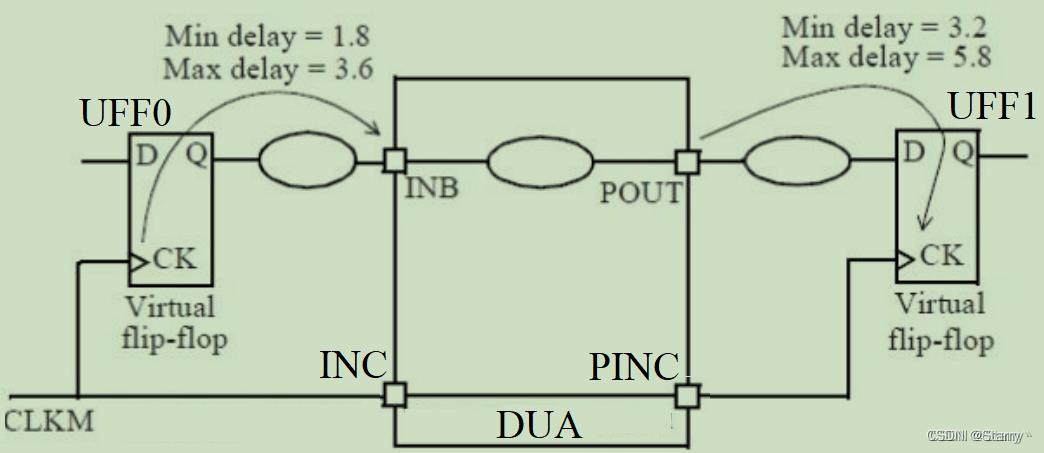

作STA要分析的时序路径四种中的一种,可看作是reg2reg的变种。详见STA:时序检查

4. input2output

第四种是发起触发器和捕获触发器都在芯片外部。

发起触发器到捕获触发器路径如下:

参数定义:

● T c l k 2 I N B T_clk2INB Tclk2INB:上升沿从时钟CLKM经过触发器UFF0传输到端口INB的延迟。

为端口INB相对于时钟CLKM的输入路径延迟,即 T c l k 2 I N B = T c l k 2 U F F 0 + T C K 2 Q U F F 0 + T U F F 02 I N B T_clk2INB=T_clk2UFF0+T^UFF0_CK2Q+T_UFF02INB Tclk2INB=Tclk2UFF0+TCK2QUFF0+TUFF02INB,通过下方SDC指定

# 最长路径,用于建立时间检查

set_input_delay -clock CLKM -max 1.5 [get_ports INB]

# 最短路径,用于保持时间检查

set_input_delay -clock CLKM -min 1 [get_ports INB]

● T I N B 2 P O U T T_INB2POUT TINB2POUT:数据从设计端口INB,经过一系列组合逻辑元件,最终到达POUT的延迟

取决于综合后端口INB到POUT之间的组合逻辑,组合逻辑延迟通过标准单元库的SDF指定。

● T P O U T 2 U F F 1 T_POUT2UFF1 TPOUT2UFF1:数据从设计端口POUT输出,经过一系列组合逻辑元件,最终到达UFF1的延迟

● T c l k 2 I N C T_clk2INC Tclk2INC:上升沿从时钟CLKM输入通过端口INC输入至设计内部的延迟。

此处INC为时钟定一点,所以该延迟就为源延迟,通过下方SDC指定

set_clock_latency 0.8 -source [get_clocks CLKM]

● T I N C 2 P I N C T_INC2PINC TINC2PINC:时钟CLKM在设计内部传输的延迟。

设计内部时钟的网络延迟,通过下方SDC指定

set_clock_latency 0.2 [get_clocks CLKM]

● T P I N C 2 U F F 1 T_PINC2UFF1 TPINC2UFF1:时钟CLKM通过端口PINC输出至UFF1的延迟。

● T c l k T_clk Tclk:时钟CLKM周期,注意该时钟并不是设计内部时钟。该值通过下方SDC指定

create_clock -period 10 -name CLKM [get_ports INC]

● T s e t u p _ u n c e r t a i n T_setup\\_uncertain Tsetup_uncertain:时钟CLKM建立时间不确定度,即预期时钟沿提前一段时间。

该值通过下方SDC指定

set_clock_uncertainty -setup 0.3 [get_clocks CLKM]

● T h o l d _ u n c e r t a i n T_hold\\_uncertain Thold_uncertain:时钟CLKM建立时间不确定度,即预期时钟沿延后一段时间。

该值通过下方SDC指定

set_clock_uncertainty -hold 0.4 [get_clocks CLKM]

● T s e t u p U F F 1 T^UFF1_setup TsetupUFF1:UFF1的建立时间。

● T o u t p u t U F F 1 T^UFF1_output ToutputUFF1:外部时序约束。POUT到UFF1/D端组合逻辑延迟与PINC到UFF1/CK端组合逻辑延迟的差,再加上UFF1的建立时间,即 T o u t p u t U F F 1 = T P O U T 2 U F F 1 − T P I N C 2 U F F 1 + T s e t u p U F F 1 / − T h o l d U F F 1 T^UFF1_output=T_POUT2UFF1-T_PINC2UFF1+T^UFF1_setup/-T^UFF1_hold ToutputUFF1=TPOUT2UFF1−TPINC2UFF1+TsetupUFF1/−TholdUFF1

可通过如下SDC指定

# 最长路径,用于建立时间检查

set_output_delay -clock CLKM -max 2 [ get_ports POUT]

# 最短路径,用于保持时间检查

set_output_delay -clock CLKM -min 1.5 [ get_ports POUT]

● T s e t u p _ s l a c k U F F 02 U F F 1 T^UFF02UFF1_setup\\_slack Tsetup_slackUFF02UFF1:路径UFF0-UFF1的建立时间裕度。为待计算量,大于零表示建立时间满足。

● T h o l d U F F 1 T^UFF1_hold TholdUFF1:UFF1的保持时间。

● T h o l d _ s l a c k U F F 02 U F F 1 T^UFF02UFF1_hold\\_slack Thold_slackUFF02UFF1:路径UFF0-UFF1的保持时间裕度

4.1. 建立时间 T s e t u p T_setup Tsetup检查

对捕获触发器UFF1进行STA

● 数据实际到达UFF1/D端的时间(Arrival Time): T c l k 2 I N B + T I N B 2 P O U T + T P O U T 2 U F F 1 T_clk2INB+T_INB2POUT+T_POUT2UFF1 Tclk2INB+TINB2POUT+TPOUT2UFF1

reg2reg型中的Arrival Time为 T c l k 2 U F F 0 + T C K 2 Q U F F 0 + T U F F 02 U F F 1 T_clk2UFF0+T^UFF0_CK2Q+T_UFF02UFF1 Tclk2UFF0+TCK2QUFF0+TUFF02UFF1,与input2reg型中的Arrival Time等价

● UFF1/D端新信号需要到达的时间(Required Time):

T

c

l

k

−

T

s

e

t

u

p

_

u

n

c

e

r

t

a

i

n

+

T

c

l

k

2

I

N

C

+

T

I

N

C

2

P

I

N

C

+

T

P

I

N

C

2

U

F

F

1

−

T

s

e

t

u

p

U

F

F

1

T_clk-T_setup\\_uncertain+T_clk2INC+T_INC2PINC+T_PINC2UFF1-T^UFF1_setup

Tclk配置STA环境(下)

文章目录

7.6 时序路径组(Timing Path Groups)

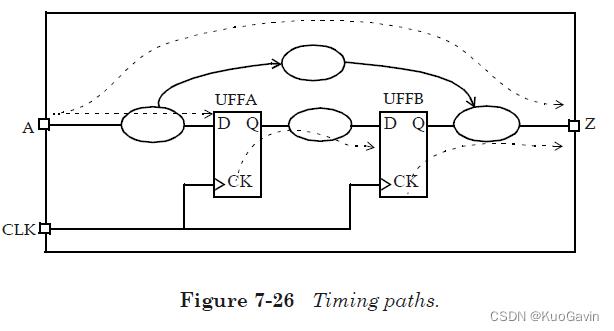

一个设计中的时序路径可视为一组路径。每个路径有一个起点(startpoint)和终点(endpoint)。图7-26展示了一些示例路径。

在STA中,时序路径是根据有效起点和终点来划分的。有效的起点包括:输入端口或者同步器件(如触发器(flip-flops)和存储器(memories))的时钟引脚。有效的终点包括:输出端口或者同步器件的数据输入引脚。因此,有效的时序路径可以是:

- i i i. 从输入端口到输出端口;

- i i ii ii. 从输入端口到触发器或存储器的数据输入引脚;

- i i i iii iii. 从触发器或存储器的时钟引脚到触发器或存储器的数据输入引脚;

- i v iv iv. 从触发器的时钟引脚到输出端口;

- v v v. 从存储器的时钟引脚到输出端口;

图7-26中的的有效时序路径有:

- 输入端口 A A A到触发器数据输入引脚 U F F A / D UFFA/D UFFA/D;

- 输入端口 A A A到输出端口 Z Z Z;

- 触发器时钟引脚 U F F A / C K UFFA/CK UFFA/CK到触发器数据输入引脚 U F F B / D UFFB/D UFFB/D;

- 触发器时钟引脚 U F F B / C K UFFB/CK UFFB/CK到输出端口 Z Z Z;

时序路径根据路径终点所相关的时钟被分为不同时序路径组(path groups)。因此,每个时钟都有一组与之相关的时序路径。这里还有一个默认时序路径组(default path group),包含了所有非时钟/异步(non-clock/asynchronous)路径。

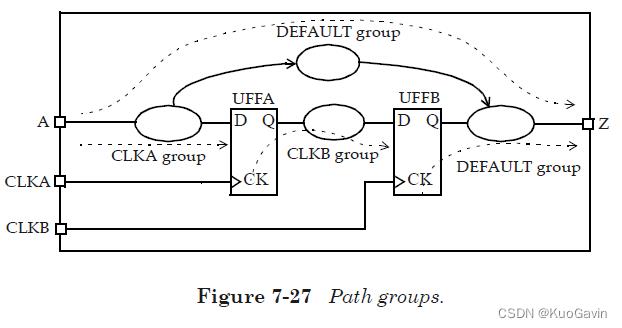

在图例7-27中,时序路径组有:

- C L K A CLKA CLKA组:输入端口 A A A到触发器数据输入引脚 U F F A / D UFFA/D UFFA/D;

- C L K B CLKB CLKB组:触发器时钟引脚 U F F A / C K UFFA/CK UFFA/CK到触发器数据输入引脚 U F F B / D UFFB/D UFFB/D;

- D E F A U L T DEFAULT DEFAULT组:输入端口 A A A到输出端口 Z Z Z;触发器时钟引脚 U F F B / C K UFFB/CK UFFB/CK到输出端口 Z Z Z;

静态时序分析和报告通常按照时序路径组来分别执行。

7.7 外部属性建模(Modeling of External Attributes)

尽管create_clock、set_input_delay和set_output_delay足以约束设计中用于执行时序分析的所有路径,但这些并不足以获取该模块

I

O

IO

IO引脚上的准确时序。为了准确地对设计环境进行建模,还需要以下属性。对于输入,需要在输入端口处指定压摆(slew)。可以使用以下方式提供此信息:

- set_drive:该命令已经过时且不推荐;

- set_driving_cell;

- set_input_transition;

对于输出,我们需要指明输出引脚的电容负载。可由如下命令进行指定:

- set_load;

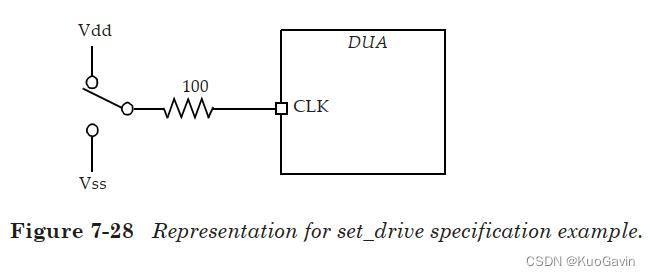

7.7.1 驱动强度建模(Modeling Drive Strengths)

set_drive和set_driving_ cell约束用于对驱动模块输入端口的外部单元的驱动强度进行建模。在没有这些约束的默认情况下,假定所有输入都具有无限的驱动强度,即输入引脚的过渡时间为

0

0

0。

set_drive明确指定了

D

U

A

DUA

DUA输入引脚上的驱动电阻值,该电阻值越小,驱动强度越高,电阻值为

0

0

0则表示无限的驱动强度。

set_drive 100 UCLK

# Specifies a drive resistance of 100 on input UCLK.

# Rise drive is different from fall drive:

set_drive -rise 3 [all_inputs]

set_drive -fall 2 [all_inputs]

输入端口的驱动强度用来计算第一个单元的过渡时间。所指定的驱动数值还可用来计算从输入端口到第一个单元的延迟值,在存在 R C RC RC互连的情况下。

D e l a y _ t o _ f i r s t _ g a t e = ( d r i v e ∗ l o a d _ o n _ n e t ) + i n t e r c o n n e c t _ d e l a y Delay\\_to\\_first\\_gate=(drive*load\\_on\\_net)+interconnect\\_delay Delay_to_first_gate=(drive∗load_on_net)+interconnect_delay

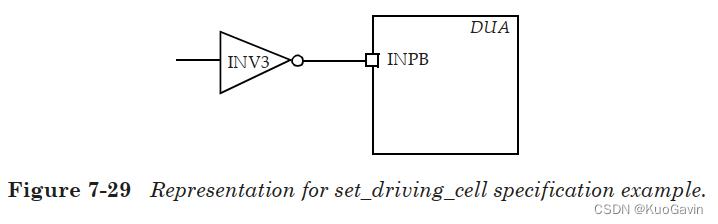

set_driving_cell约束提供了一个更加方便和准确的描述一个端口的负载能力的方式。set_driving_cell可以用来约束一个单元驱动一个输入端口。

set_driving_cell -lib_cell INV3 \\

-library slow [get_ports INPB]

# The input INPB is driven by an INV3 cell

# from library slow.

set_driving_cell -lib_cell INV2 \\

-library tech13g [all_inputs]

# Specifies that the cell INV2 from a library tech13g is

# the driving cell for all inputs.

set_driving_cell -lib_cell BUFFD4 -library tech90gwc \\

[get_ports testmode[3]]

# The input testmode[3] is driven by a BUFFD4 cell

# from library tech90gwc.

与set_drive约束一样,set_driving_cell也可用于计算第一个单元的过渡时间,并在任何互连情况下计算从输入端口到第一个单元的延迟值。

使用set_driving_cell约束的一个注意点是:由于输入端口上的电容性负载而导致驱动单元的增量延迟被视作为输入上的附加延迟被包括在内。

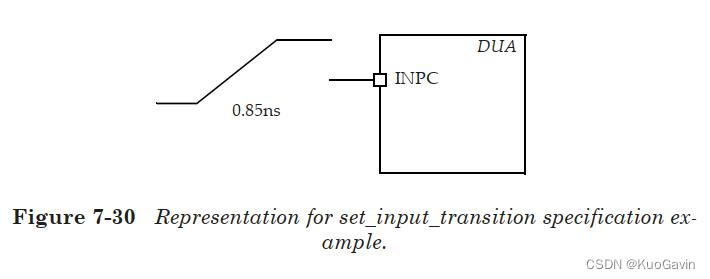

作为上述方法的替代方法,set_input_transition约束提供了一种在输入端口表示过渡时间的便捷方法,并且可以指定参考时钟。以下是图7-30中示例的约束以及其它约束示例:

set_input_transition 0.85 [get_ports INPC]

# Specifies an input transition of 850ps on port INPC.

set_input_transition 0.6 [all_inputs]

# Specifies a transition of 600ps on all input ports.

set_input_transition 0.25 [get_ports SD_DIN*]

# Specifies a transition of 250ps on all ports with

# pattern SD_DIN*.

# Min and max values can optionally be specified using

# the -min and -max options.

总之,输入端的偏斜值需要指定来确定输入路径中的第一个单元的时延。如果缺失该约束,则假定时延值为现实中不会存在的 0 0 0。

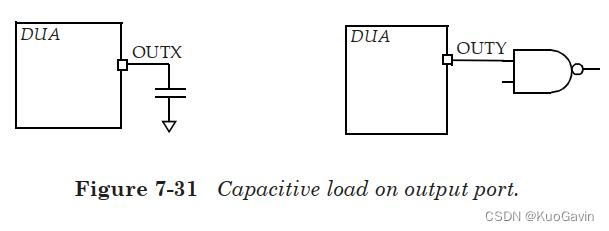

7.7.2 电容负载建模(Modeling Capacitive Load)

set_load指令在输出端口放置一个电容负载以对输出端口所驱动的外部负载进行建模。默认情况下,输出端口的电容负载是

0

0

0。负载可以明确指定为具体的电容值或一个单元输入引脚电容。

set_load 5 [get_ports OUTX]

# Places a 5pF load on output port OUTX.

set_load 25 [all_outputs]

# Sets 25pF load capacitance on all outputs.

set_load -pin_load 0.007 [get_ports shift_write[31]]

# Place 7fF pin load on the specified output port.

# A load on the net connected to the port can be

# specified using the -wire_load option.

# If neither -pin_load nor -wire_load option is used,

# the default is the -pin_load option.

指定输出端口的负载值很重要因其影响到驱动输出的单元的延迟。若是缺失该指定值,则输出负载为 0 0 0的假定是与现实不符的。

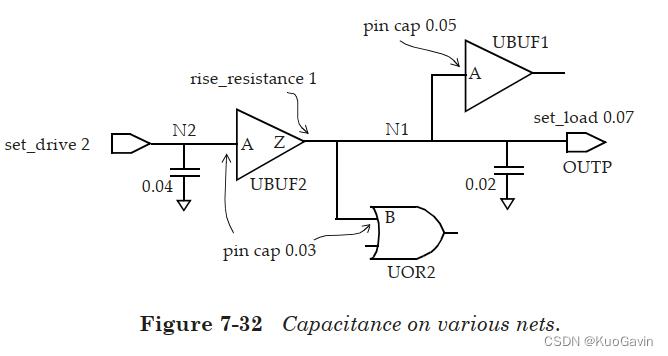

set_load同样可以用来指定一个设计中内部网络的负载。例子如下:

set_load 0.25 [get_nets UCNT5/NET6]

# Sets the net capacitance to be 0.25pF.

7.8 设计规则检查(Design Rule Checks)

STA中两个常用的设计规则是最大过渡时间-max_transition和最大电容-max_capacitance。这些规则将会检查设计中的所有端口和引脚是否满足过渡时间和电容的规定约束。这些规则可以使用以下命令指定:

- set_max_transition;

- set_max_capacitance;

作为STA的一部分,任何对这些设计规则的违例将会用裕量(slack)的形式报告。例子如下:

set_max_transition 0.6 IOBANK

# Sets a limit of 600ps on IOBANK.

set_max_capacitance 0.5 [current_design]

# Max capacitance is set to 0.5pf on all nets in

# current design.

一个网络的电容是通过所有引脚电容加上所有 I O IO IO负载再加上网络上的任何互连电容的总和计算得出的。图7-32便是一个例子。

T o t a l c a p o n n e t N 1 = p i n c a p o f U B U F 1 : p i n / A + p i n c a p o f U O R 2 : p i n / B + l o a d c a p s p e c i f i e d o n o u t p u t p o r t O U T P + w i r e r o u t i n g c a p = 0.05 + 0.03 + 0.07 + 0.02 = 0.17 p F \\beginalign* & Total\\,\\,cap\\,\\,on\\,\\,net\\,\\,N1=pin\\,\\,cap\\,\\,of\\,\\,UBUF1:pin/A\\,\\,+ \\\\ & \\ \\ \\ \\ pin\\,\\,cap\\,\\,of\\,\\,UOR2:pin/B\\,\\,+ \\\\ & \\ \\ \\ \\ load\\,\\,cap\\,\\,specified\\,\\,on\\,\\,output\\,\\,port\\,\\,OUTP\\,\\,+ \\\\ & \\ \\ \\ \\ wire\\,\\,routing\\,\\,cap \\\\ & \\ \\ \\ \\ =0.05+0.03+0.07+0.02 \\\\ & \\ \\ \\ \\ =0.17pF \\endalign* TotalcaponnetN1=pincapofUBUF1:pin/A+ pincapofUOR2:pin/B+ loadcapspecifiedonoutputportOUTP+ wireroutingcap =0.05+0.03+0.07+0.02 =0.17pF

T o t a l c a p o n n e t N 2 = p i n c a p o f U B U F 2 / A + w i r e r o u t i n g c a p f r o m i n p u t t o b u f f e r = 0.04 + 0.03 = 0.07 p F \\beginalign* & Total\\,\\,cap\\,\\,on\\,\\,net\\,\\,N2\\,\\,= \\\\ & \\ \\ \\ \\ pin\\,\\,cap\\,\\,of\\,\\,UBUF2/A\\,\\,+ \\\\ & \\ \\ \\ \\ wire\\,\\,routing\\,\\,cap\\,\\,from\\,\\,input\\,\\,to\\,\\,buffer \\\\ & \\ \\ \\ \\ =0.04+0.03 \\\\ & \\ \\ \\ \\ =0.07pF \\endalign* TotalcaponnetN2= pincapofUBUF2/A+ wire以上是关于STA:时序检查 - input2output型的主要内容,如果未能解决你的问题,请参考以下文章