FPGA教程案例23基于FIFO核的跨时钟域数据传输

Posted fpga和matlab

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了FPGA教程案例23基于FIFO核的跨时钟域数据传输相关的知识,希望对你有一定的参考价值。

---------------------------------------------------------------------------------------

1.软件版本

vivado2019.2

2.本算法理论知识

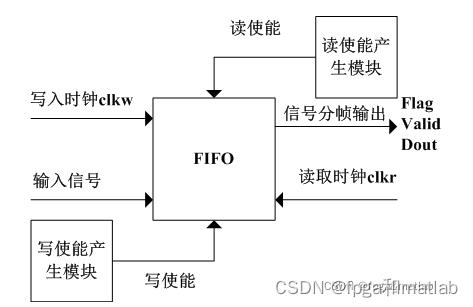

信号从一个时钟域同步到另一个时钟域,并且保证所有的信号到新时钟域中的同一时钟周期,这是一个关键问题。FIFO通过一个时钟域的控制信号将数据存入FIFO缓存中,并通过第二个时钟域的控制信号将数据从同一FIFO缓存的另外一端读取并删除。基于FIFO的跨时钟域数据传输,其原理图如下所示:

FIFO的工作流程分为写入FIFO和从FIFO读取两个部分。在数据写入过程中,系统的控制模块产生一个写使能信号,当使能为高电平时,数据被写入到FIFO中。当FIFO写满N个数据之后,系统控制器产生一个读使能信号,从FIFO中读取N个数据。在读取第一个数据时,flag产生一个高电平,表示帧头位置,同时v

以上是关于FPGA教程案例23基于FIFO核的跨时钟域数据传输的主要内容,如果未能解决你的问题,请参考以下文章