从 MLPerf 谈起:如何引领 AI 加速器的下一波浪潮

Posted AI科技大本营

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了从 MLPerf 谈起:如何引领 AI 加速器的下一波浪潮相关的知识,希望对你有一定的参考价值。

作者 | OneFlow社区

来源 | OneFlow社区

在深度学习史上,专用化硬件至少在AlexNet和Transformers这两个革命性时刻发挥了关键作用,介绍这两种架构的论文都在其摘要中强调了GPU的作用,并详细说明了它们如何将底层计算并行化到多个GPU中,以加快计算速度。

之所以要强调这一点,是因为早在AlexNet论文发表的20年前,应用于计算机视觉的深度卷积神经网络就已经诞生了;同样,早在Transformers论文发表前,应用于自然语言处理的LSTMs、RNNs和自注意力机制(self-attention mechanism)也已存在,这说明许多算法基础早就已经有了。

然而,通过展示如何以合理的成本进行大规模计算,论文作者们在上述领域取得了进一步突破。究其原因,是他们掌握了AI加速的革命性本质:扩展到日用品(Scale-to-Commodity)。

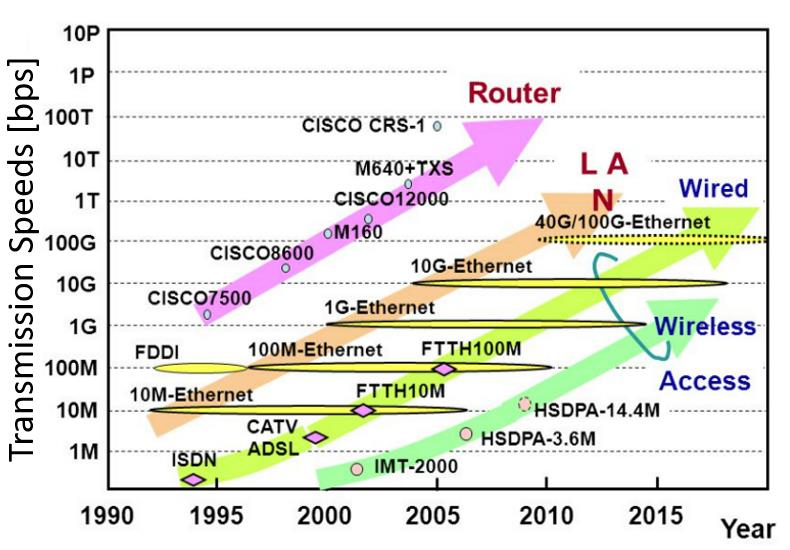

25年来,路由器、有线和无线的网络速率增长了1000倍

虽然提高单位成本的性能一直是计算机科学家和工程师们的长期目标,但在某些情况下,收益会改变游戏规则,一些过去认为不可能成为日用品的东西会变成日用品。

当芯片性能提高100倍,意味着你在两个小时内就可以运行一个复杂的模型,而过去你却得耗费一周时间,甚至可能需要100个基于CPU的工作站(假设你能够掌握所有这些并行化并支付昂贵的电费)。

过去20年,由于互联网带宽增加了1000多倍,我们的生活也发生了翻天覆地的变化。你能想象,以前人们需要等待好几个小时才能下载完自己喜欢的电视剧吗?简直太煎熬了。

为了保持AI的革命性本质,我们需要考虑哪些模型可以日用品化以及如何将它们日用品化。

1

AI基准测试的缺陷

近年来,我们见证了MLPerf的兴起,这是一个旨在对AI硬件和系统供应商报告的性能数据进行标准化的基准测试组件。它由来自70多家头部科技公司(英伟达、谷歌、AMD和英特尔)、多家初创公司(SambaNova、Cerebras和Graphcore)以及各大学术机构(斯坦福、哈佛和伯克利)等众多行业领导者共同发起。

MLPerf基准测试包括ResNet50和BERT等多个AI应用,并就不同版块进行评估,包括数据中心训练、数据中心推理和移动设备推理等等。每隔几个月,MLPerf就会收到各大公司和机构提交的测试结果(主要涉及应用运行时间),然后他们会把结果推送给相应的领域。这样,提交者们就可以根据MLPerf竞赛评估各自的表现,一些潜在客户也能挑选出更符合自身需求的AI系统。

MLPerf有一项雄心勃勃的使命宣言:基于真实的模型、公开的数据集和易于理解的指标,为用户提供标准化和无偏见的性能推理方法,从而推动AI的应用。

随着AI硬件更加普及,我们迫切需要更多的行业标准和指标去了解AI硬件的性能。虽然MLPerf在性能评估方面已经做得不错了,但我还想提三项可扩大其影响力的改进措施。

1、规范化

AI加速器五花八门,不同用户(业余爱好者、研究生、大型企业等)和系统(移动设备、工作站、自动驾驶汽车、HPC/云等)的需求也有很大差异。

此外,构建加速器的方法多种多样,给出一个计算域,你就可以尽情发挥自己的想象力和创造力来协同设计硬件和软件(当然,你还得考虑市场需求和成本)。由于AI加速器和系统多种多样,单是比较不同的加速技术就已经相当不易,更不用说定义一种公平、无偏见的加速器对比标准了。

IEEE spectrum曾发布了一篇名为《AI训练正在超越摩尔定律》的文章(https://spectrum.ieee.org/ai-training-mlperf),该观点基于MLPerf公布的测试结果。摩尔定律认为,晶体管密度每隔18个月就会增加约2.2倍,但MLPerf公布的数据却显示,AI训练的结果在18个月内提升了16-27倍。

于是,马上就有人说,“如果我们比摩尔定律快这么多,那么大部分的性能提升肯定都不是因为我们使用了更好的半导体技术,而是因为采用了更好的加速方法和软件技术。”然而,他们的结论并不可靠。因为他们没有规范化的标准来衡量性能,所以才忽视了硬件对性能优化所做的贡献。

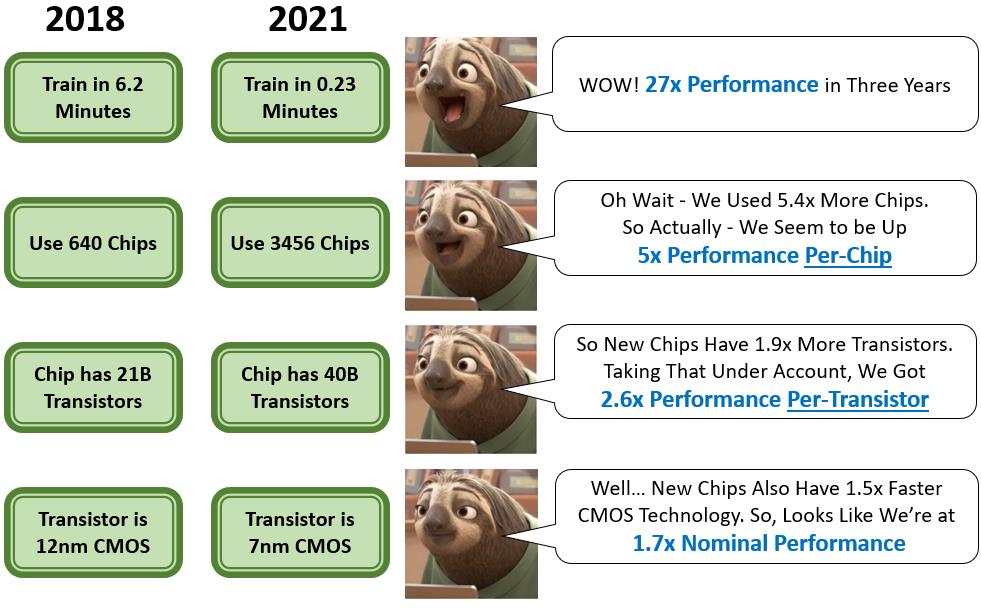

ResNet50训练结果的逐步规范化

让我们深入解读一下这些数字。以ResNet50的数据中心训练为例,2018年,MLPerf基线结果是使用640个NVIDIA V100 GPU达到的6.2分钟,而在2021年,时间减少到了0.23分钟。单从数字来看,速度的确是快了约27倍,但这是因为使用了3456个TPU v4加速器,这意味着加速器的数量增加了5.4倍。因此,如果我们将这一标准运用到每一个芯片上,实际性能仍会提高5倍,这非常了不起。

另外,一个V100 GPU芯片上有211亿个晶体管,虽然谷歌在TPU规格方面并没有透露太多,但其与TPUv4竞争的训练芯片(NVIDIA A100、SambaNova SN10、Graphcore mk2 IPU等)的晶体管数量在400-600亿个左右。

因此,我们可以合理地假设TPUv4也拥有这么多晶体管,它可以提供每秒275万亿浮点运算的峰值性能,所以保守估计TPUv4有400亿个晶体管,于是我们会推出来每一个晶体管性能提升了2.6倍左右。

最后,V100是使用12纳米CMOS技术制造,而TPUv4很可能是使用7纳米CMOS技术制造的(如TPUv4i)。ITRS和其他学术研究认为,7纳米的电路应该比12纳米的电路快1.5倍。因此,考虑到所有这些因素,包括更多的预算,更快和更优的硬件能力,架构帮助性能提升大约只有1.7倍左右。

显然,这是一个一阶近似值(first-order approximation),实际性能是由计算半导体技术以外的许多因素决定的,比如内存带宽、缓存、通信带宽和拓扑结构等。更复杂的系统确实需要由更精细和更成熟的软件堆栈来管理,增加芯片或晶体管的数量并不能保证性能有同等倍数的提升。我们必须有这样的思维,才能更好地理解规范化,以及通过晶体管实现性能优化。

为什么靠规范晶体管优化性能如此迫切?原因主要以下四点:

1、这就是加速器存在的意义。如果有一天,晶体管技术真的会像随摩尔定律所说的那样停止发展,未来我们就只有基于硅基技术陷入停滞的前提下实现性能优化;

2、如果缺少公平的比较方法,成绩就只是数字而已,就像一个骑自行车的人和一个开兰博基尼的人之间的比赛毫无意义;

3、芯片的性能不可能无限制地提升,当加速器供应商开发出系列加速器时,他们需要评估每一代加速器的硬件、软件堆栈,从而找出更新换代能够为性能优化所做的真实贡献。同时,还需要知道,有时他们将不再为同一问题提出更好的解决方案,并且会遇到芯片专用化回报的递减以及撞上“加速器墙”;

4、试图在一个问题上投入大量资金从而提高性能的做法不可取,MLPerf只有坚持自己的加速愿景,并推动AI复兴进入第一阶段——扩展到日用品,才能继续维护自己的价值。

AlexNet和Transformers为使用单一系统训练复杂模型打开了大门,并引领了新一轮突破。我们需要更加重视规范化的性能指标,比如单位功率性能或单晶体管性能。我们已经在单位功率性能方面做了些许尝试,但是这样的工作似乎不太有吸引力。功率测量比较麻烦,而且在这方面取得突破也不会像创下新的训练时间纪录那样引起轰动。

最后,虽然知道绝对性能数字是件好事,但普通数据科学家真的关心如何在千万亿级系统(拥有他们负担不起的数千处理器)上提高执行时间吗?这引出了我们后续的讨论。

2. 大众化

MLPerf基准测试涉及的应用,主要是2012至2018年间发表的学术研究论文中提到的模型,而GPU作为当时深度学习唯一可行的选择,那些论文中的数据都是模型在GPU上运行的性能结果。

而且,论文涉及的底层架构特征、超参数和架构规模都会根据GPU来配置,模型的优点会与GPU的架构优点相结合,当然,最终的测试结果也会受GPU的缺点所限制。

如此一来,MLPerf竞赛本质上其实更类似于“GPU竞赛”,也让GPU从此成为了AI硬件的代名词。

不要误解我的意思——我们都应该重视GPU,因为它是现代AI的开路先锋。如果没有GPU成熟的硬件/软件堆栈,也就根本不会见证AI应用的崛起。但除了GPU,我们现在还有其他的解决方案,我们也应该探索在其他类型的架构上开发的原生模型的属性,它们可以开辟出一些新领域。

此外,我们可能也不希望只有单一的软件实施方案,或单一类型的架构,这决定了整个AI应用领域的成果和局限性。可以假设,如果在2010年就已经存在TPU和TensorFlow生态系统,那MLPerf的应用范围也会有不同。

3. 泛化

“When a measure becomes a target, it ceases to be a good measure(当一项指标变成目标,它将不再是一个好的指标。)”-Charles Goodhart

MLPerf需要克服的最后一个挑战是缺乏应用泛化。大约一年前,我调研了一家业内领先的AI硬件供应商的性能评估。经验告诉我,要想达到预期性能并非易事。

当时的情况是,即使在一个新的Docker镜像上安装了所有最新的库,重现参加过MLPerf的模型的跑分也没能接近他们公布的分数。只有使用供应商从专门的库中提供的模型版本,并且手动配置文件覆盖掉编译器对模型的决策后,才有可能达到他们公布的分数。

最后,当我用了另一款模型替换了供应商提供的模型(两款模型的层数和大小几乎完全相同),并且进行了相同的配置后,却发现性能下降了50%左右。我听说,其他朋友在使用别的供应商提供的一些模型时也有过类似经历。

使用基准问题测试“慢动目标”(slow-moving targets)会出现上述不理想的结果,这并不奇怪。

目前,MLPerf基准测试已经连续三年使用同一组应用,因此供应商只需要在测试时给这些应用展示一些不符合实际的“一次性”性能,就能跑出不错的成绩;大多数的数据科学家也并非真的了解底层硬件、编译器和软件库,所以他们不会花费数周进行性能调优,更不用说创建覆盖编译器决策的手动配置文件了。

AI面临的主要挑战之一是实现“用户到硬件的表达(user-to-hardware-expressiveness)”。AI领域发展飞速,每天都有数百篇新研究论文发表,所以我们需要对堆栈进行泛化,从而保证它们能够“开箱即用”地运行更多性能良好的用例,而不是仍旧专注于十年前的应用。

MLPerf应该更加重视,数据科学家们需要的是强大的加速堆栈(acceleration stack),这些加速堆栈可以利用底层硬件来处理空前庞大的工作量。

目前,大多数AI硬件供应商都是优先考虑客户模型和需求,而非MLPerf应用。如果MLPerf再不采取更普遍、更大众化的方式,势必会遇到更多竞争对手,并且人们最终也将不再愿意将其视为行业级基准。

2

重新思考硬件加速

硬件加速一直是推动AI领域发展的关键因素之一,因此了解硬件加速的基本假设、现有概念局限性以及新发展方向,对于推动AI领域进一步发展至关重要。

跨越创新鸿沟

AI领域是研究驱动型的,因此工业界和学术界之间有着紧密的共生关系。生产系统中所使用的最前沿的AI模型及其理论都出自发表在NeurIPS、ICML、CVPR和ICLR等顶级学术会议上的论文,包括AlexNet、ResNet、YOLO、Transformers、BERT、GPT-3、GANs和 Vision Transformers。此外,其中不少论文都是由学术机构与谷歌、脸书、英伟达和微软等公司的研究实验室合作的成果。

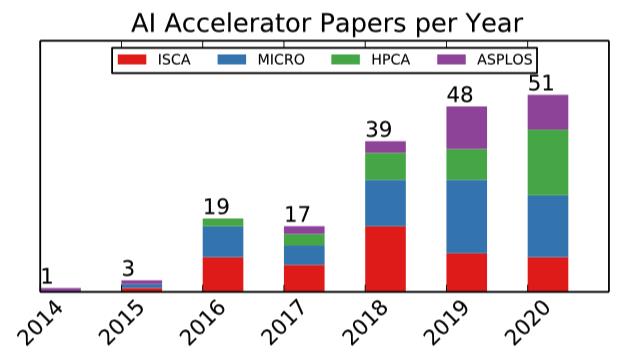

与AI应用领域相比,工业界在AI加速器领域一直落后于学术界。虽然ISCA、MICRO、HPCA和ASPLOS等计算机体系结构顶级会议每年都会刊登数十篇关于加速器的新论文,但生产中部署的加速器的核心架构思想几十年前就诞生了,包括内存处理、数据流计算、脉动阵列、VLIW等等。

我们需要积攒更多的想法和创新,并将其具体化为新的产品。新想法的采纳总是很缓慢,这是因为制造芯片需要数年之久,而且AI硬件领域竞争激烈,采纳新想法意味着可能需要耗费巨大成本改变现有的一些功能,这样做风险很大。

然而,现在的AI加速器领域已经趋于成熟,一些必需的基础已经奠定,我们也知道怎样做才有效。因此,供应商们是时候尝试一些新想法了,通过新的发现来推动AI加速器领域发展。要相信,AI加速器领域仍有创新空间!

让AI加速真正作用于AI

现代AI已经激发了我们的兴趣,它让我们思考未来无限的可能性,并提出了一些关于哲学、社会学和伦理学的问题,这些领域的大牛们也在激烈讨论:AI可以做什么?AI未来的发展方向是什么?但是,在我们展开想象之前,必须注意AI的“鸡和蛋”问题:硬件作为模型的基础,我们很难想象新模型部署在性能较差的硬件上,也就是说,新模型需要新的硬件。

由于制造新硬件的成本很高,所以需要有合理的理由才能拿到资金开始研究新硬件。但如果你没有在合理时间内运行这些新模型的硬件,也就无法证明这些新模型的价值。接着,由于没能展示新模型的实际性能,AI创新就会受到现有硬件解决方案的束缚。

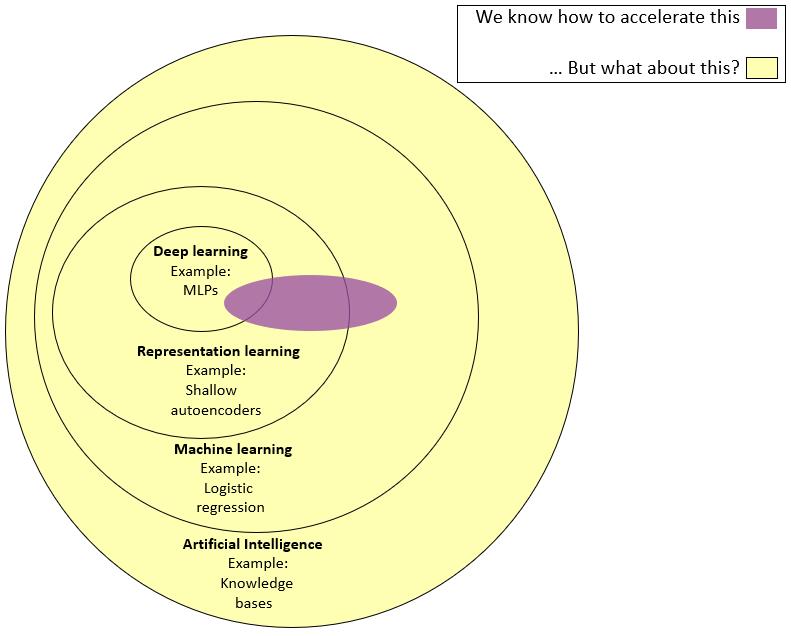

从AI到深度学习:我们在加速什么?

值得一提的是,虽然我们将当前硬件所做的称为“AI加速”,但其实是在夸大其词。事实上,它更接近于“深度学习加速”,或者是结合了基于张量的深度学习和机器学习算法的产物,可以在矩阵乘法引擎上运行良好。

有人可能会说,“好吧,我们几乎都听说过深度学习,它是当今最具价值的‘杀手级应用’”,但这正是关键所在———我们主要研究深度学习,因为算法库和硬件都是为深度学习量身定制的,因此深度学习是我们目前能够探索的领域,这是开发加速硬件时需要注意的。

我们通过协同设计算法和硬件,已经从构建通用处理器发展到搭建各种体系结构;然而,我们将数据路径长度优化为固定大小的变量,因为有固定大小的算法引擎和固定字大小的内存和连接,并且我们尽量使用矩阵乘法,因为它拥有简单且可预测的控制流。我们不希望过度优化硬件导致其性能大幅下降,这会妨碍探索新功能,从而阻碍算法进步。

虽然我不是神经科学家,但我知道大脑拥有许多复杂的结构,这些结构以不规则的方式进行通信,所以我们可能无法使用矩阵乘法、固定宽度数据路径和非线性函数来模拟它们。

因此,我们需要思考,这种硬件进化是否让应用硬件协同设计空间中收敛到局部最优?也许,如果脱离张量密集型模型就能实现“AI加速2.0”,迎来AI硬件的下一波浪潮。

那时,“AI加速2.0”不需要将矩阵相乘,但支持不规则的计算模式,并拥有灵活的表征和任意并行化的计算引擎。具有这些特性的加速器(或此类加速器的异构集成)将拥有更广泛的应用范围,也更接近真正的AI。

总而言之,我们需要思考:注意力机制是我们所需的全部吗?卷积神经网络(CNN)是最终的答案吗?不管答案是什么,卷积神经网络确实凝集了我们大部分的研究成果,但也许AI还有更多可以扩展到日用品的东西。

(本文经授权后发布,原文:

https://medium.com/@adi.fu7/ushering-in-the-next-wave-of-ai-acceleration-a7a14a1803d1)

往期回顾

分享

点收藏

点点赞

点在看以上是关于从 MLPerf 谈起:如何引领 AI 加速器的下一波浪潮的主要内容,如果未能解决你的问题,请参考以下文章

值得买科技发布2022年三季报 企业将如何引领消费行业的下一个周期