NVIDIA GPU显卡介绍

Posted 花花少年

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了NVIDIA GPU显卡介绍相关的知识,希望对你有一定的参考价值。

一、参考资料

NVCC学习笔记

NVIDIA GPU 架构演进

Nvidia GPU架构 - Cuda Core,SM,SP等等傻傻分不清?

请问英伟达GPU的tensor core和cuda core是什么区别?

二、相关概念

2.1 dGPU

dGPU(discrete GPU),独立显卡。

2.2 FLOPS(Floating-point operations per second)

每秒浮点运算次数(亦称每秒峰值速度)是每秒所运行的浮点运算次数;

一个MFLOPS(megaFLOPS)等于每秒一百万(10^6)次的浮点运算;

一个GFLOPS(gigaFLOPS)等于每秒十亿(10^9)次的浮点运算;

一个TFLOPS(teraFLOPS)等于每秒一兆/一万亿(10^12)次的浮点运算;

一个PFLOPS(petaFLOPS)等于每秒一千兆/一千万亿(10^15)次的浮点运算;

一个EFLOPS(exaFLOPS)等于每秒一百京/一百亿亿(10^18)次的浮点运算;

2.3 TOPS(Tera Operations Per Second)

1TOPS代表处理器每秒钟可进行一万亿次(10^12)操作。

2.4 SM流处理器

流式传输多元处理器。

2.5 SMP(SM Processing Block)

流处理块。比如GPU Pascal架构里,每个SM由两个SMP组成。

1 SM = 2个SMP = 64 CUDA Core + 1 RT Core + 8 Tensor Core

2.6 CUDA Core

CUDA Core(Shader processors),也称为Streaming Processor(SP),是 全能通吃型的浮点运算单元。CUDA Core名称正式出现的位置是在Fermi架构(2010年),在此之前称为processor core ,也称为streaming processors (SPs) 或者称为 thread processors。CUDA Core在显卡里是并行运行的,CUDA Core越多,算力越强。

CUDA Core包含了一个 integer arithmetic logic unit (ALU)整数运算单元和一个 floating point unit (FPU)浮点运算单元。CUDA Core能进行一种fused multiply-add (FMA)的操作,即一个加乘操作的融合。特点:在不掉精度的情况下,单指令完成乘加操作,并且这个是支持32-bit精度。

更通俗一点,比如公式:

Z

=

W

∗

X

+

b

Z = W * X + b

Z=W∗X+b

输出Z等于W乘以输入X加上bias,深度学习中,有大量这种运算。如果用常规的CPU,会怎么处理呢?先把寄存器里面的数据送入乘法器,然后把结果送回寄存器,然后再把寄存器的数据送入加法器。但是,在CUDA Core中,单指令完成该运算。

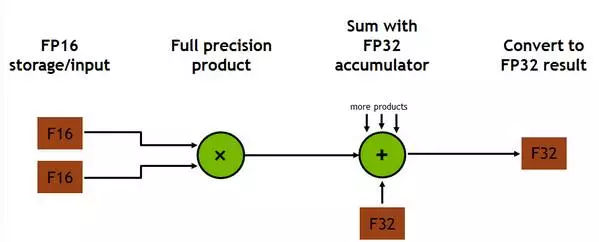

但是,对于一些场景,比如混合精度的矩阵操作,CUDA Core计算不是很高效,于是NVIDIA就开始专门针对tensor张量运算的硬件单元Tensor Core。

2.7 RT Core(光线追踪运算核心)

光线跟踪专用的运算单元。

2.8 Tensor Core(硬件核)

张量运算核心Tensor Core;

深度学习运算单元Tensor Core;

Tensor Core比流处理器更强大的专门针对 深度学习矩阵操作 有特别优化的一个运算核;

Tensor Core第一代是在volta架构上推出的,格外擅长加速 矩阵—矩阵乘法,这是训练神经网络和推理功能的核心算法,换句话说,这就是机器学习所必须的硬件基础。

[pascal与volta对比](Nvidia GPU.assets/pascal与volta对比.mp4)

2.9 DLA单元(Deep Learning Accelerator)

深度学习加速器。

Nvidia DLA is designed specifically for the deep learning use case and is used for offload the inference effort from GPU.

These engines improve energy efficiency and free up the GPU to run more complex networks and dynamic tasks implemented by the user.

2.10 LD/ST(load store unit)

用来操作内存的。

2.11 SFU(Special function unit)

用来做cuda的intrinsic function的。

2.12 TensorRT(软件库)

加快推断(inference)的速度。

Nvidia:CUDA GPU,面向嵌入式的Jetson;

Intel:Movidius VPU(NCS2);

Apple:A12处理器(及之后)上的NPU;

高通:骁龙处理器(上的AIE引擎,目前到了第5代);

华为:麒麟处理器(达芬奇架构);

2.13 NVIDIA的显卡架构出道顺序

- Tesla1.0 (2006年, 代表GeForce8800)

- Tesla2.0 (GT200)

- Fermi(算力可以支撑深度学习啦)

- Kepler(core增长)

- Maxwell(core继续增长)

- Pascal(算力提升)

- Volta(第一代tensor core)

- Turning(第二代 tensor core)

- Ampere(第三代tensor core)

2.14 AI程序如何调用显卡计算资源

用户代码 -> AI框架(PyTorch/Tensorflow/Caffe等)-> CUDA lib -> Driver -> 显卡。

三、GPU架构

计算能力并不是描述GPU设备计算能力强弱的绝对指标,准确的说,这是一个架构的版本号。一般来说越新的架构版本号更高,计算能力的第一个数值也就最高(例如3080计算能力8.6),而后面的6代表在该架构前提下的一些优化特性。

3.1 Fermi

Compute Capability: 2.0, 2.1。

每个 SM 包含:

- 2 个 Warp Scheduler/Dispatch Unit;

- 32 个 CUDA Core(分在两条 lane 上,每条分别是 16 个)

- 每个 CUDA Core 里面是 1 个单精浮点单元(FPU)和 1 个整数单元(ALU),可以直接做 FMA 的乘累加;

- 每个 cycle 可以跑 16 个双精的 FMA;

- 16 个 LD/ST Unit;

- 4 个 SFU;

3.2 Kepler架构

Compute Capability: 3.0, 3.2, 3.5, 3.7;

Tesla K40;

每个 SM包含:

- 4 个 Warp Scheduler,8 个 Dispatch Unit;

- CUDA Core 增加到 192 个(4 * 3 * 16,每条 lane 上还是 16 个);

- 单独分出来 64 个(4 * 16,每条 lane 上 16 个)双精运算单元。;

- SFU 和 LD/ST Unit 分别也都增加到 32 个;

3.3 Maxwell(麦克斯韦架构)

Compute Capability: 5.0, 5.2, 5.3;

GTX 9 SERIES;

Tesla M40;

每个SM包含:

- 4个 Warp Scheduler,8个 Dispatch Unit;

- 128个CUDA Core(4 * 32);

- 32个 SFU 和 LD/ST Unit(4 * 8);

每个 Process Block包含:

- 1个Warp Scheduler 和 2个 Dispatch Unit;

- 32个 CUDA Core;

- 8个 SFU 和 LD/ST Unit;

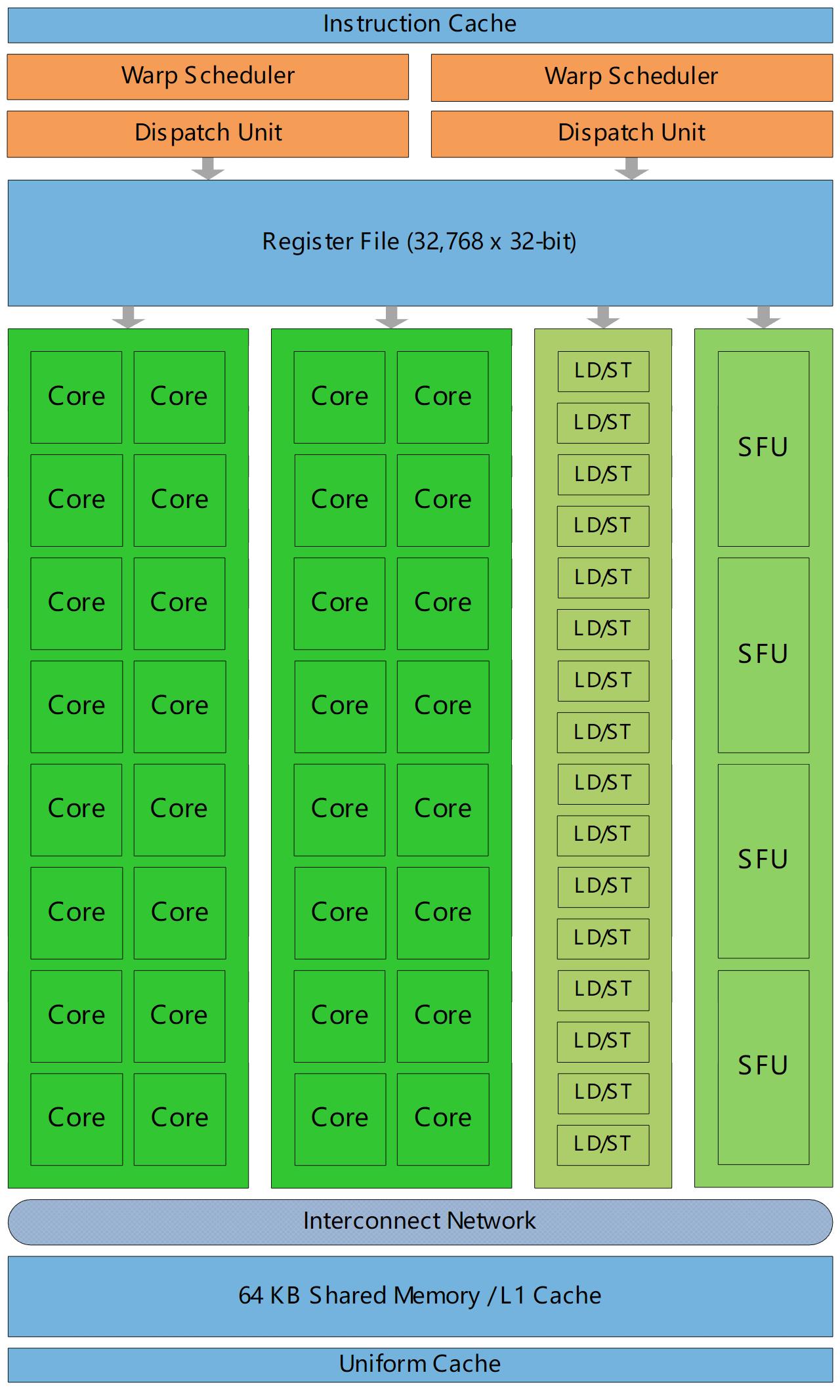

3.4 Pascal 架构

Compute Capability: 6.0, 6.1, 6.2;

GTX 10 SERIES;

Tesla P100;

Pascal架构是NVIDIA于 GTC 2016发布的GPU架构

CUDA Core在这一代终于有升级,硬件直接支持FP16的半精度计算,半精度性能是单精度的2倍,一个单精度单元用两个半精度计算。

每个SM包含:

- 2个 Warp Scheduler,4个Dispatch Unit;

- 64个 CUDA Core(2 * 32);

- 32个双精度浮点单元(2 * 16);

- 16个 SFU 和 LD/ST Unit(2 * 8);

每个 Process Block包含:

- 1个Warp Scheduler 和 2个 Dispatch Unit;

- 32个 CUDA Core;

- 多了16个 DP Unit;

- 8个SFU 和 LD/ST Unit;

3.5 Volta架构

参考资料:深度解析Volta架构,专为深度学习而生的Tensor Core

Compute Capability: 7.0, 7.2;

Tesla V100;

Volta架构是NVIDIA于 GTC 2013发布的GPU架构。

Volta架构专为计算和数据科学而打造,通过将 NVIDIA® CUDA® 和 Tensor 核心配合使用,可以在单个 GPU 中提供 AI 超级计算机的性能。

每个SM包含:

- 4 个 Warp Scheduler,4 个 Dispatch Unit;

- 64 个 FP32 Core(4 * 16);

- 64 个 INT32 Core(4 * 16);

- 32 个 FP64 Core(4 * 8);

- 8 个 Tensor Core (4 * 2);

- 32 个 LD/ST Unit(4 * 8);

- 16 个 SFU;

每个 Process Block 包含:

- 1 个 Warp Scheduler,1 个 Dispatch Unit;

- 16 个 FP32 Core;

- 16 个 INT32 Core;

- 8 个 FP64 Core;

- 2 个 Tensor Core;

- 8 个 LD/ST Unit;

- 4 个 SFU;

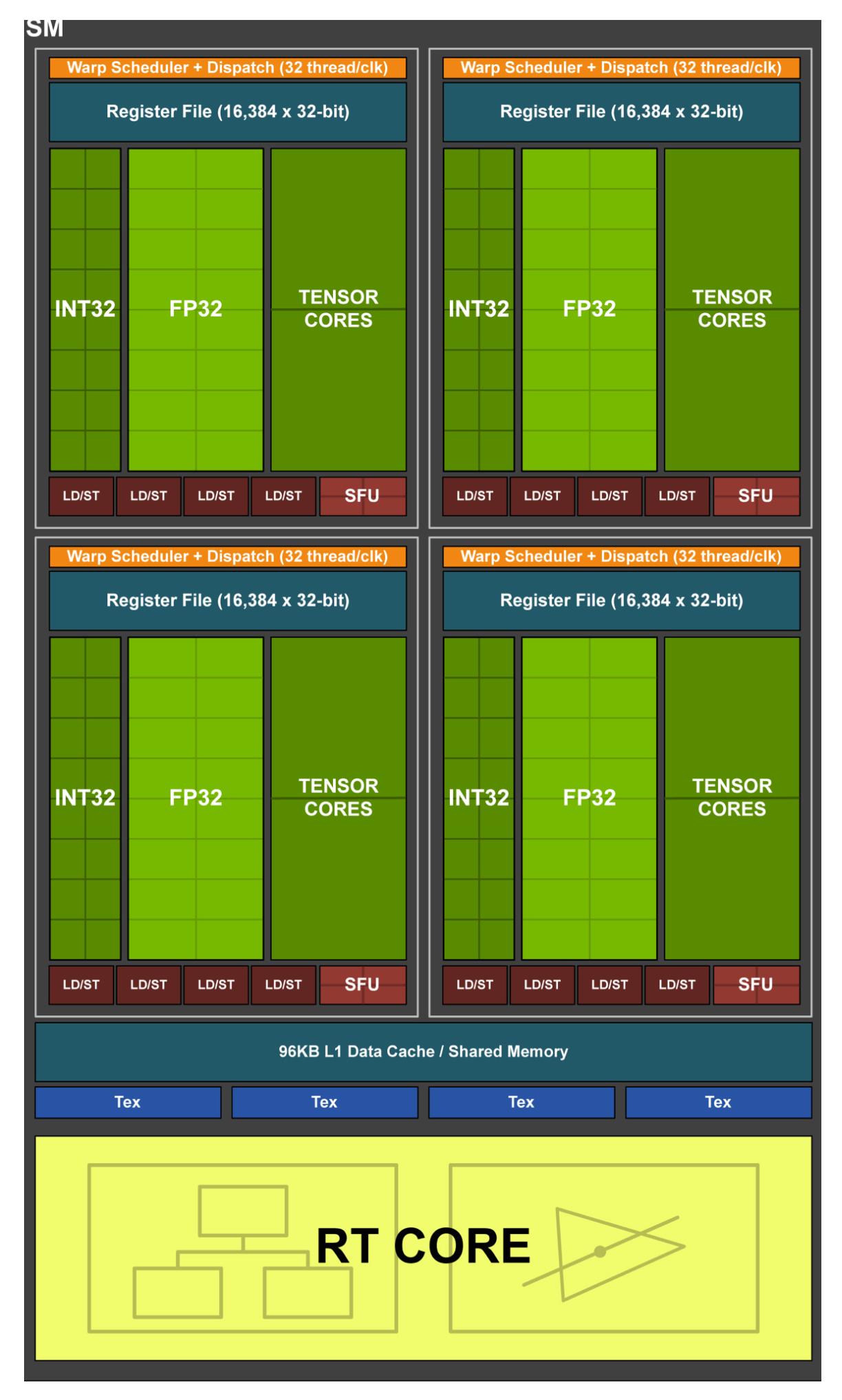

3.6 Turning(图灵架构)

Compute Capability: 7.5;

RTX 20 SERIES;

Quadro RTX 8000;

Quadro RTX 6000;

Quadro RTX 5000;

Quadro RTX Server;

Turning架构是NVIDIA于 在 SIGGRAPH 2018发布的GPU架构。

每个 SM 包含:

- 4 个 Warp Scheduler,4 个 Dispatch Unit;

- 64 个 FP32 Core(4 * 16);

- 64 个 INT32 Core(4 * 16);

- 8 个 Tensor Core(4 * 2);

- 16 个 LD/ST Unit(4 * 4);

- 16 个 SFU;

每个 Process Block 包含:

- 1 个 Warp Scheduler,1 个 Dispath Unit;

- 16 个 FP32 Core;

- 16 个 INT32 Core;

- 2 个 Tensor Core;

- 4 个 LD/ST Unit;

- 4 个 SFU;

Turning图灵架构的光线跟踪特性,实际上是旧有光线跟踪技术与近年兴起的人工智能(AI)、深度学习结合的产物,先是利用光线跟踪专用的运算单元RT core生成图像的关键要素,剩余的非关键要素则是交由深度学习运算单元Tensor Core来补全

在Turning图灵架构中,每个SM单元包含了64个CUDA核心、1个RT核心和8个张量核心,1 SM = 64 CUDA Core + 1 RT Core + 8 Tensor Core

RTX 2080、RTX 2080ti是图灵架构,具有实时光线跟踪(Ray tracing)功能

RTX 2070 SUPER的SM单元数量比RTX 2070多4个,达到40个。由于在图灵架构中,每个SM单元包含了64个CUDA核心、1个RT核心和8个张量核心,所以RTX 2070 SUPER的CUDA核心数增加到2560个,而RTX 2070的CUDA核心数为2304个,同时前者的RT核心和张量核心分别增加了4个和32个

3.7 Ampere(安培架构)

Compute Capability: 8.0;

RTX 30 SERIES;

Ampere架构是NVIDIA于 GTC 2020发布的GPU架构,NVIDIA Ampere 由540亿晶体管组成,是7nm芯片。

每个 SM 包含:

- 4 个 Warp Scheduler,4 个 Dispatch Unit;

- 64 个 FP32 Core(4 * 16);

- 64 个 INT32 Core(4 * 16);

- 32 个 FP64 Core(4 * 8);

- 4 个 Tensor Core (4 * 1);

- 32 个 LD/ST Unit(4 * 8);

- 16 个 SFU;

每个 Process Block 包含:

- 1 个 Warp Scheduler,1 个 Dispatch Unit;

- 16 个 FP32 Core;

- 16 个 INT32 Core;

- 8 个 FP64 Core;

- 1 个 Tensor Core;

- 8 个 LD/ST Unit;

- 4 个 SFU;

四、算力

Matching CUDA arch and CUDA gencode for various NVIDIA architectures

CUDA:NVCC编译过程和兼容性详解

4.1 算力表

NVIDIA算力表

【原】CUDA的deviceQuery命令

4.2 不同算力支持的量化等级

GPU有个重要参数-算力,算力值对应GPU的“代”值,如算力5.0,对应的“代”为sm_50,也对应Maxwell架构。

为了实现GPU架构的演变,NVIDIA GPU以不同代次发布。新一代产品在功能和/或芯片架构方面会引入重大改进。同一代产品中的GPU模型显示出较小的配置差异,对功能和/或性能产生中等的影响。

除了sm_20,sm_30,sm_50这些大的代号,还有sm_21,sm_35,sm_53这些小代,这些小代不会做大的改变,会有一些小的调整,如调整寄存器和处理器集群的数量。这只影响执行性能,不会改变功能。程序更精准的对应GPU代号可能达到最佳性能。

在实际结论中,compute_30以上的程序,算力高的GPU可以运行编译成低代的程序,反之则不行,如算力5.0的GPU可以运行编译成compute_30,sm_30的程序。虚拟框架由compute_开头,真实框架由sm_开头。

'-gencode', 'arch=compute_50,code=sm_50'

表示算力5.0以上的GPU都可以运行编译的程序,但算力3.0的GPU就不能运行了。

-gencode,-genarate-code的缩写,保证用户GPU可以动态选择最合适的GPU架构(最适合GPU的大代和小代)

[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-8vsCsxn6-1648990324595)(Nvidia GPU.assets/代与算力的关系.png)]

五、GPU类型

- 用于训练的DGX;

- 用于超大规模云的HGX;

- 用于边缘的EGX;

- 用于终端的AGX;

六、特殊产品

6.1 Xavier SOC

参考资料

NVIDIA声称Xavier是迄今为止发明的最复杂的SOC

NVIDIA Jetson Xavier性能首测:AI性能碾压苹果A12,自研CPU架构看齐骁龙845

- 用于无人机和机器人的Jetson Xavier;

- 用于诸如L3-4级驾驶辅助的Drive Xavier;

- 旗舰Drive Pegasus,具有双Xavier SOC和2瓦GPU,以支持完全自动驾驶的L5级别;

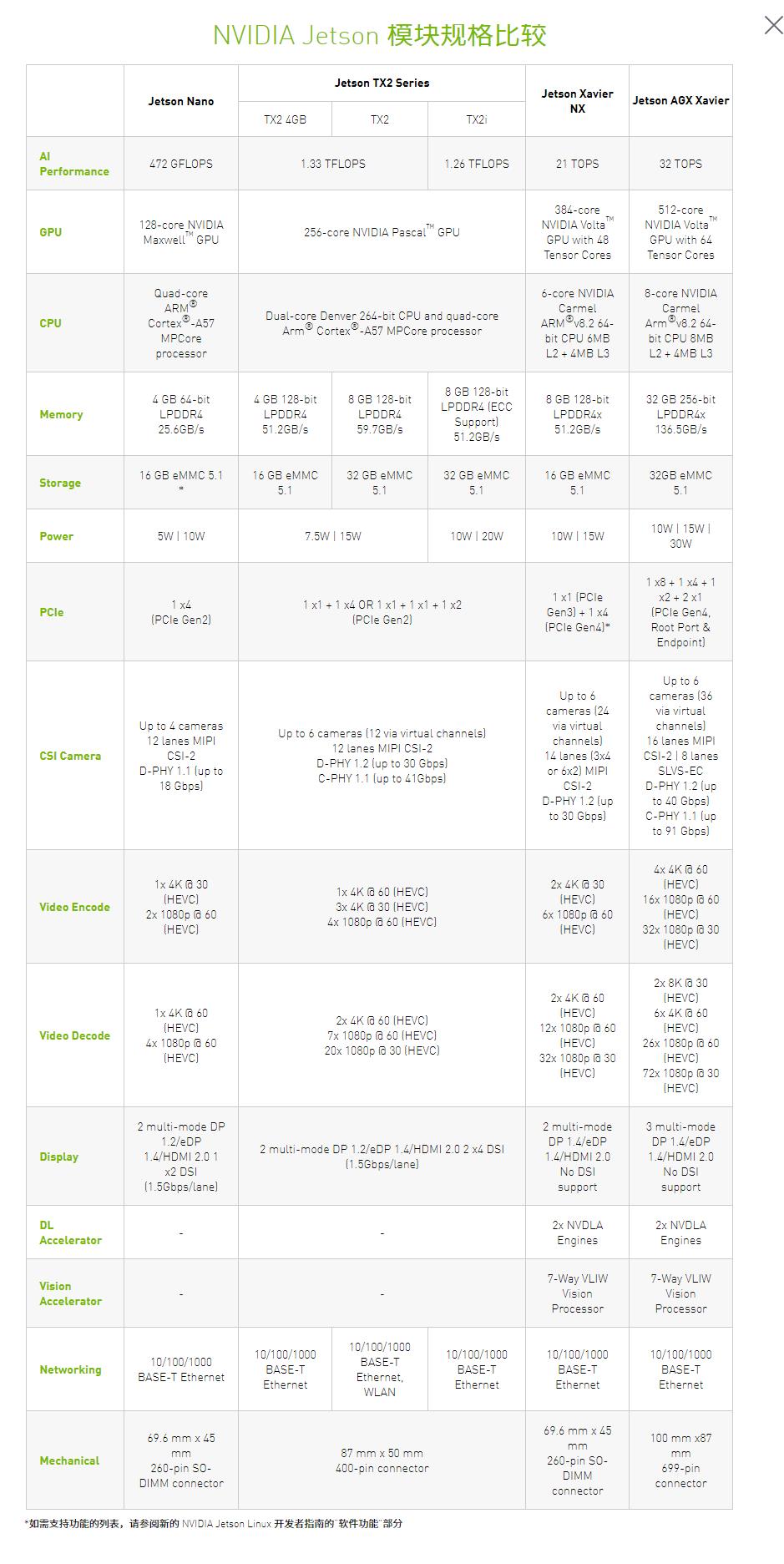

6.2 Jetson平台

参考资料

CUDA 初学者统一内存

CUDA中的Unified Memory

Jetson是NVIDIA嵌入式产品,不存在独立的显存和内存,即CPU和GPU共用存储器。

6.2.1 Jetson TK1

2018年已经下架

属于探索性产品

6.2.2 Jetson Nano

参考资料

AI | Nvidia Jetson Nano介绍与使用指南

售价899RMB

最新推出,主打便宜

6.2.3 Jetson TX2

教育售价2899RMB

迭代升级

6.2.4 Jetson Xavier NX

教育售价2899RMB

迭代升级

6.2.5 Jetson AGX Xavier

教育售价7099RMB

迭代升级

专为自动驾驶技术和汽车产品使用的超算解决方法,是所谓的车规级SoC芯片。

| Jetson Nano | Jetson TX2 | Jetson Xavier NX | Jetson AGX Xavier | |

|---|---|---|---|---|

| 架构 | Maxwell™ | Pascal™ | Volta™ | Volta™ |

| NVIDIA CUDA 核心 | 128 | 256 | 384 | 512 |

| Tensor 核心 | 48 | 64 |

以上是关于NVIDIA GPU显卡介绍的主要内容,如果未能解决你的问题,请参考以下文章

再现猪队友?技嘉曝光RTX 3080 Ti与RTX 3060显卡

Nvidia GPU信息nvidia-smi(Persistence-M持久性内存Volatile Uncorr. ECC显存错误校正GPU-Util显卡利用率Compute M.显卡计算模式)