试述指令周期 CPU周期和时钟周期之间的关系?

Posted

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了试述指令周期 CPU周期和时钟周期之间的关系?相关的知识,希望对你有一定的参考价值。

相互关系如下:指令周期是取出并执行一条指令的时间,指令周期常常有若干个CPU周期(也叫机器周期),CPU周期一般由12个时钟周期组成(时钟周期通常由晶振决定)。

也就是说指令周期的通常大于cpu周期,指令周期的长短与执行的指令有关,有的指令需要花费更多的CPU周期。

1、时钟周期

时钟周期也称为振荡周期,定义为时钟脉冲的倒数(可以这样来理解,时钟周期就是单片机外接晶振的倒数,例如12M的晶振,它的时间周期就是1/12 us),是计算机中最基本的、最小的时间单位。

在一个时钟周期内,CPU仅完成一个最基本的动作。对于某种单片机,若采用了1MHZ的时钟频率,则时钟周期为1us;若采用4MHZ的时钟频率,则时钟周期为250us。由于时钟脉冲是计算机的基本工作脉冲,它控制着计算机的工作节奏(使计算机的每一步都统一到它的步调上来)

在8051单片机中把一个时钟周期定义为一个节拍(用P表示),二个节拍定义为一个状态周期(用S表示)。

2、机器周期

在计算机中,为了便于管理,常把一条指令的执行过程划分为若干个阶段,每一阶段完成一项工作。例如,取指令、存储器读、存储器写等,这每一项工作称为一个基本操作。完成一个基本操作所需要的时间称为机器周期。

8051系列单片机的一个机器周期同6个S周期(状态周期)组成。前面已说过一个时钟周期定义为一个节拍(用P表示),二个节拍定义为一个状态周期(用S表示),8051单片机的机器周期由6个状态周期组成,也就是说一个机器周期=6个状态周期=12个时钟周期。

3、指令周期

指令周期是执行一条指令所需要的时间,一般由若干个机器周期组成。指令不同,所需的机器周期数也不同。对于一些简单的的单字节指令,在取指令周期中,指令取出到指令寄存器后,立即译码执行,不再需要其它的机器周期。

对于一些比较复杂的指令,例如转移指令、乘法指令,则需要两个或者两个以上的机器周期。

通常含一个机器周期的指令称为单周期指令,包含两个机器周期的指令称为双周期指令。

CC2530的每个指令周期是一个时钟,而标准的8051 每个指令周期是12 个时钟。 参考技术A 时钟周期是最基本的,就是该CPU所用震荡器的周期,振荡器输出给CPU做时钟信号。CPU周期就是时钟周期,指令周期是指该CPU执行一条机器指令所用的若干个振荡器周期(即时钟周期)的时间本回答被提问者采纳 参考技术B “若采用4MHZ的时钟频率,则时钟周期为250us。“

是不是应为0.25US?

CPU的流水线指令设计

为什么小小一个CPU,有那么多周期(Cycle)?

程序的性能,是由三个因素相乘来衡量的,“指令数×CPI×时钟周期”。

和周期相关的只有一个时钟周期,即CPU主频的倒数。

一个CPU的时钟周期可以认为是可以完成一条最简单的计算机指令的时间。

那为何构造CPU时,有那么多周期?

单指令周期处理器

一条CPU指令的执行,由FDE三步组成。这个执行过程,至少需花费一个时钟周期。因为在取指令的时候,我们需要通过时钟周期的信号,来决定计数器的自增。

很自然,我们希望能确保让这样一整条指令的执行,在一个时钟周期内完成。

这样,一个时钟周期可执行一条指令,CPI=1,看着就比执行一条指令要多个时钟周期性能好。

这就是单指令周期处理器(Single Cycle Processor):一个时钟周期内,处理器正好能处理一条指令。

但时钟周期固定,指令的电路复杂程度不同,所以实际一条指令执行时间不同。

随门电路层数增加,由于门延迟,位数多、计算复杂指令需执行更久。

不同指令执行时间不同,但要让所有指令都在一个时钟周期内完成,只好把时钟周期和执行时间最长的那个指令一样。不然就会导致快速执行完成的指令,需等待满一个时钟周期,才能执行下一条指令。

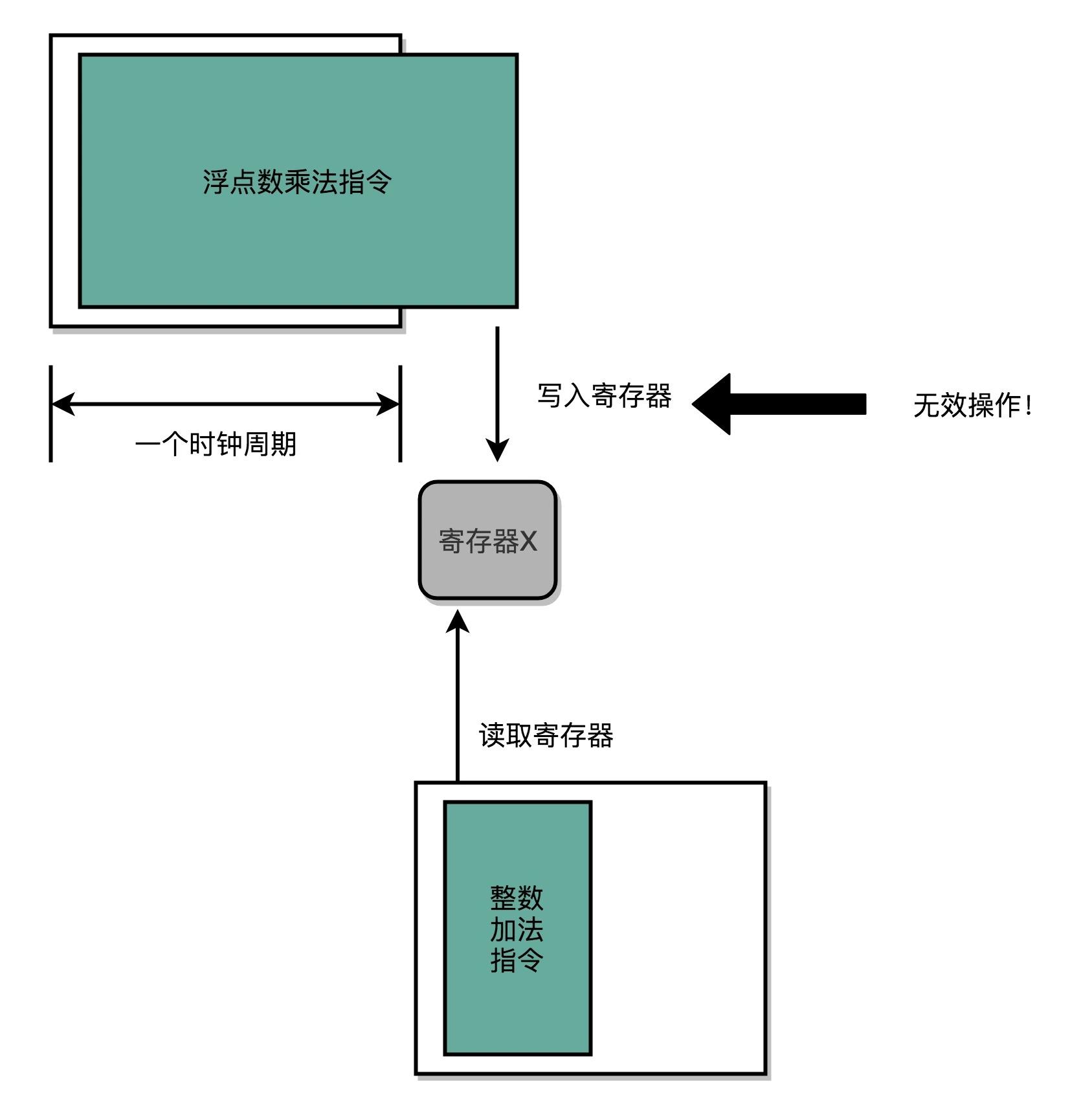

虽然CPI能够保持在1,但时钟频率却没法太高。太高,有些复杂指令没法在一个时钟周期内完成。在下个时钟周期到来,开始执行下条指令时,前一条指令执行结果可能还没写入寄存器。下一条指令读取的数据就不准确了。

- 前一条指令的写入,在后一条指令的读取之前

一个CPU时钟周期,可认为是完成一条简单指令的时间。

为什么单指令周期处理器,反而变成执行一条最复杂的指令的时间?

无论是Intel CPU or ARM CPU,都不是单指令周期处理器,而是采用一种叫作指令流水线(Instruction Pipeline)的技术。

现代处理器的流水线设计

指令执行过程会拆分成“取指令、译码、执行”三步。

更细分,执行的过程,还包含从寄存器或内存读数据,通过ALU运算,把结果写回寄存器或内存。

CPU的指令执行过程,其实也是由各电路模块组成:

-

取指令时,需要译码器,把数据从内存取出来,写入寄存器

-

指令译码时,需要另外一个译码器,把指令解析成对应控制信号、内存地址和数据

-

指令执行时,需要一个完成计算工作的ALU。这些都是一个一个独立的组合逻辑电路,我们可以把它们看作一个团队里面的产品经理、后端工程师和客户端工程师,共同协作来完成任务。

-

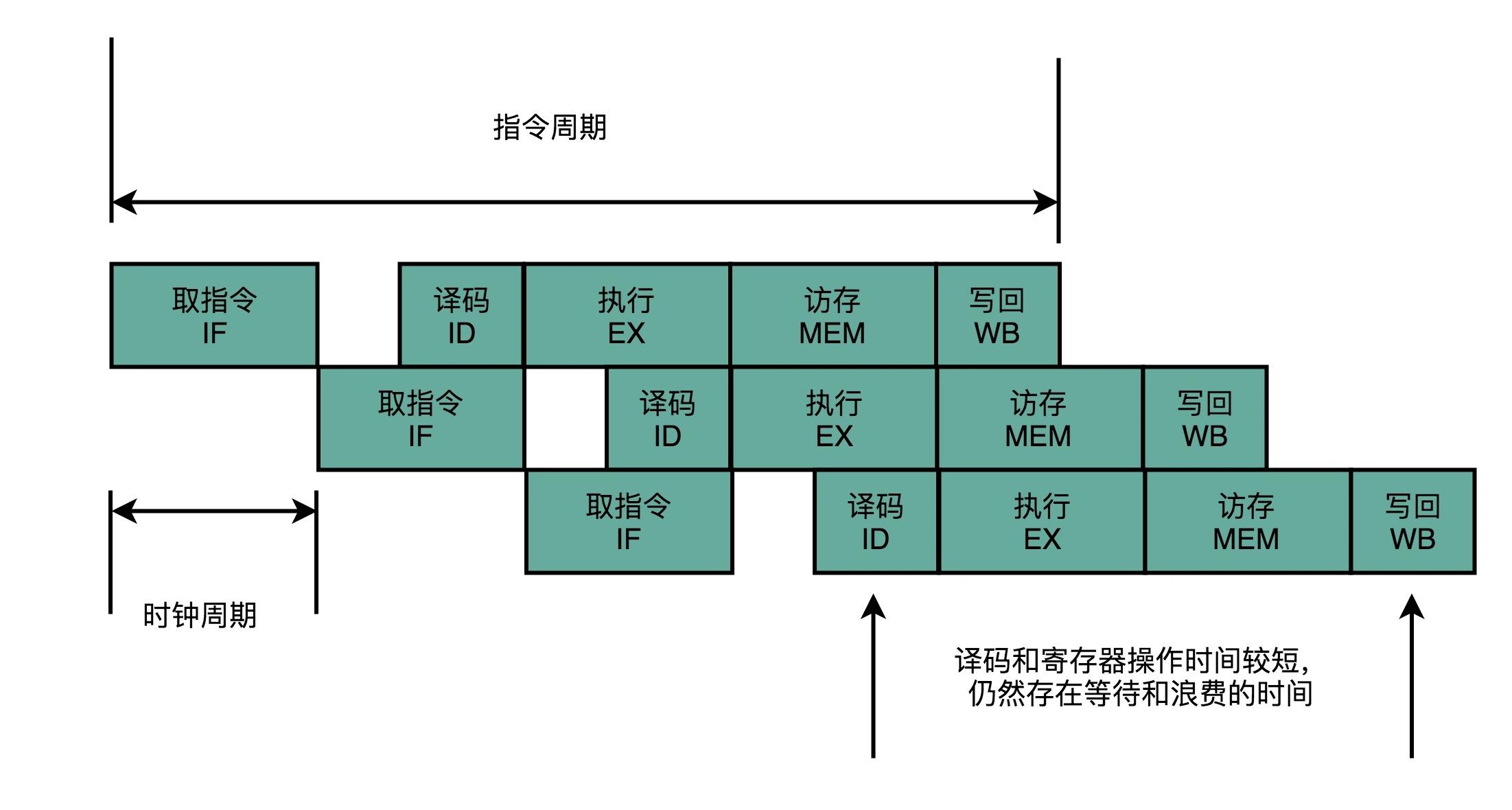

流水线执行示意图

这就不用把时钟周期设置成整条指令执行的时间,而是拆分成完成这样的一个一个小步骤需要的时间。同时,每一个阶段的电路在完成对应的任务之后,也不需要等待整个指令执行完成,而是可以直接执行下一条指令的对应阶段。

这样的协作模式,就是指令流水线。这里每个独立步骤,称为流水线阶段或流水线级(Pipeline Stage)。

把一个指令拆分成“取指令-指令译码-执行指令”三部分,那这就是一个三级流水线。

进一步把“执行指令”拆分成“ALU计算(指令执行)-内存访问-数据写回”,就变成一个五级流水线。

五级流水线:同一时钟周期里,同时运行五条指令的不同阶段。这时,虽然执行一条指令的时钟周期变成5,但可提高CPU的主频。

无需确保最复杂那条指令在时钟周期里执行完成,只要保障一个最复杂的流水线级操作,在一个时钟周期内完成即可。

若某一操作步骤时间太长,可考虑把该步骤拆分成更多步骤,让所有步骤需执行时间尽量差不多长。这就可解决在单指令周期处理器中遇到的,性能瓶颈来自最复杂的指令的问题。

像ARM或IntelCPU,流水线级数都已到14级。

虽然不能通过流水线,减少单条指令执行的“延时”指标,但通过同时在执行多条指令的不同阶段,提升了CPU的“吞吐率”。

外部看来,我们的CPU好像“一心多用”,同一时间,同时执行5条不同指令的不同阶段。

CPU内部,就像生产线,不同分工的组件不断处理上游传递下来的内容,而无需等待单件商品生产完成后,再启动下一件商品的生产。

超长流水线的性能瓶颈

你说流水线能增加 CPU 吞吐率,流水线级数就越深越好咯?

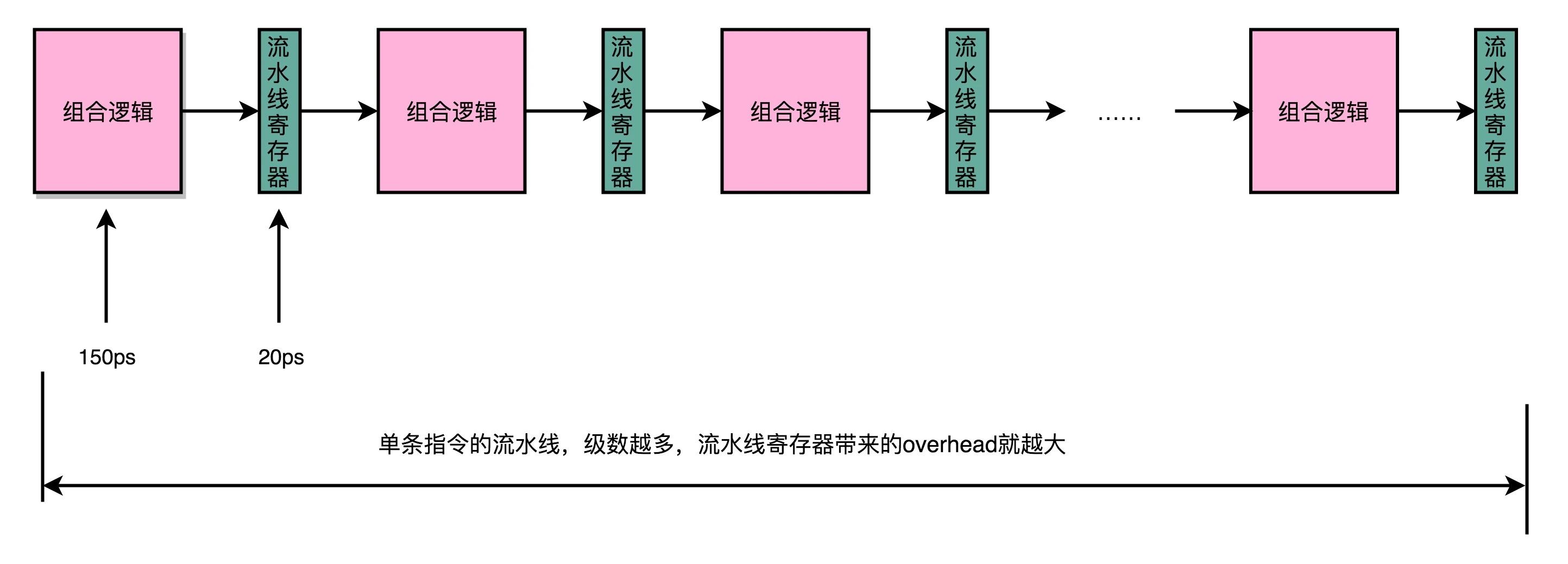

增加流水线深度,是有性能成本的。

同步时钟周期的,不再是指令级别,而是流水线阶段级别。

每一级流水线对应的输出,都要放到流水线寄存器(Pipeline Register),然后在下一个时钟周期,交给下一个流水线级去处理。

所以,每增加一级流水线,就要多一级写入到流水线寄存器的操作。

虽然流水线寄存器非常快,比如只有20皮秒(ps,

1

0

−

12

10^-12

10−12秒)。

但不断加深流水线,这些操作占整个指令的执行时间的比例就会不断增加。最后,性能瓶颈就会出现在这些overhead。

若指令执行有3ns=3000ps:

- 20级流水线,则流水线寄存器写入就要400ps,占超过10%

- 50级流水线,就要多花费1ns在流水线寄存器上,占到25%

这意味着,单纯增加流水线级数,不仅不能提升性能,反而会有更多overhead开销。所以,设计合理的流水线级数也是现代CPU中非常重要的一点。

总结

为不浪费CPU性能,通过把指令执行过程,切分成一个个流水线级,提升CPU吞吐率。而CPU设计,又是由一个个独立的组合逻辑电路串接起来形成,适合这样采用流水线“专业分工”的工作方式。

因为每一级overhead,一味地增加流水线深度,并不能无限地提高性能。同样地,因为指令的执行不再是顺序地一条条执行,而是在上一条执行到一半的时候,下一条就已经启动了,所以也给我们的程序带来了很多挑战。这些挑战和对应的解决方案,就要请你坚持关注后面的几讲,我们一起来揭开答案了。

参考

- 《深入理解计算机系统》的4.4章节

- 《计算机组成与设计 硬件/软件接口》的4.5章节

以上是关于试述指令周期 CPU周期和时钟周期之间的关系?的主要内容,如果未能解决你的问题,请参考以下文章