指令周期,机器周期,时钟周期与存储周期的关系

Posted

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了指令周期,机器周期,时钟周期与存储周期的关系相关的知识,希望对你有一定的参考价值。

指令周期,机器周期,时钟周期与存储周期的关系如上 不是很理解存储周期 看的书里说是存储两次独立的存储操作所需的最小间隔时间,这里

1.这个周期大小是固定的吗,一次存储的数据量是固定的吗

2.它和各类机器周期的关系是什么,谁包括谁

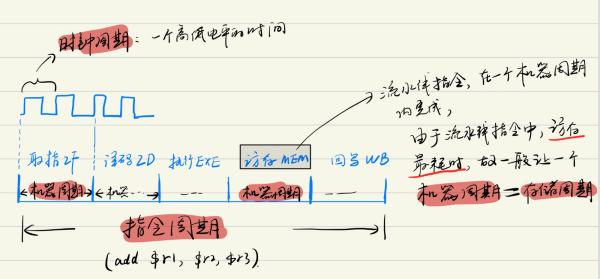

首先周期的单位是时间 s ms ns,倒数是频率。针对上图,说明几点:

1:本图以 MIPS 汇编为例。

2:一个机器周期具体是几个时钟周期,要看CPU流水线的设计,但至少是一个,时钟周期是最小的单位,时钟周期的倒数为 CPU 的频率,比如 3GHz,意思就是 3*10^9 个时钟周期 / s。

3:一条指令一般=一条汇编,但在CPU维度上,指令仍然不是最小的执行单位(x86中还有微指令),如上图,一条加法指令需要5个流水线指令:取指,译码,执行ALU,访存,回写寄存器。虽然不一定每个环节都用到,但为了实现流水线作业,所以都得执行。

4:同样为了实现流水线方便,每条流水线指令(取指、译码...) 会在一个机器周期内完成。且在单周期流水线的设计中机器周期长度都都相等,一般会让机器周期=存储周期 (时间长度上相等,概念不一样),原因是流水线指令中,访存指令(读内存或者写内存)最耗时。

5:存储周期的简单解释,两次内存的读或者写之间的最短时间间隔,之所以这样定义,是因为内存(一般为DRAM) 的读操作,属于破坏性读出,读完每个存储单元,数据会暂时丢失,需要花时间刷新存储单元来恢复数据。所以可粗略的认为存储周期=读取时间+恢复时间。之所以粗略,是因为,读取数据的时间,还和总线传输时间有关。。。所以用两次访存的时间间隔定义,最为简单和精确。

参考技术A周期:取决于"晶振频率",固定。但是因为工艺的关系,每个单元之间会有一定范围内的异同,"超频"就是这个道理,说到底还是"工艺";数据量:一次存取的最大二进制数据量肯定固定。因为引脚数目肯定是固定的。

参考百度百科"机器周期":指令周期(Instruction Cycle):取出并执行一条指令的时间。总线周期(BUS Cycle):也就是一个访存储器或I/O端口操作所用的时间。时钟周期(Clock Cycle):处理操作的最基本单位,晶振频率的倒数。指令周期、总线周期和时钟周期之间的关系:一个指令周期由若干个总线周期组成,而一个总线周期时间又包含有若干个时钟周期。一个总线周期包含一个(只有取址周期)或多个机器周期。

时钟周期,机器周期,指令周期的区别

时钟周期

时钟周期也称为振荡周期,定义为时钟脉冲的倒数(时钟周期就是单片机外接晶振的倒数,例如12M的晶振,它的时钟周期就是1/12us),是计算机中的最基本的、最小的时间单位。

在一个时钟周期内,CPU仅完成一个最基本的动作。时钟脉冲是计算机的基本工作脉冲,控制着计算机的工作节奏。时钟频率越高,工作速度就越快。

8051单片机把一个时钟周期定义为一个节拍(用P表示),二个节拍定义为一个状态周期(用S表示)。

机器周期

计算机中,常把一条指令的执行过程划分为若干个阶段,每一个阶段完成一项工作。每一项工作称为一个基本操作,完成一个基本操作所需要的时间称为机器周期。8051系列单片机的一个机器周期由6个S周期(状态周期)组成。

一个S周期=2个节拍(P),所以8051单片机的一个机器周期=6个状态周期=12个时钟周期。

例如外接24M晶振的单片机,他的一个机器周期=12/24M 秒;

指令周期

执行一条指令所需要的时间,一般由若干个机器周期组成。指令不同,所需的机器周期也不同。

CPU 周期信号、节拍周期信号、节拍脉冲信号三者之间的关系是什么?

一小块石英晶体加电后产生压电反应,在固定频率振动,产生出电压按照固定周期变化的脉冲信号。这个高频率的信号通向分频器(frequency divider),转化为比较低频的信号。

( http://www.electronics-tutorials.ws/counter/count_1.html )

以上图为例,分频器分出来的信号有四个频率。题目中所说 CPU周期信号、节拍周期信号、节拍脉冲信号本质上都是时钟脉冲的不同分频,主要区别在于用途上。

通常来说,CPU 周期信号最“慢”,它决定 CPU 所处的状态。CPU 执行一条指令的周期叫做指令周期(instruction

cycle),指令周期可以划分为 fetch、decode、和 execute 三个部分,所以也叫 fetch-decode-execute

cycle。假设上图与 QD 频率相同的信号有三个,QD1、QD2、QD3,它们分别依次处于高电位,那么就可以用它们来控制 CPU 处于

fetch、decode、还是 execute 状态,这就是 CPU 周期信号。

节拍周期信号是控制信号,调整电路的功能。比如,现在 CPU 处于 fetch 状态,仍旧以上图为例,假设 QC 这个比 QD

“快”的信号有 QC1、QC2、QC3……QCi

个,分别对应电路的不同功能(比如,应该将从内存中取来的数字作为指令解释,还是送给寄存器存起来),谁处于高电位,CPU

就能执行谁决定的功能。

节拍脉冲信号则是触发信号,决定电路的实际工作起点。以上图的 QB 为例,假设 QD1 决定 CPU 处于 fetch 阶段,QC1 决定 CPU 的功能是去内存取一个数字,那么 QB 的上升沿会触发整个电路切实地执行这个功能。

可以这样类比:

某诊所周一二三门诊,周四五看复诊病人,周六日不办公

——对应三个 CPU 周期

诊所星期一二三 8:00 开始门诊,12:00 午休,13:00 继续门诊,17:00 关门

——对应节拍周期

某个病人星期二 9:00 去看了病

——对应脉冲信号

(注意上面的说法极度简化,实际的实现要复杂很多,比如振动源不一定是石英,每个 CPU 周期未必等长,CPU 也并不是在某一时刻只能处于单独一种周期状态里(详见 pipelining),乃至周期层级也未必就是三层等等。)

以上是关于指令周期,机器周期,时钟周期与存储周期的关系的主要内容,如果未能解决你的问题,请参考以下文章