关于ISE14.7 时钟IP核使用 输出时钟恒为0

Posted

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了关于ISE14.7 时钟IP核使用 输出时钟恒为0相关的知识,希望对你有一定的参考价值。

FPGA:Kintex7, 输入为差分时钟 200M

ip 核实例

myclc_test instance_name

(// Clock in ports

.CLK_IN1_P(clk_in_p), // IN

.CLK_IN1_N(clk_in_n), // IN

// Clock out ports

.CLK_OUT1(CLK_OUT1), // OUT

// Status and control signals

.RESET(rst),// IN

.LOCKED(rst_n)); // OUT

UCF约束

时序约束

NET "clk_in_p" TNM_NET = "clk_in_p";

TIMESPEC "TS_clk_in_p" = PERIOD : "clk_in_p" : 5.000 ns HIGH 50.0%;

管脚约束

NET "clk_in_p" LOC="AA3" |iosTANDARD=DIFF_SSTL15;

NET "clk_in_n" LOC="AA2" |IOSTANDARD=DIFF_SSTL15;

结果 CLK_OUT1恒为零

请问原因何在?

10ISE14.7和modelsim10.5关联编译库

今天准备在ISE14.7中调用PLL的IP核,搞一下时钟的分频和倍频。可在我做好pll的IP核后,我直接用ise生成了一个仿真文件,只需要修改下例化模块名和加一个时钟就行勒。

问题:但怎么在ISE14.7中调用Modelsim勒?

百度找了很多资料发现,要想调用:首先得先对ISE编译库进行编译。然后就是关联ISE 和modelsim。网上的很多教程都是老版本的,没有找到10.5版本,同时在很多细节上也和实际操作不一样,怕大家入坑折磨自己一段时间。所以我就自己原创一篇教程,能够帮大家解决问题,同时记录下我的学习过程哈。我是最新的10.7,所以我又安装勒10.5版本的modelsim。至于怎么破解modelsim,可以看看我的另一篇博客,有详细的介绍及问题汇总解决哈。还有在操作中发现存在很多细节不一样,我成功入了很多坑,折腾了好几遍,看不同的教程尝试解决办法,成功真不容易哈。

下面上详细的关联教程:

第一步在开始菜单中,找到Xilinx design tools的任一文件,选择打开文件位置后如下图:

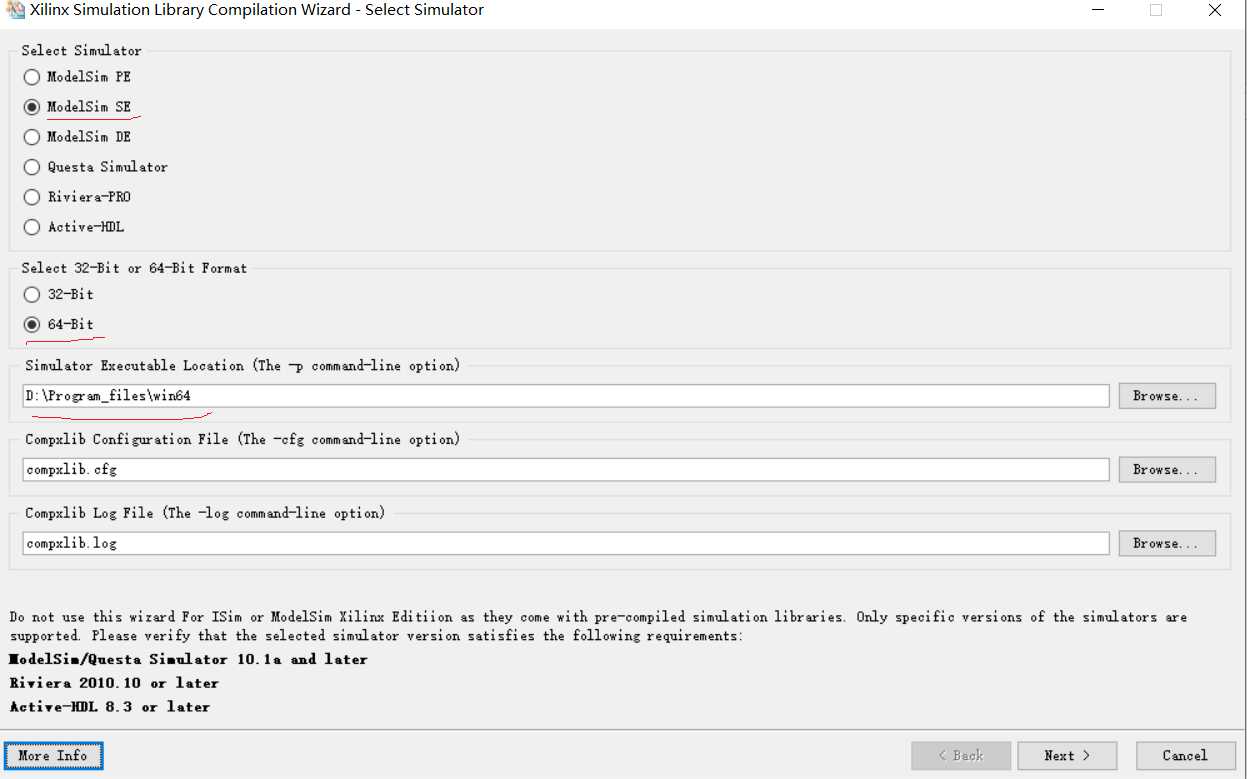

第二步,就到了设置modelsim的安装包位置和32位或64位选择,大家根据自己的软件位置和电脑来选,我选中的如红色标注,在next。如下图所示:

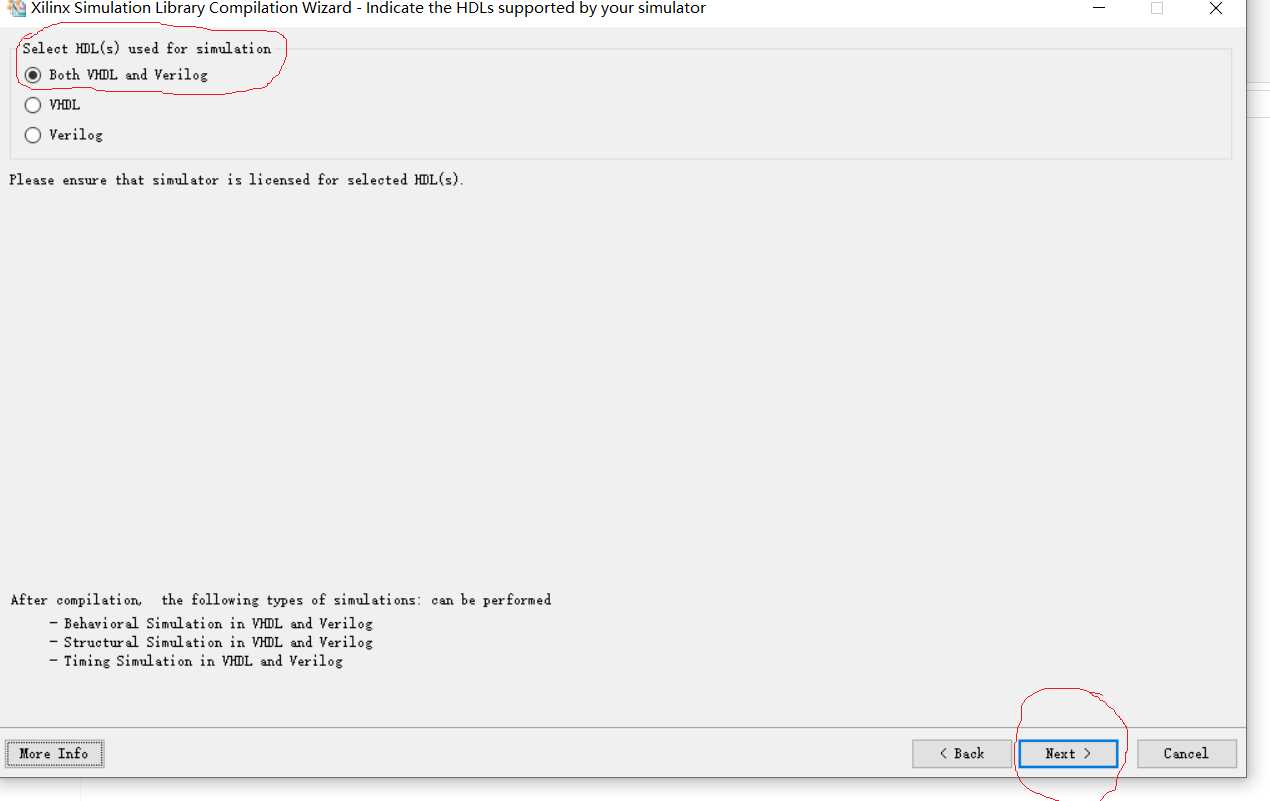

第三步,选择仿真语言,两种语言大家都选哈,就下一步

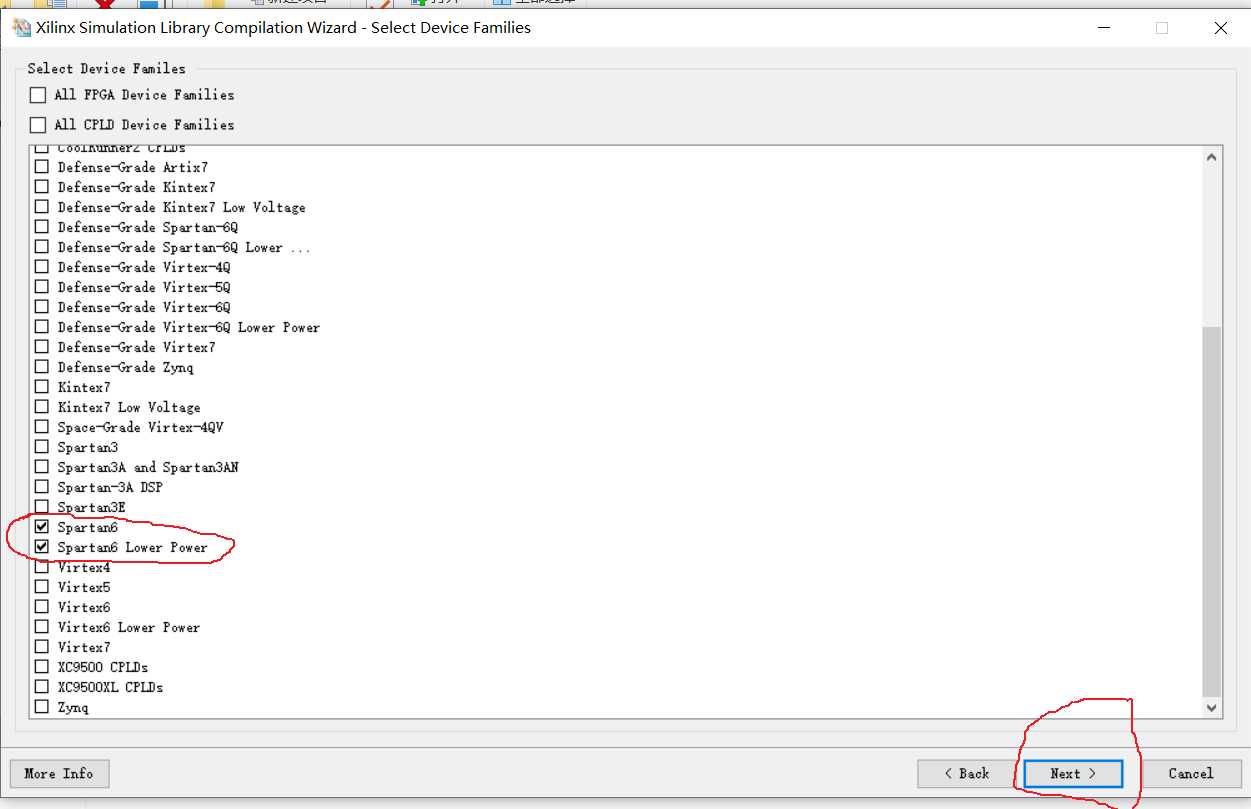

第四步,如下图所示:选择芯片的型号,这个看大家的需要和开发板芯片型号,我的型号是Spartan6,其他都用不到呀:

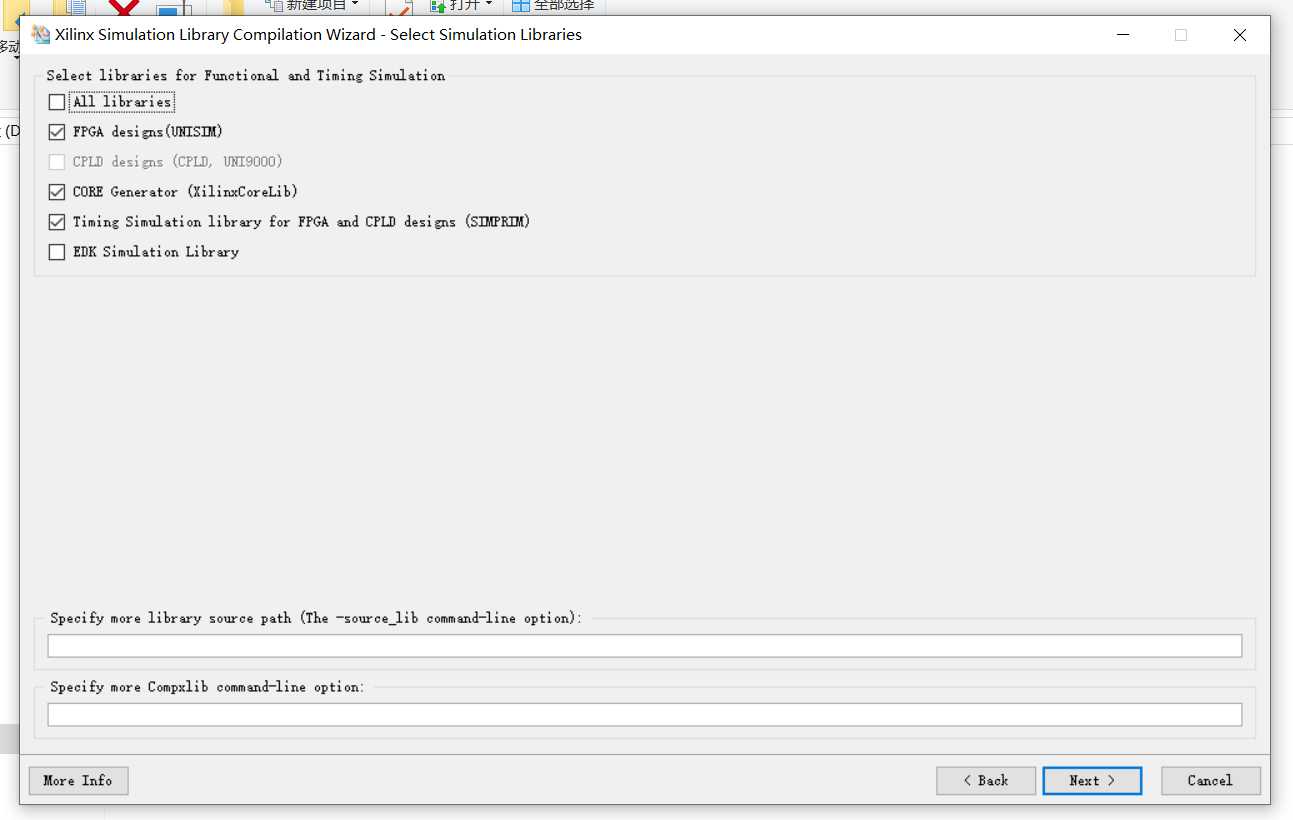

第五步,选择编译库和时序仿真,去掉了EDK,如下图

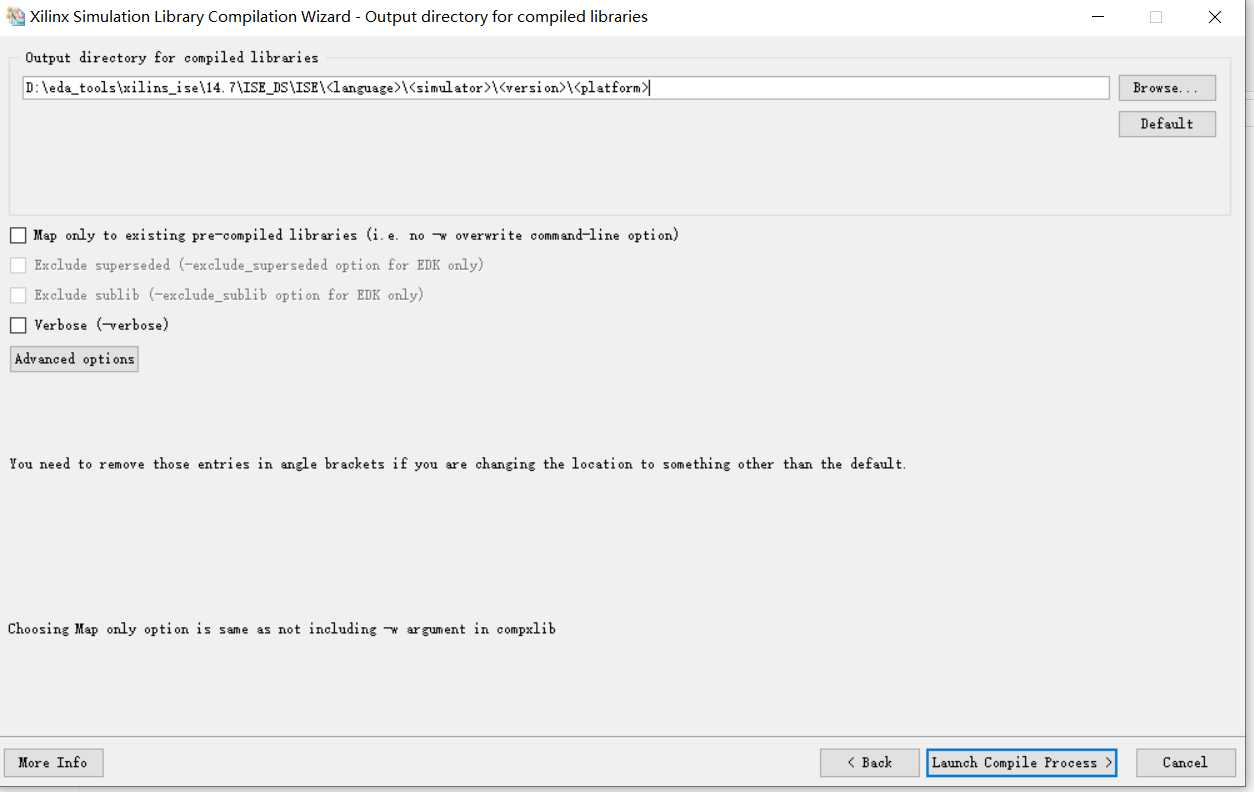

第六步,选择编译库路径,默认就行,如下图

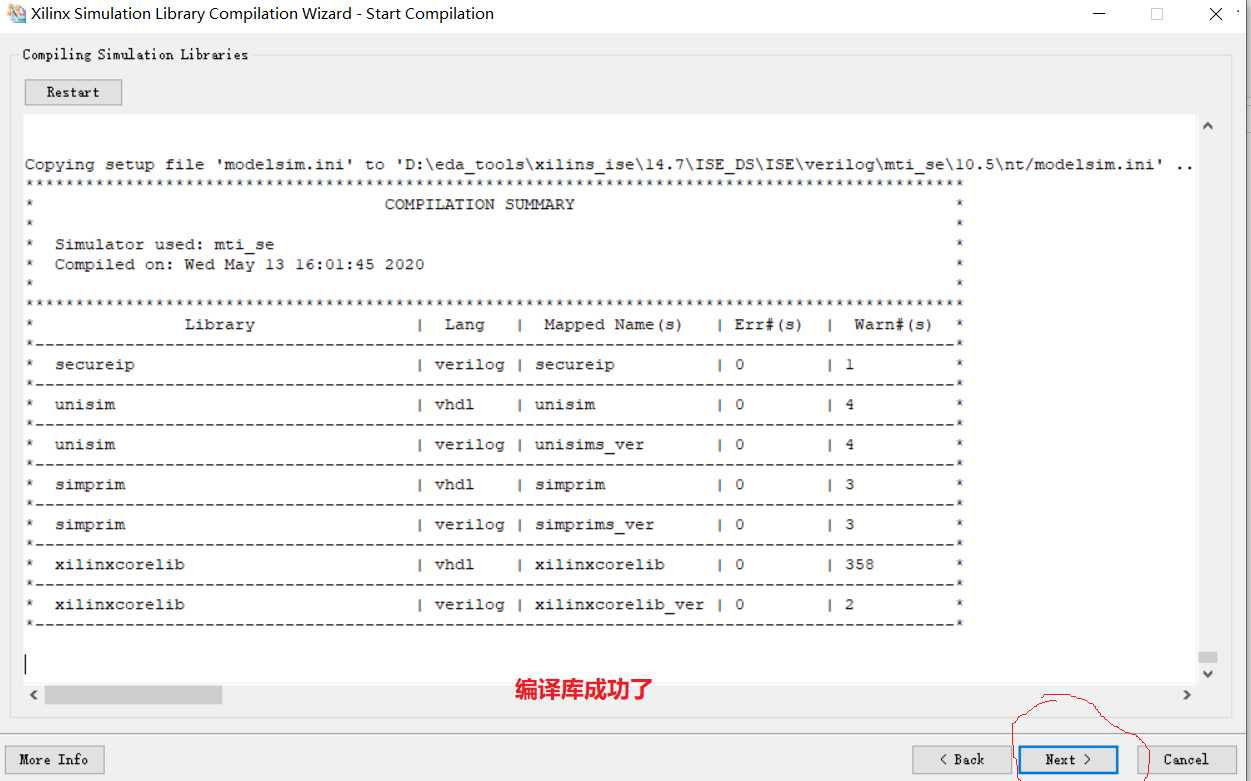

第七步:编译库后,没有错误,且出现了下面的几个库,说明编译库成功了哈

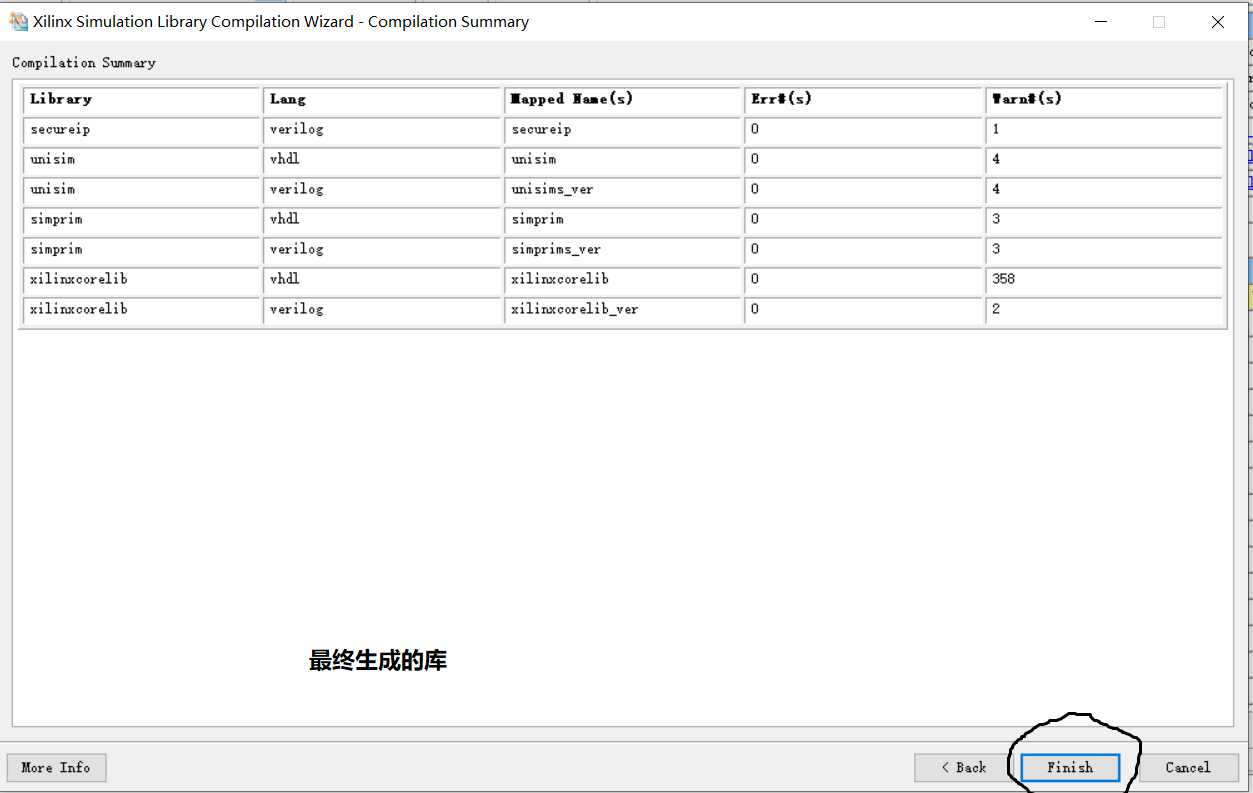

第八步:点击finish即可。

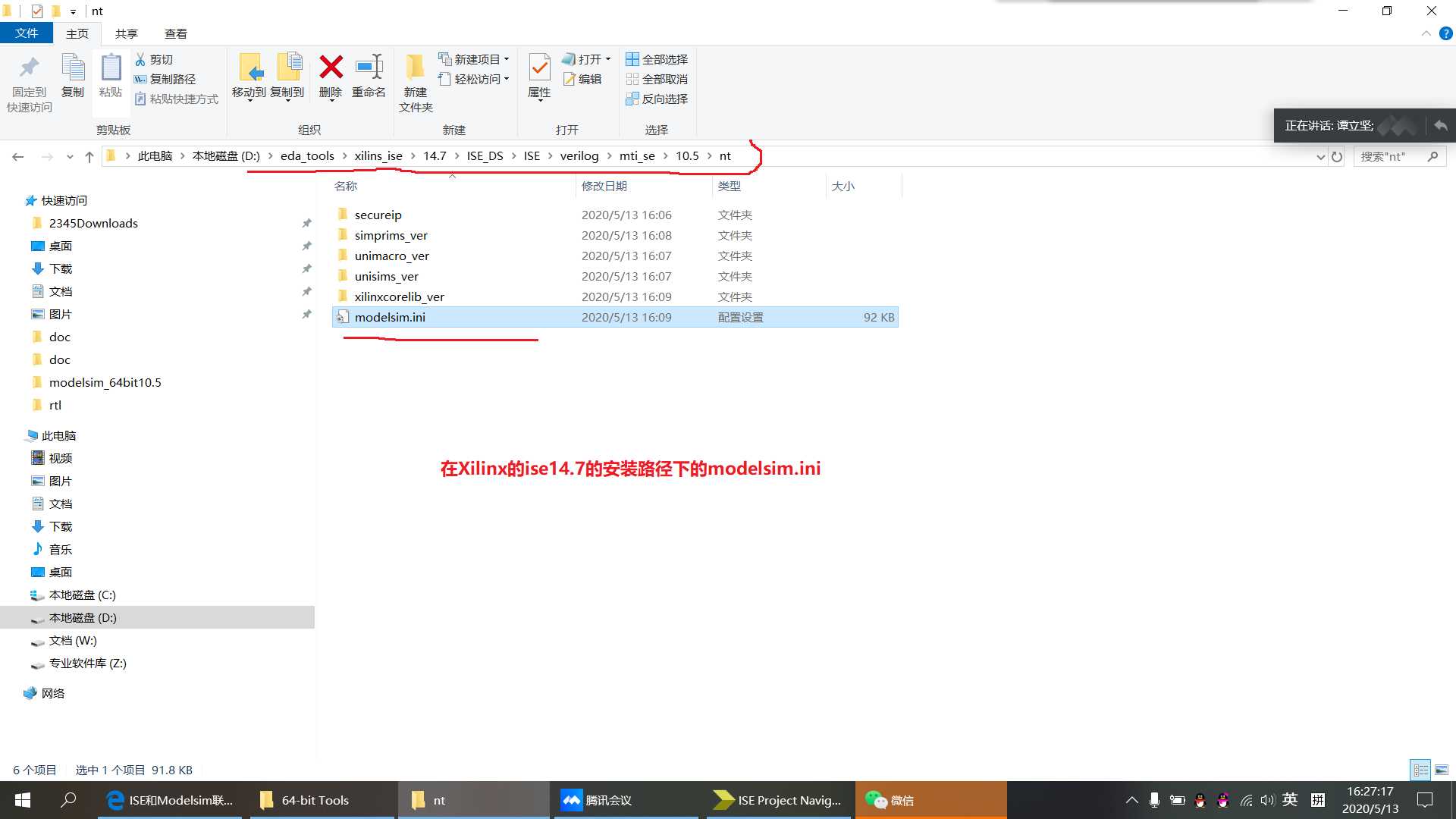

第九步:从上一步,我们编译库成功了,接着就是对ISE14.7和modelsim10.5的ini文件操作勒!先是ISE14.7如下图所示

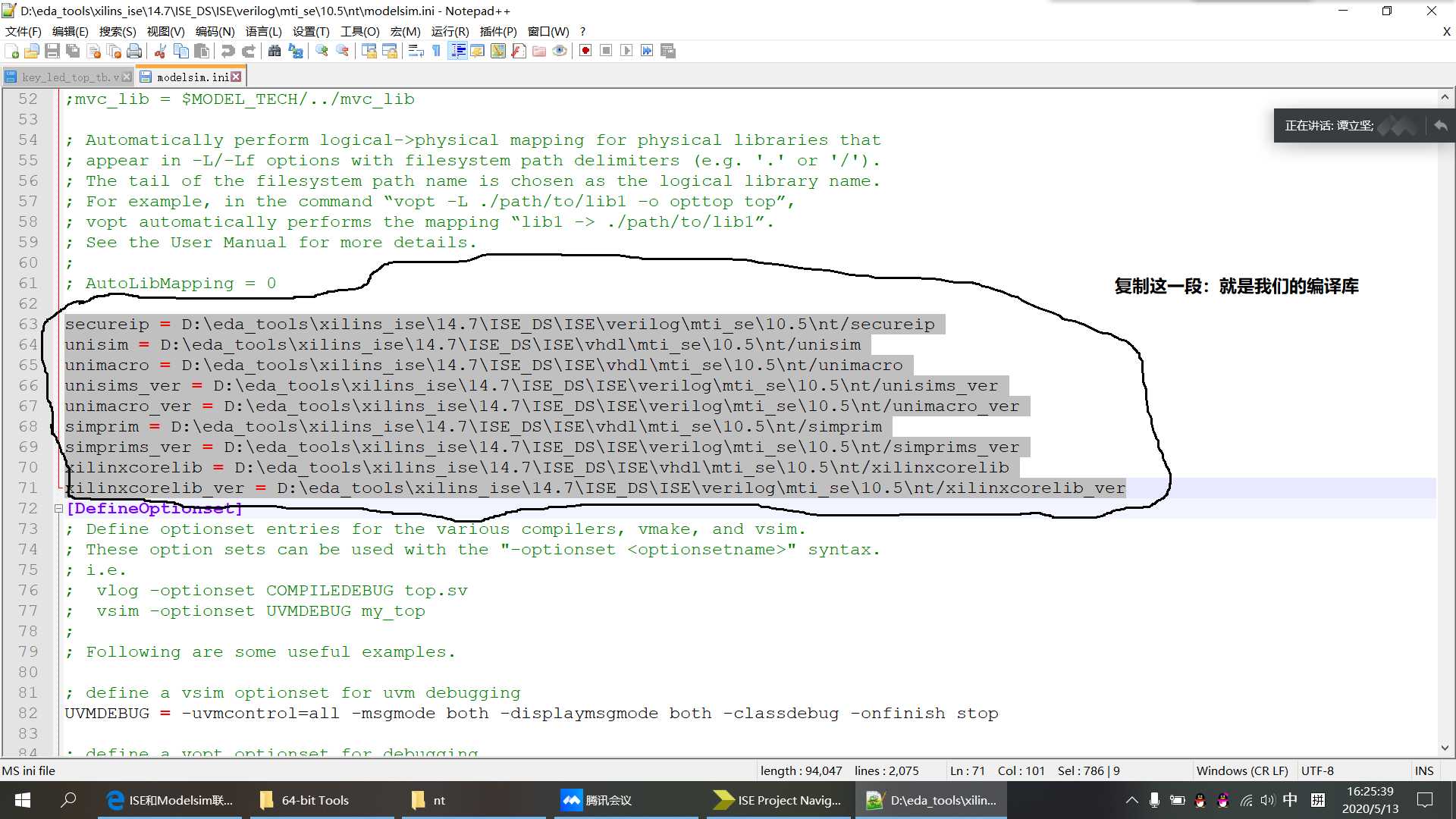

第十步:如下图,用notepad++打开上一步的ISE14.7的inti文件后,复制下面的部分

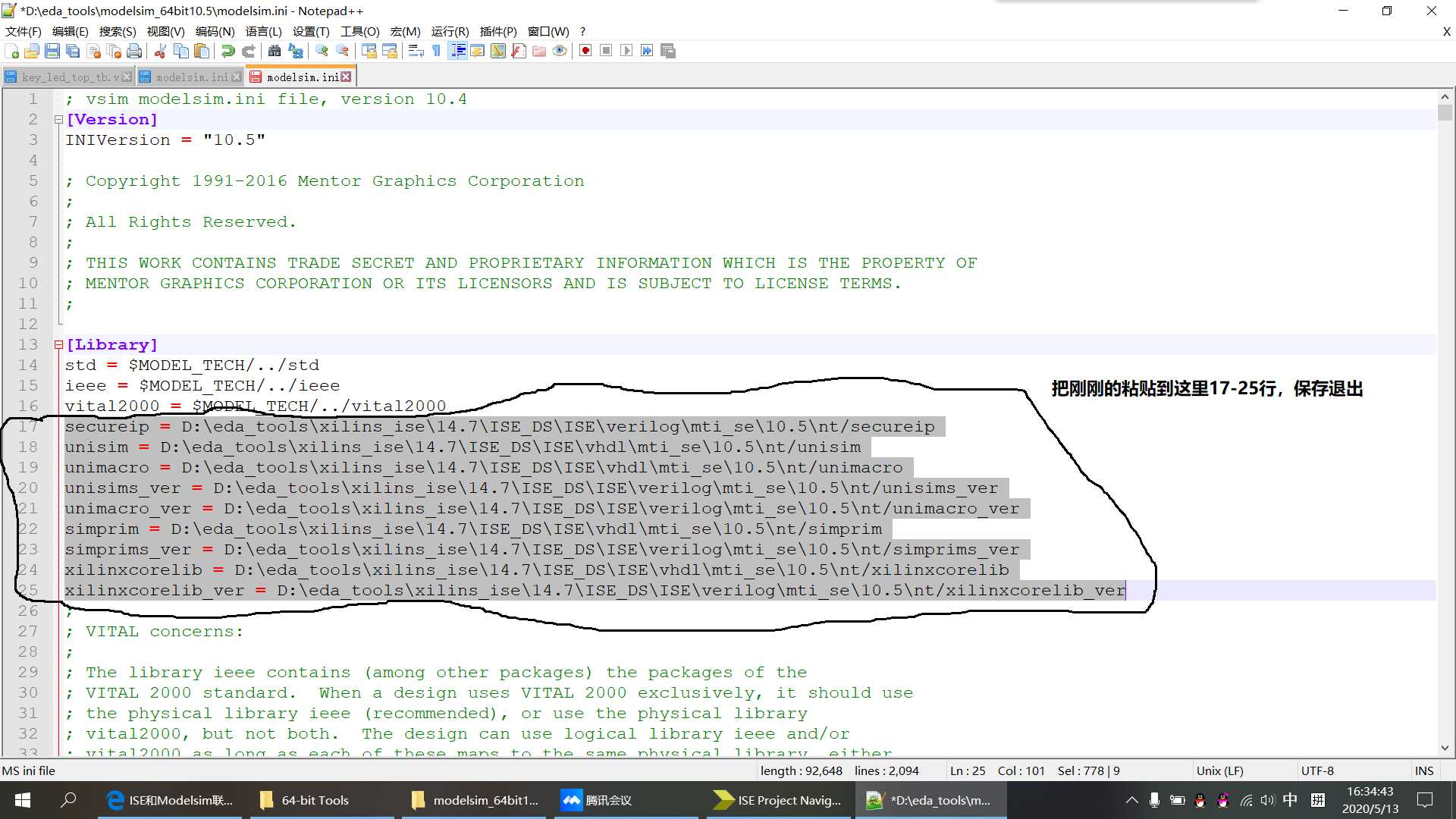

第十一步:直接把上一步ise14.7的复制的部分粘贴到下面位置,再保存退出就行

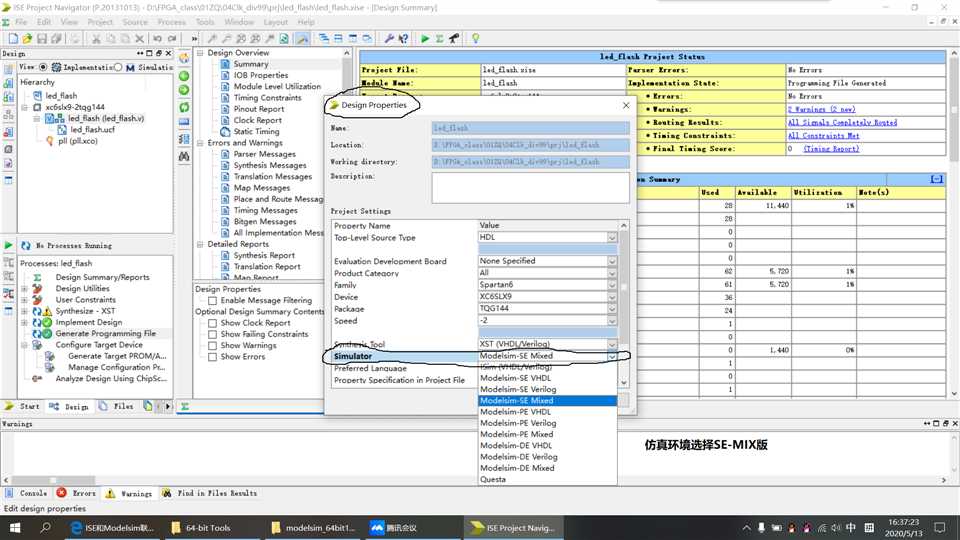

第十二步:设置仿真软件的版本,如下图所示

第十三步:按照下图的操作,在ISE14.7中调出来Modelsim10.5。走到这一步的我们就成功实现勒ISE和modelsim联合咯

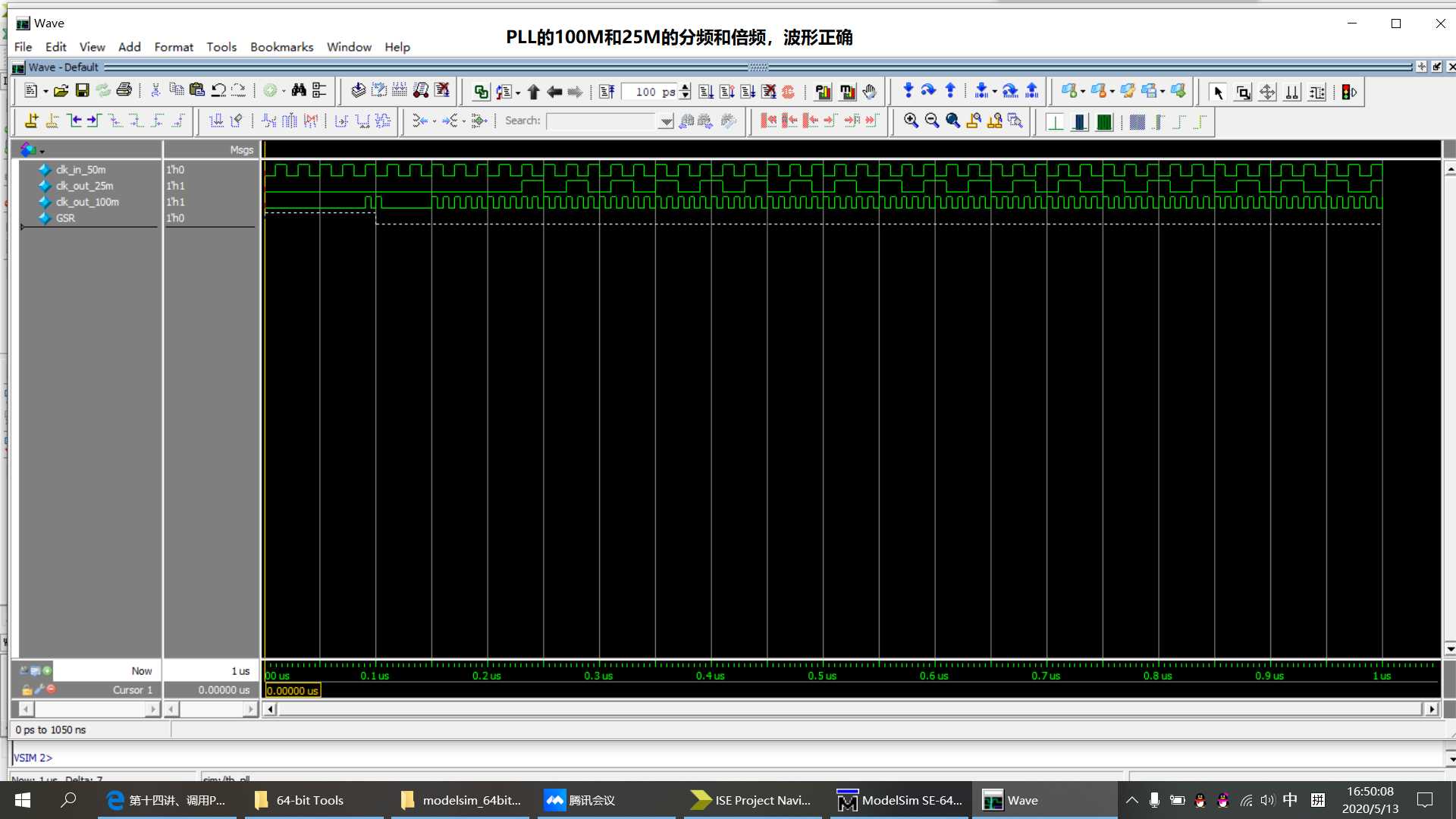

第四步:如下图,仿真波形成功显示

哈哈,整个ISE14.7 Modelsim10.5的关联和对仿真库的编译就欧克勒

不过在这个过程难免遇到一些问题,下面我来讲哈怎么解决这些问题

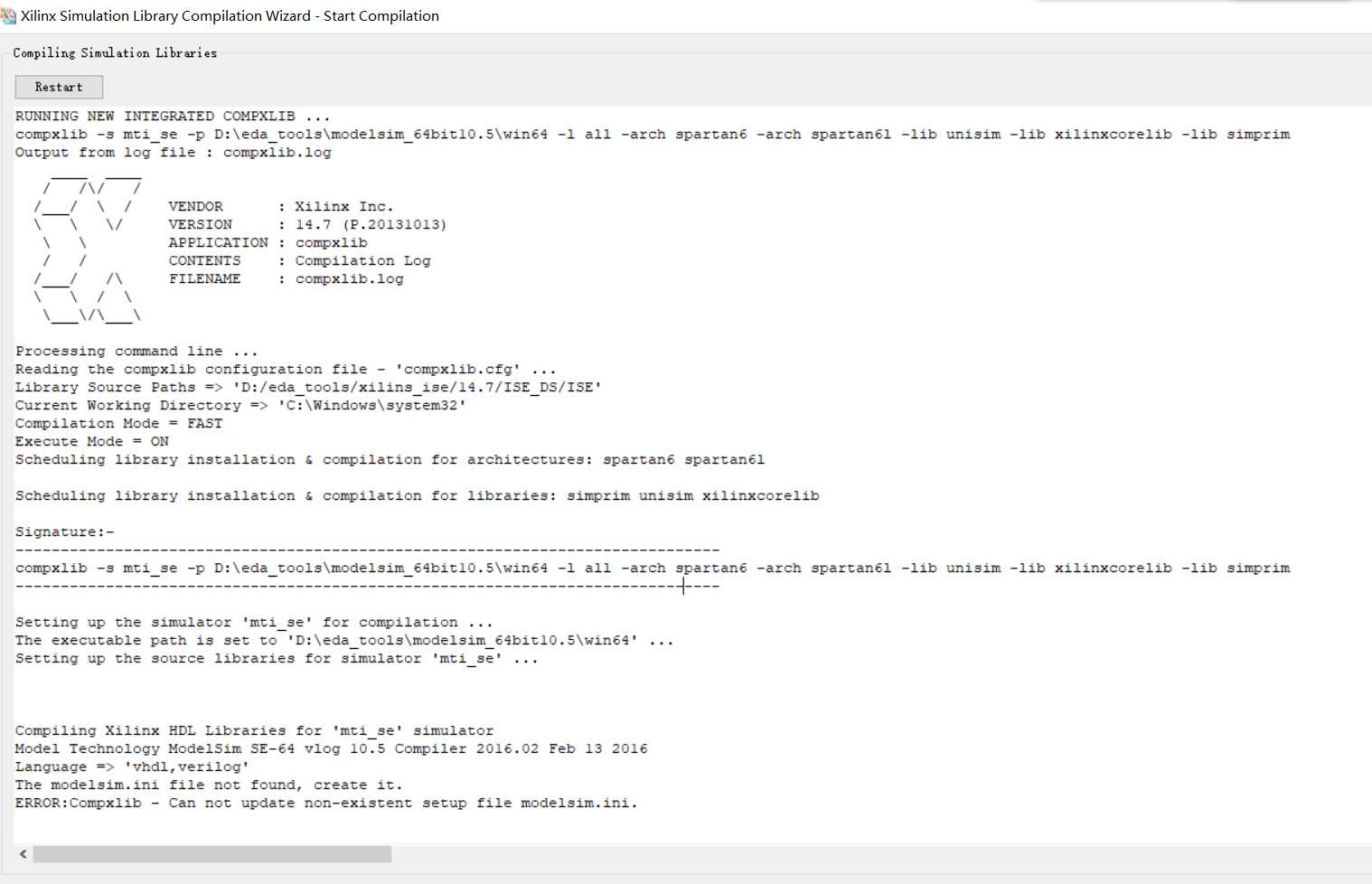

问题一;如下图

这个问题很麻烦,我上午搞了一个上午都没解决,一直显示这个,哈哈后面还是被我解决勒

我的解决办法很简单:在ise14.7的安装目录下,找到下面这个程序,点击后就回到上面教程的第一步开始就不会编译出错。

以上是关于关于ISE14.7 时钟IP核使用 输出时钟恒为0的主要内容,如果未能解决你的问题,请参考以下文章

(转)modelsim10.0C编译ISE14.7的xilinx库(xilinx ip核)