DSP_ePWM Module

Posted cian-h

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了DSP_ePWM Module相关的知识,希望对你有一定的参考价值。

Ref:TMS320x2833x, 2823x Enhanced Pulse Width Modulator (ePWM) Module

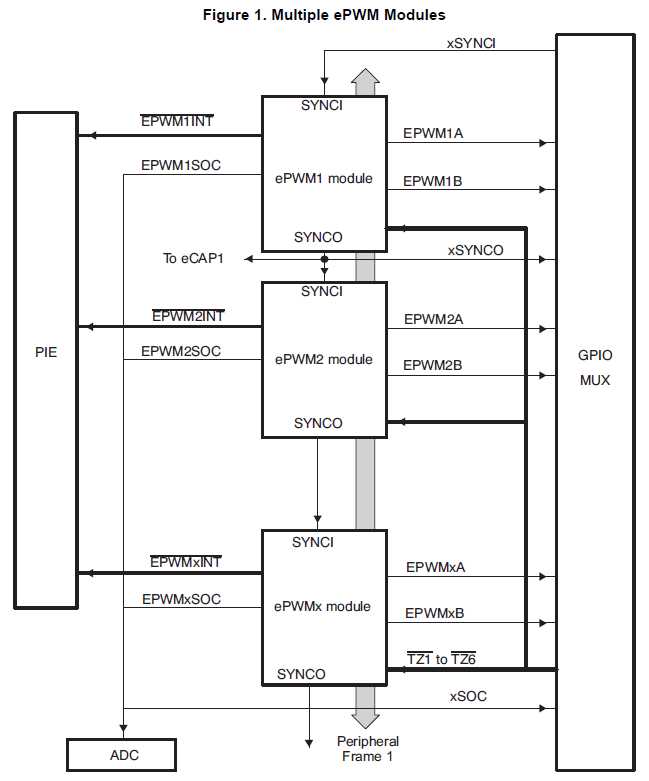

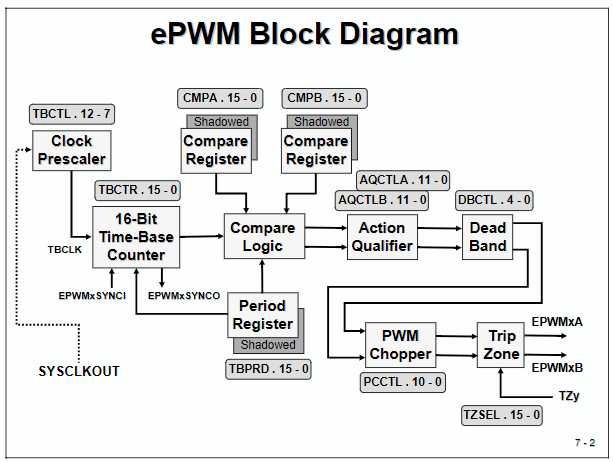

Multiple ePWM Modules

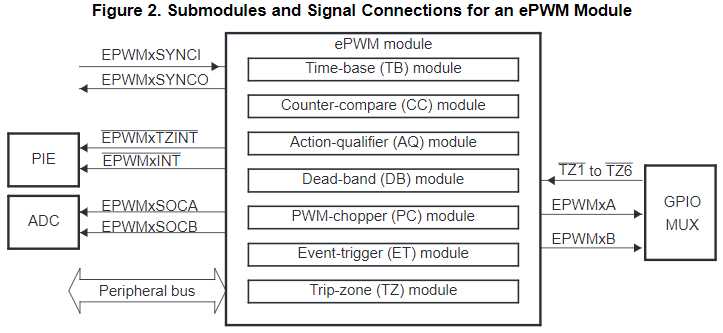

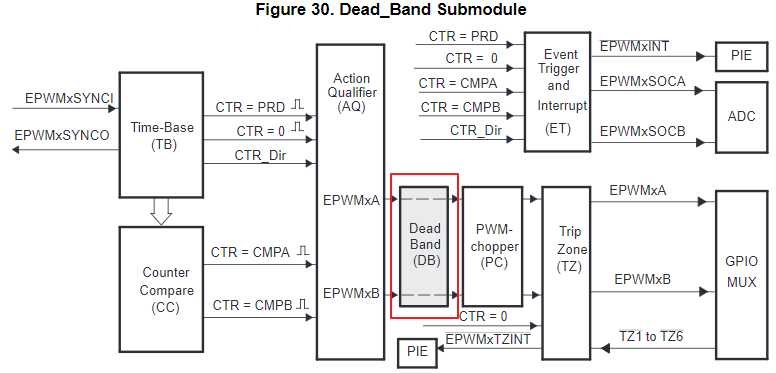

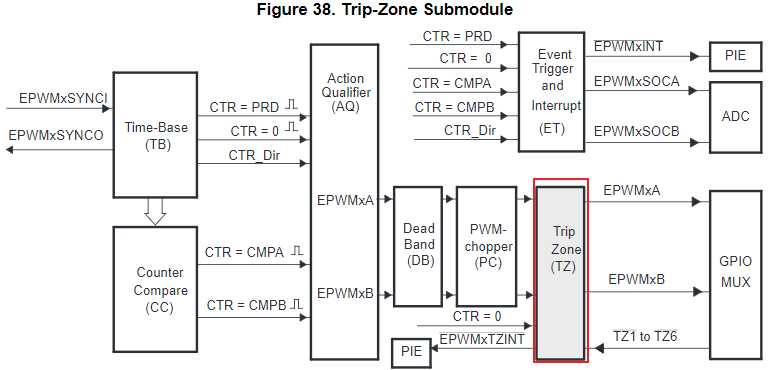

Submodules and Signal Connections for an ePWM Module(ePWM模塊的子模塊和信號連接)

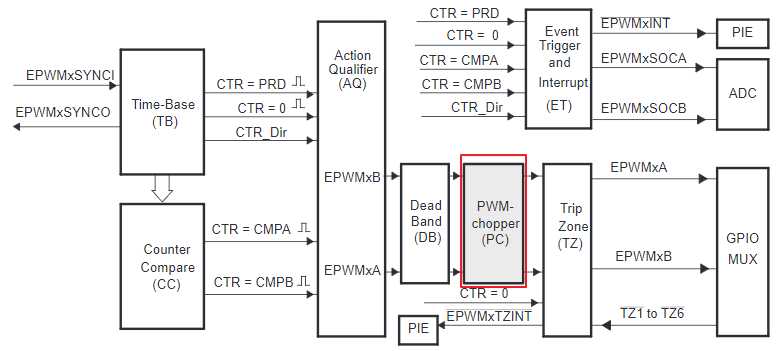

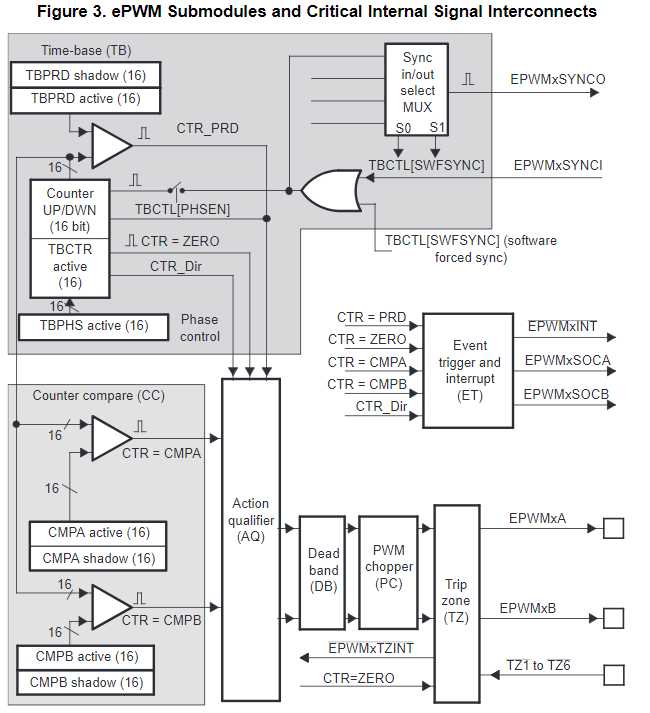

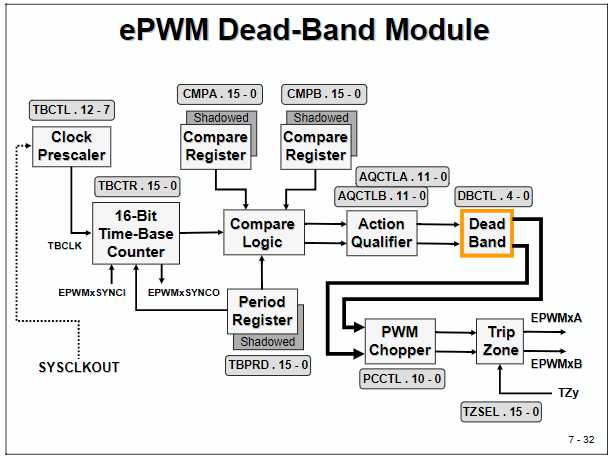

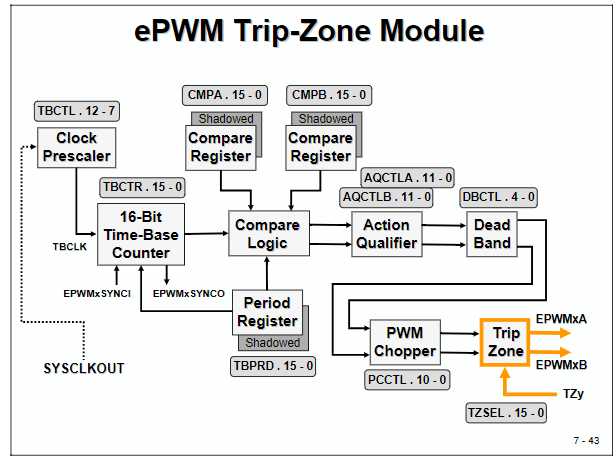

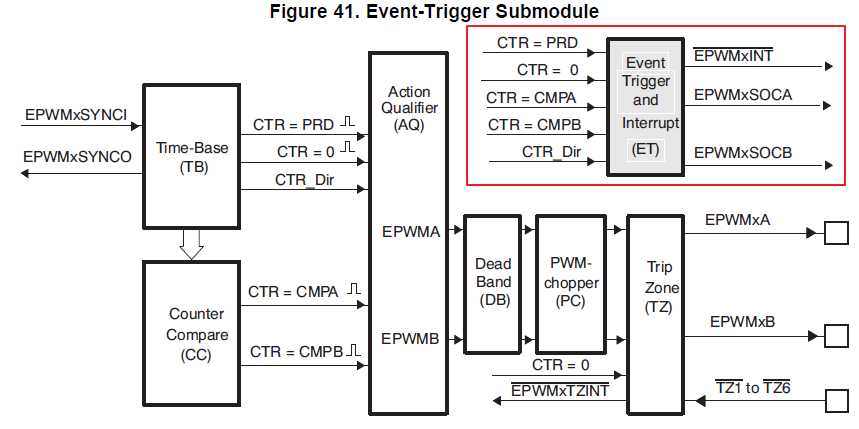

ePWM Submodules and Critical Internal Signal Interconnects(Epwm內部結構圖)

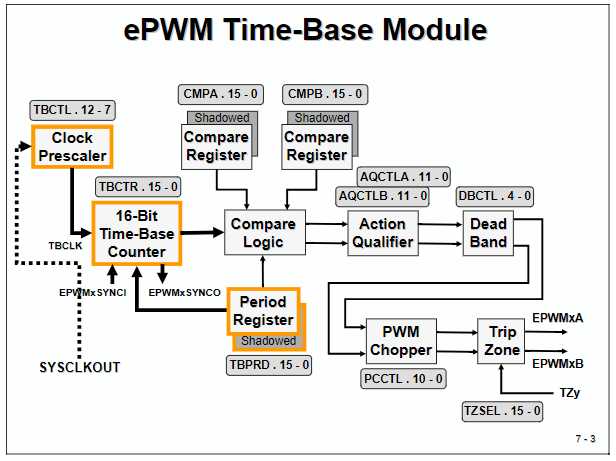

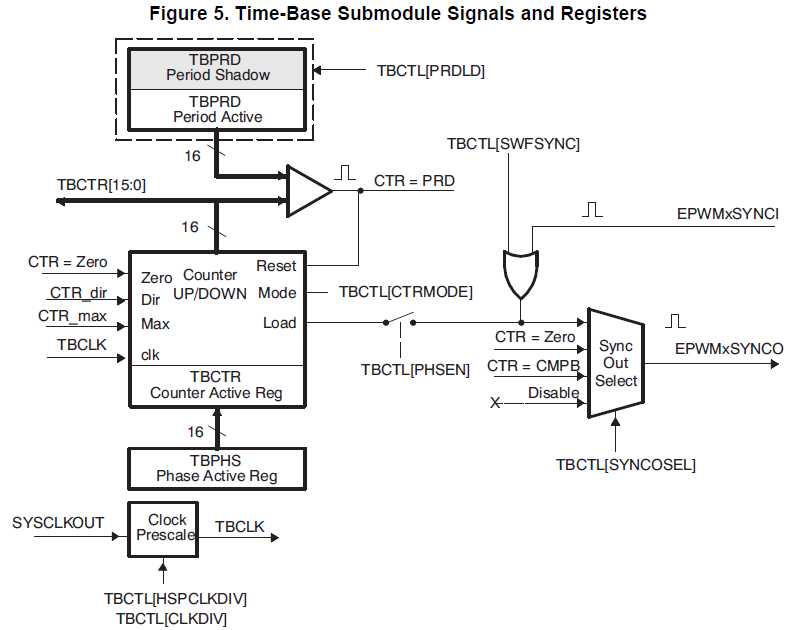

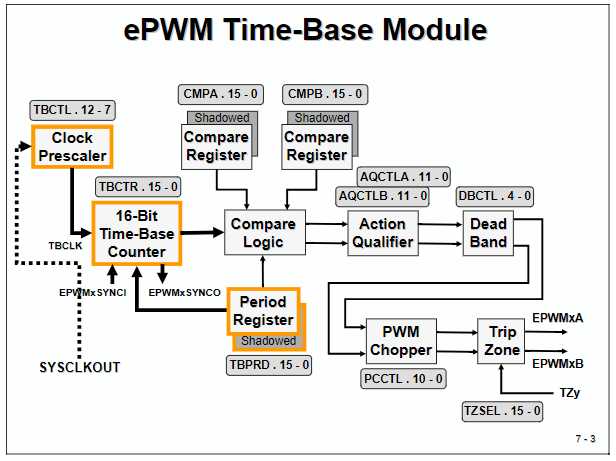

Time-Base (TB) Submodule(時間基準子模塊)

時鐘預分頻器(寄存器TBCTL,位12至7)可用於將輸入計數頻率減少1和1792之間的可選因數。

寄存器TBPRD定義了輸入信號周期的長度,以輸入信號的時間週期的倍數為單位。

F2833x的另一個獨特功能是其操作寄存器的“影子”功能,在ePWM單元可用於比較寄存器A,B和周期寄存器的情況下。對於某些應用程序,有必要在每個週期修改比較或週期寄存器內的值。後台寄存器的優點是我們可以為當前的下一個時段準備值。如果沒有後台功能,我們必須等待當前時段的結束,然後觸發高優先級的中斷。有時這種安排形式將錯過它的最後期限......

影子寄存器的內容被傳送到活動寄存器。這可以防止由於軟件異步修改寄存器而導致的損壞或虛假操作。

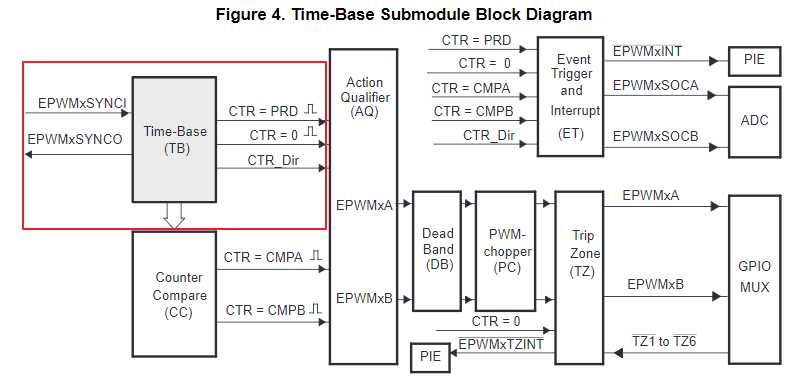

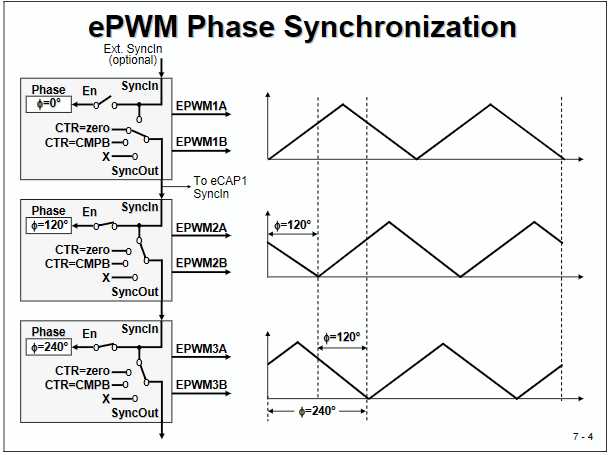

ePWM Phase Synchronisation

時基同步方案連接設備上的所有ePWM模塊。每個ePWM模塊都有一個同步輸入(EPWMxSYNCI)和一個同步輸出(EPWMxSYNCO)來使ePWM單元彼此同步。

例如,我們可以將一個ePWM單元定義為“主”,每次計數器等於週期時生成一個輸出信號“SYNCO”。

可以初始化兩個ePWM單元以將此信號識別為“SYNCI”,並在每次收到此信號時立即開始計數。

以這種方式,我們已經建立了3個ePWM信道的同步集合。但我們可以做得更好。

通過使用另一個名為“TBPHS”的寄存器,我們可以在主站,從站1和從站2之間引入相移,這是三相控制系統的絕對必要條件。

Example:

ePWM2和ePWM3的寄存器TBCNT分別預加載了一個對應於120°和240°的起始值。在這個例子中,每當計數器寄存器等於零時,ePWM1就被初始化為主器件來產生SYNCO。

通過使能ePWM2和ePWM3的相位輸入功能,兩個通道將作為從器件1和從器件2運行,並將其計數器寄存器TBCNT加載到存儲在相應相位寄存器TBPHS中的數字中。

- ePWM1 counts from 0 to 6000. TBPRD = 6000

- ePWM2 register TBPHS = 2000

- ePWM3 register TBPHS = 4000

Time-Base ClockSynchronization(時基時鐘同步)

置位時,所有啟用的ePWM模塊時鐘都將在TBCLK的第一個上升沿對齊的情況下啟動。對於完美同步的TBCLK,每個ePWM模塊的預分頻器必須設置相同。

啟用ePWM時鐘的正確過程如下所示:

- 在PCLKCRx寄存器中啟用ePWM模塊時鐘

- Set TBCLKSYNC= 0

- Configure ePWM modules

- Set TBCLKSYNC=1

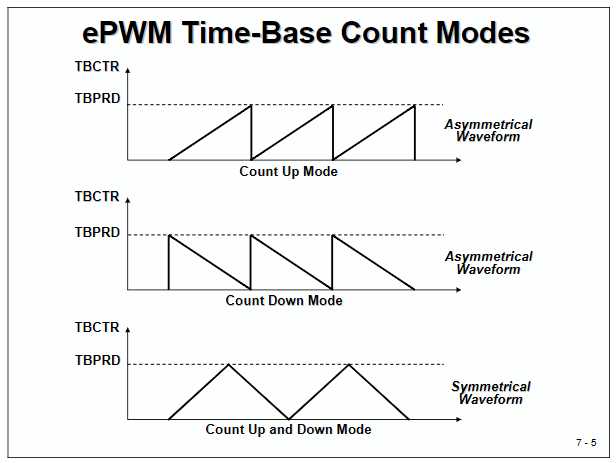

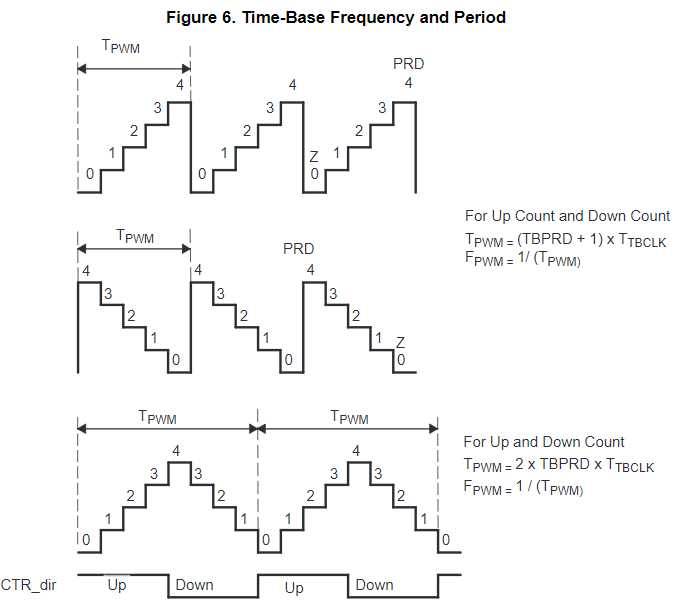

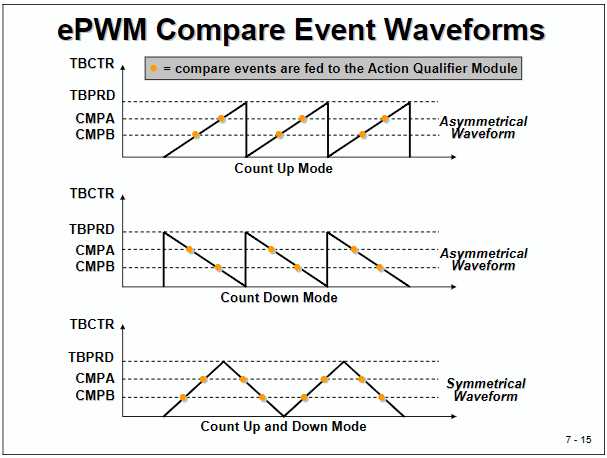

Timer Operating Modes

每個ePWM模塊都能夠以3種不同的計數模式中的一種進行操作,由寄存器TBCTL的位1和位0選擇:

- count up mode

- count down mode

- count up and down mode

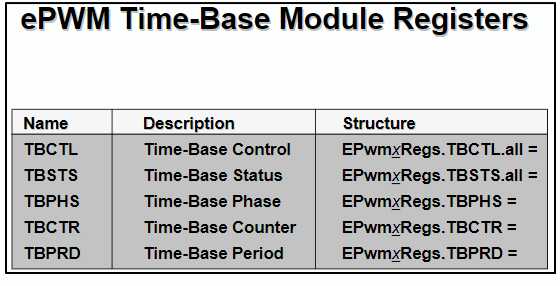

Time Base Registers

要使用C編程語言訪問這些寄存器,我們可以利用源代碼文件“DSP2833x_GlobalVariableDefs.c”,該文件將所有內存映射的硬件寄存器定義為全局變量。

有變量均基於結構和聯合數據類型,也已由德州儀器定義,並包含在主頭文件“DSP2833x_headers.h”中。

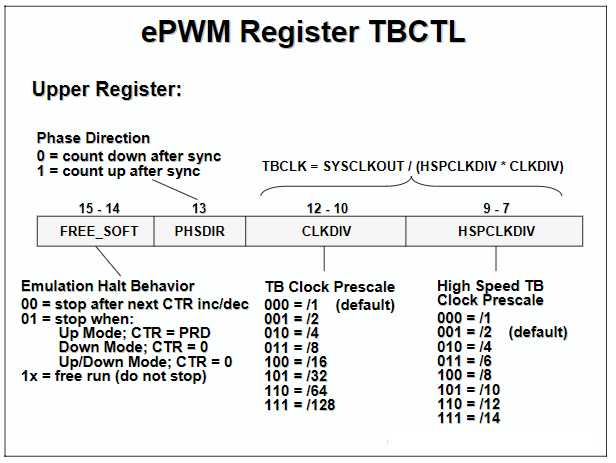

Time Base Control Register TBCTL

FREE_SOFT:

- 控制DSC和JTAG仿真器之間的交互。

- 如果代碼的執行順序碰到斷點,我們可以指定該ePWM單元應該發生什麼。

PHSDIR:

- 指定在看到SYNCIN脈沖之後,此ePWM單元是開始向上還是向下計數。

- 如果單個ePWM設置中禁用了同步功能,則該位為“不關心”

CLKDIV and HSPCLKDIV:

- 可降低輸入頻率“SYSCLKOUT”

- 對於100MHz系統,每個脈沖轉換成10ns,對於150MHz-系統轉換成6.667ns。

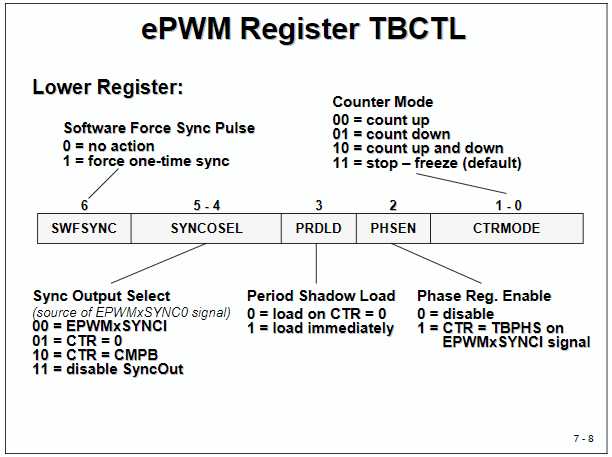

SWFSYNC:

- 設置該位的指令將立即從該ePWM單元產生一個“SYNCO”脈衝

SYNCOSEL:

- 選擇SYNCO信號的來源。

- 如果未使用通道同步,請關閉此功能。

PRDLD:

- 啟用(0)或禁用(1)TBPRD的影子寄存器功能。如果禁用,所有寫入TBPRD的指令將直接改變週期寄存器。 如果啟用,寫入指令將在陰影中存儲新值。在下一個事件CTR = 0時,陰影值將自動加載到TBPRD中。

PHSEN:

- 通過“SYNCIN”觸發器啟用(1)從TBPHS預加載寄存器TBCTR

CTRMODE:

- 定義此ePWM單元的操作模式

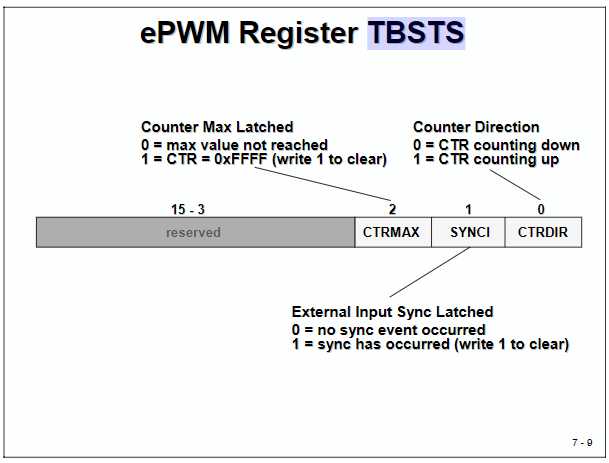

Time Base Status Register TBSTS

該寄存器標記了ePWM單元的當前狀態

CTRDIR

- 如果ePWM向上計數(1)或向下計數(0)

SYNCI:

- 如果此ePWM單元已經看到SYNCI事件,則該位為1,否則為0.

- 注意:要清除此位,必須向其中寫入1!

CTRMAX:

- 如果由於某種原因16位計數器寄存器TBCTR溢出,位“CTRMAX”將被設置為1.在正常情況下,這不應該發生,所以我們可以將此位作為安全警報信號。

- 注意:要清除這一點,必須寫入1!

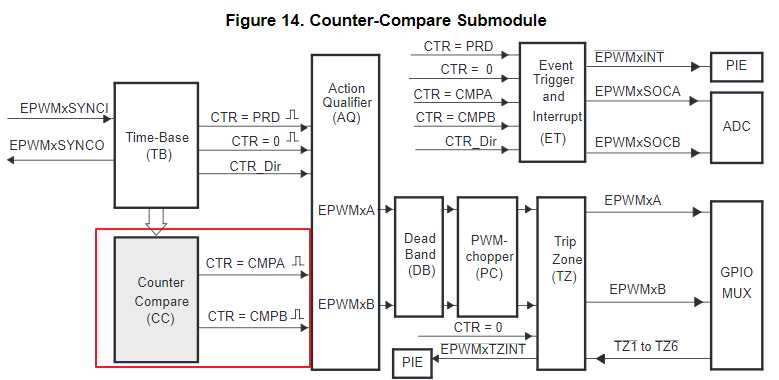

Counter-Compare (CC) Submodule

除了0或TBPRD觸發以外又多了CMPA與CMPB,每個週期最多使用4個點來觸發一個動作。

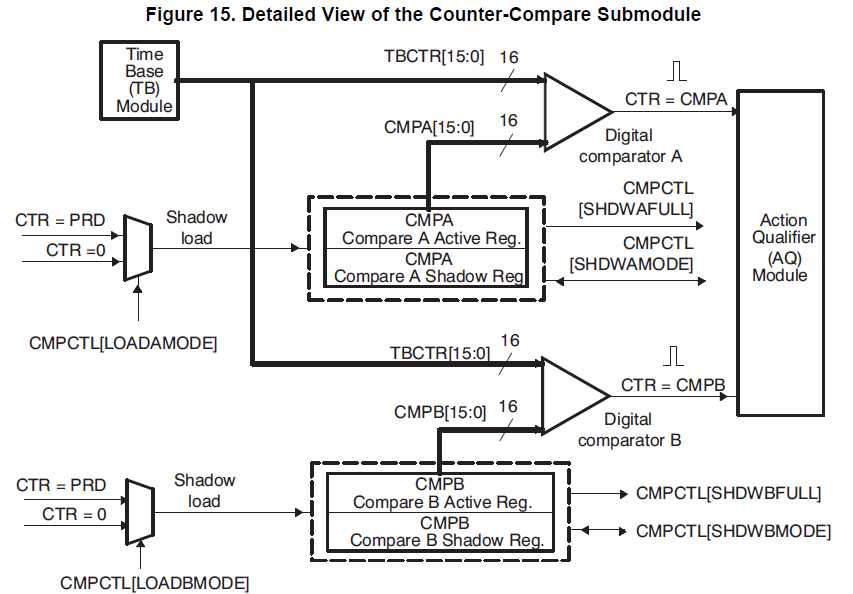

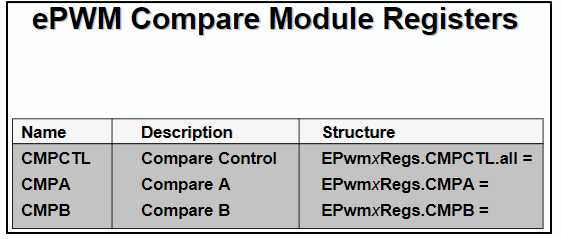

ePWM Compare Module Registers

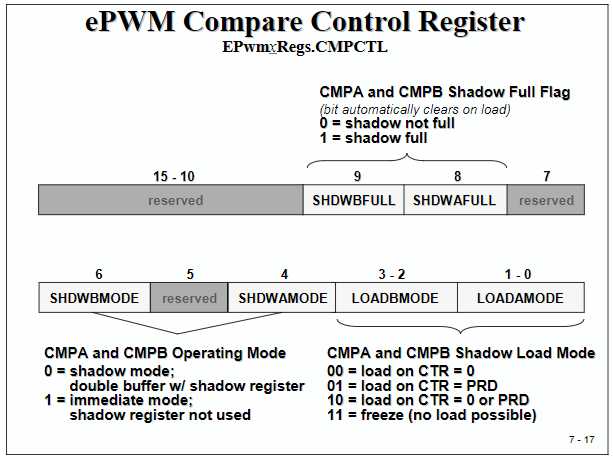

ePWM Compare Control Register

LOADxMODE:

- 定義硬件事件,它將從後台複製一個值到活動的前台寄存器中

SHDWxMODE:

- 啟用(0)或禁用(1)後台更新模式。如果禁用,所有寫入指令將立即更改寄存器CMPA或CMPB中的值

SHDWxFULL:

- 只讀狀態字段。如果陰影已滿(1)並且硬件將該值複製到前景中,則該位將自動清除

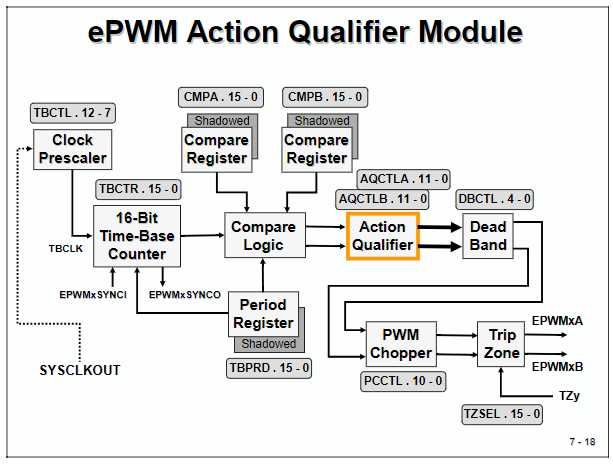

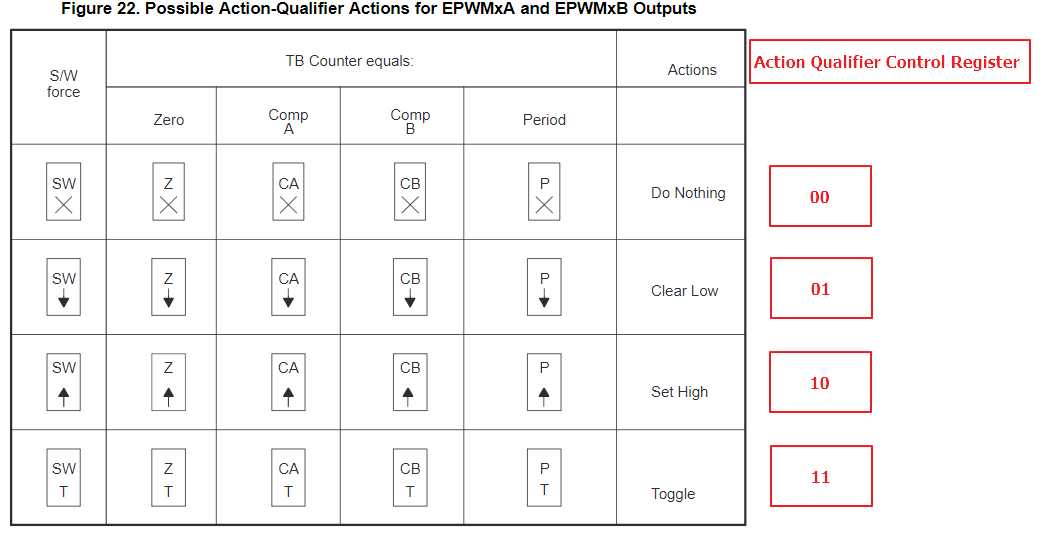

Action-Qualifier (AQ) Submodule

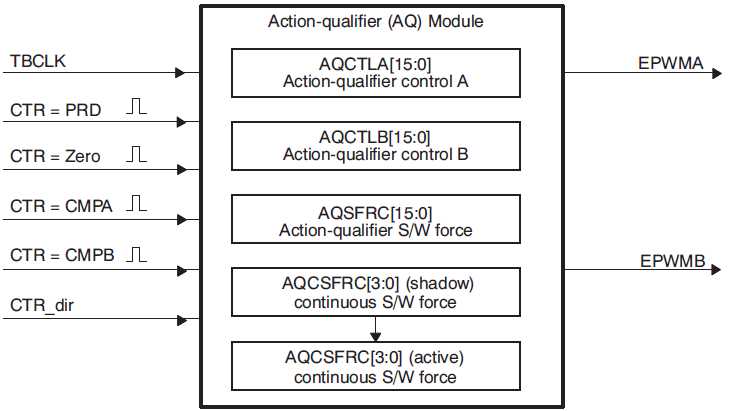

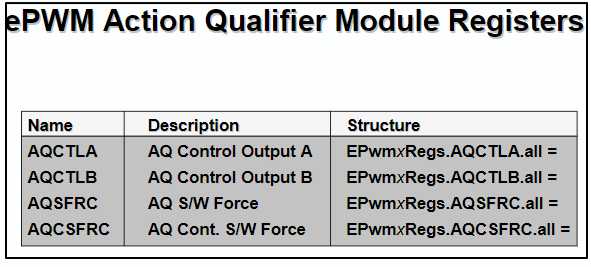

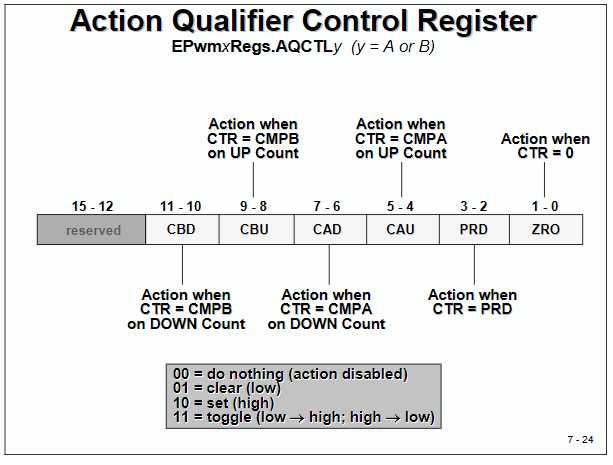

Action Qualifier Registers

Action Control Register A and B

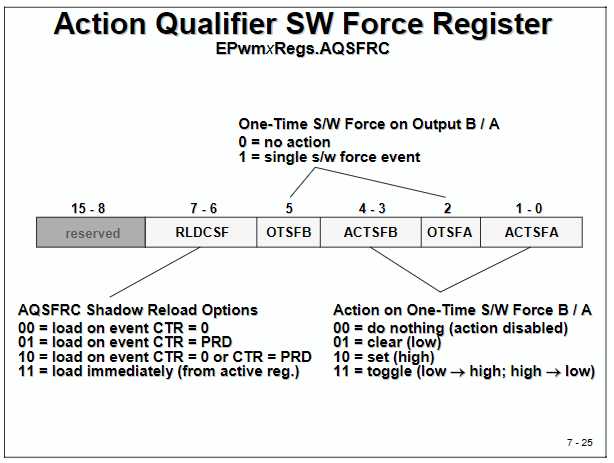

Software Forcing Registers

該寄存器允許強制輸出線進入定義狀態。“一次”代表當前PWM頻率週期的持續時間。

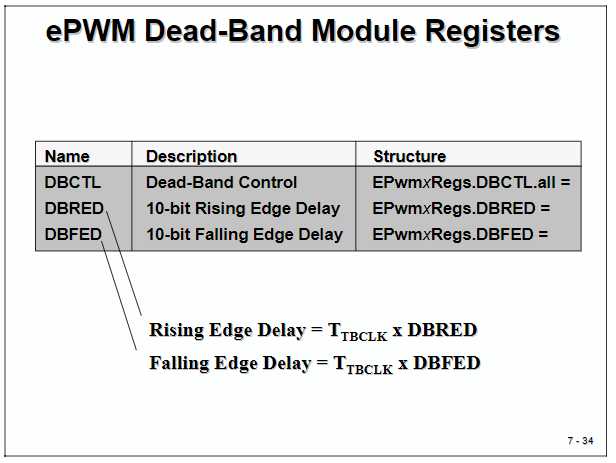

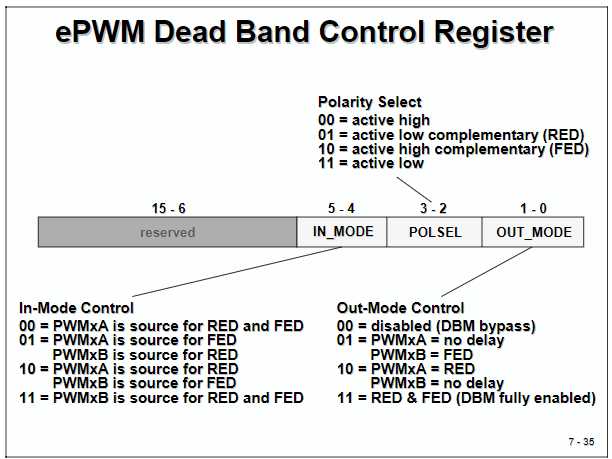

Dead-Band Generator (DB) Submodule

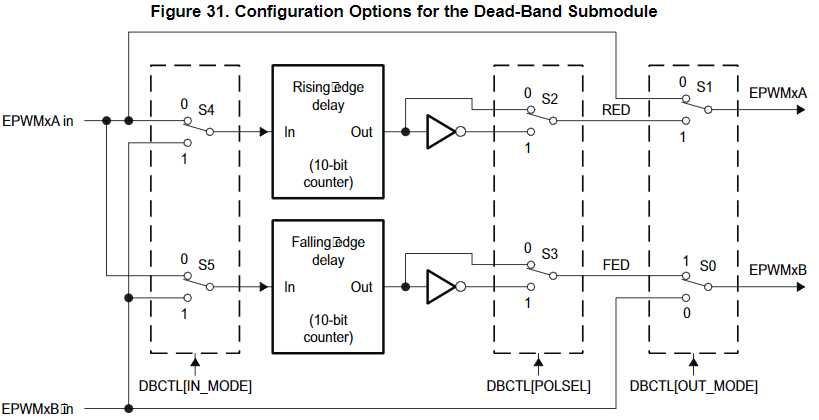

死區單元的設置基於六個開關S0至S5。

更經典的模式假定S4 = 0且S5 = 0 [IN_MODE]被配置為使得“EPWMxA-IN”此訊號是下降沿延遲或是上升沿延遲。

Dead Band Unit Registers

死區控制寄存器結合了開關S0到S5的位域:

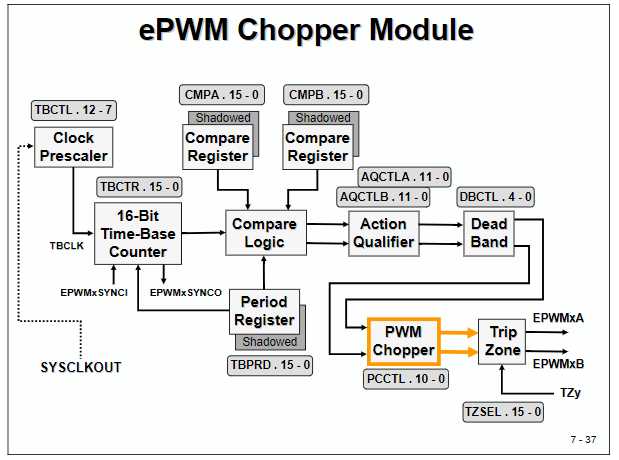

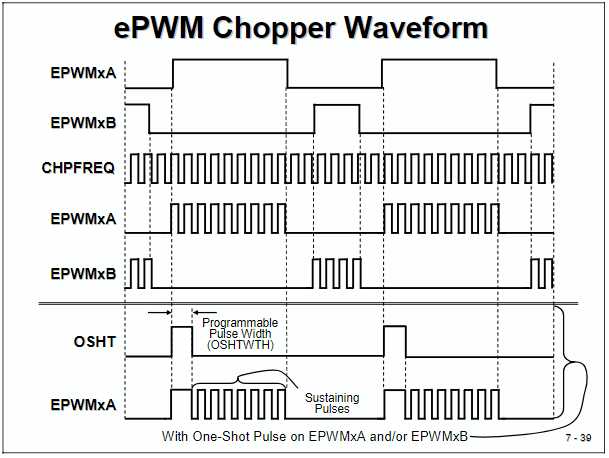

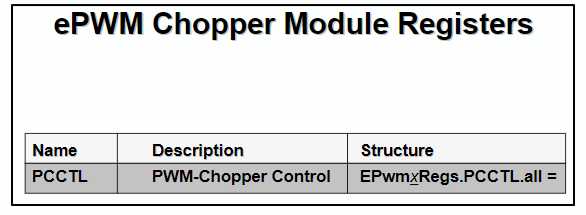

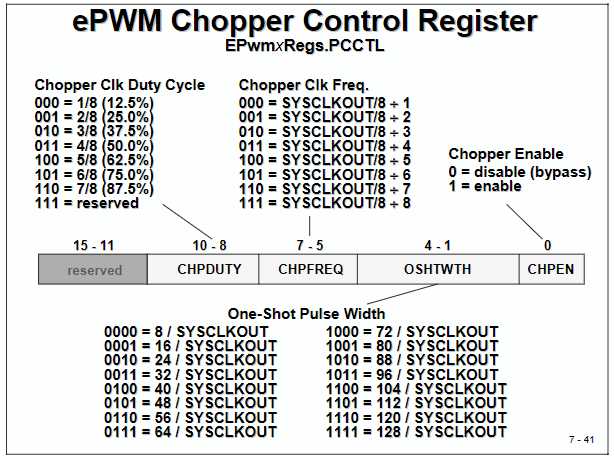

ePWM Chopper Module

暫不討論

Chopper Mode Control Registers

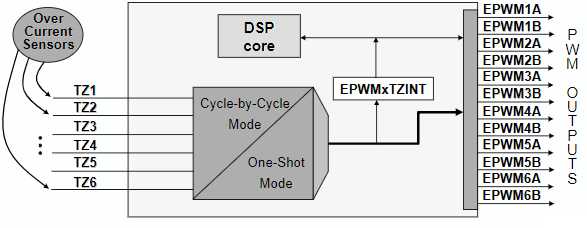

Trip-Zone (TZ) Submodule

Trip Trip--Zone Module Features

- Trip Trip - Zone具有快速,獨立於時鐘的高邏輯邏輯路徑,具有與EPWMxA EPWMxA / B輸出引腳/ B輸出引腳高阻抗阻抗快速,時鐘獨立的邏輯路徑

- 中斷延遲可能無法在響應ov時保護硬件當通過ISR軟件響應超過當前條件或短路條件或通過ISR軟件電路短路時,中斷延遲可能無法保護硬件

- Supports:

- 對於主要短路或過電流條件下的主要短路或過電壓跳閘 = 一次性跳閘(one shot trip)

- 通過循環跳閘來限制電流循環 (cycle byby cycle)

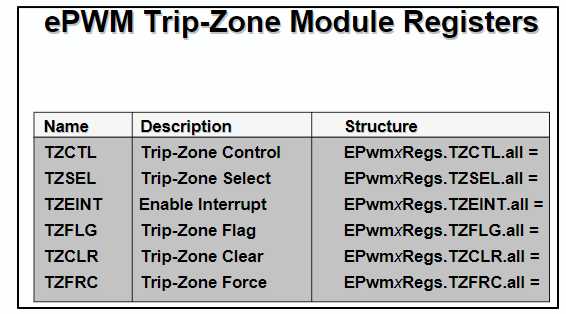

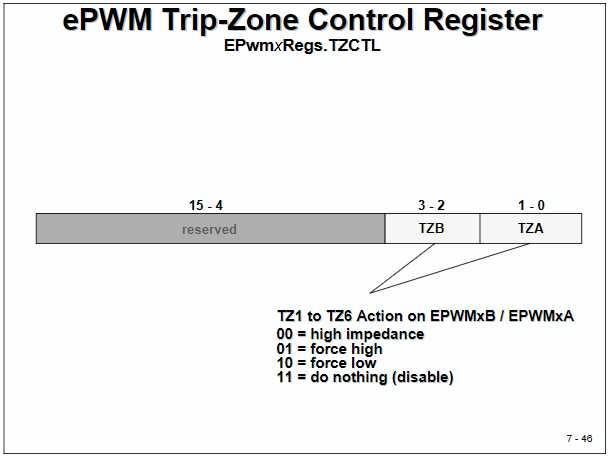

ePWM Trip - Zone Registers

寄存器TZCTL用於定義在過電流信號情況下線路ePWMxA和ePWMxB的狀態。

寄存器TZCTL用於定義在過電流信號情況下線路ePWMxA和ePWMxB的狀態。

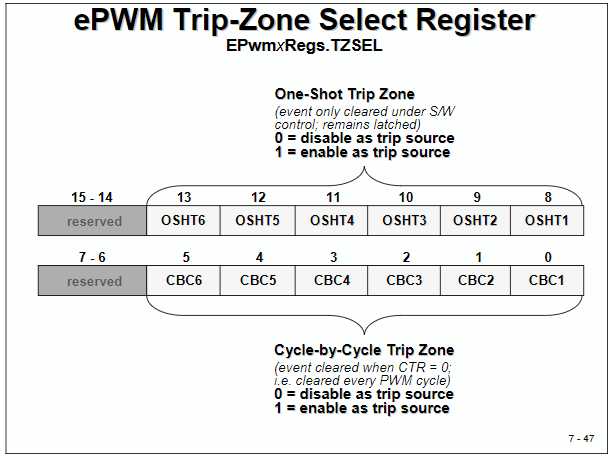

使用寄存器TZSEL,我們可以指定應該將哪個輸入信號TZx用作逐週期或作為永久(單次)關閉信號。

使用寄存器TZSEL,我們可以指定應該將哪個輸入信號TZx用作逐週期或作為永久(單次)關閉信號。

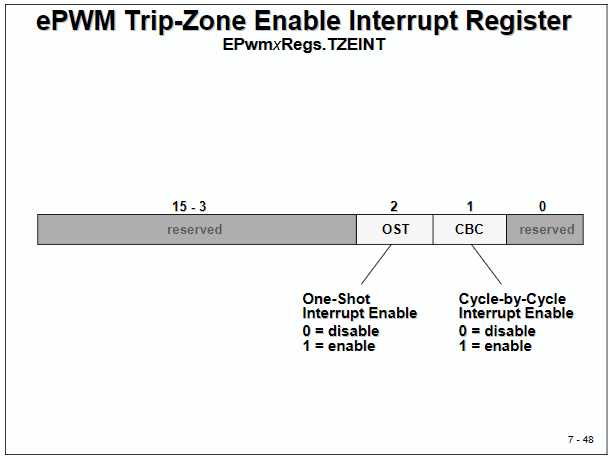

TZEINT可用於在閉環控制系統中出現過電流情況下請求中斷服務請求。

們可以使用逐週期或單次過電流中斷請求,具體取決於寄存器TZSEL中的選擇。

樣的中斷事件中應該做什麼?那麼這取決於應用和故障的嚴重性。

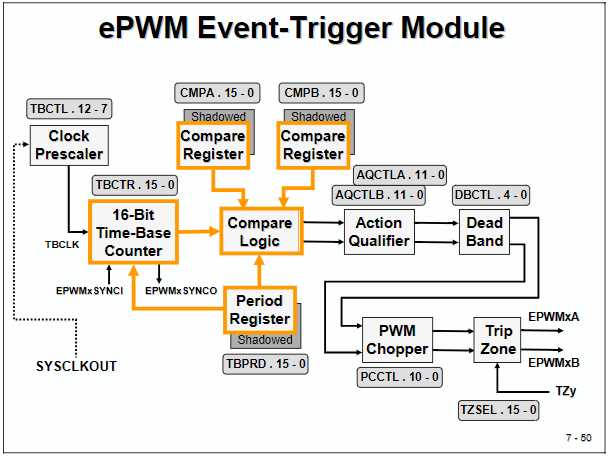

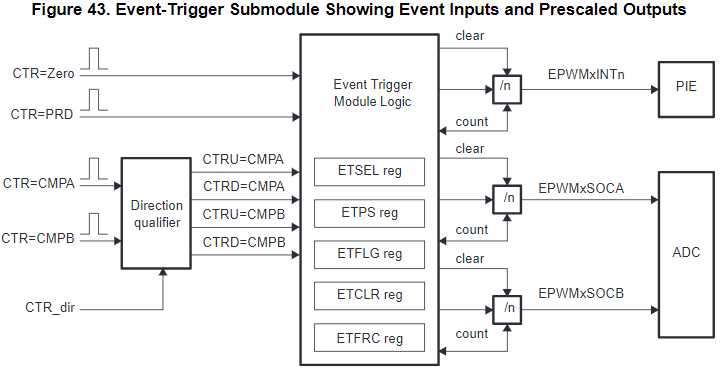

Event-Trigger (ET) Submodule

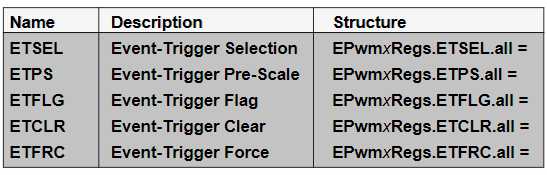

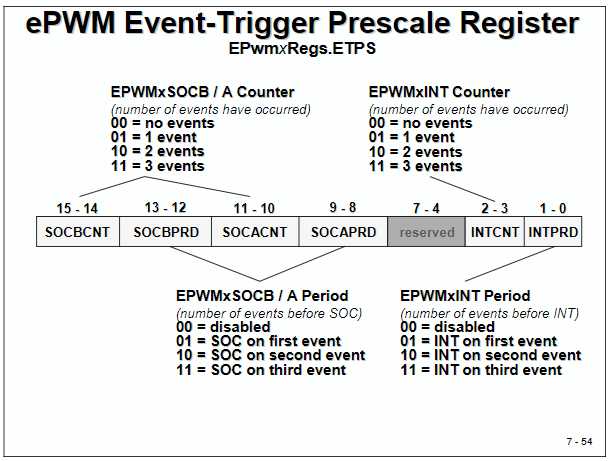

Event-Trigger-Sub模塊由一組寄存器初始化:

- ETSEL - 該暫存器選擇哪些可能的事件觸發中斷或開始ADC轉換。

- ETPS - 該暫存器程序用於對上述事件預處理??選項進行編程。

- ETFLG - 用標誌位註冊以指示所选和預分頻事件的狀態。

- ETCLR - 這些位允許您通過軟件清除ETFLG寄存器中的標誌位。

- ETFRC - 這些位允許軟件強制執行事件。用於調試或s / w干預。

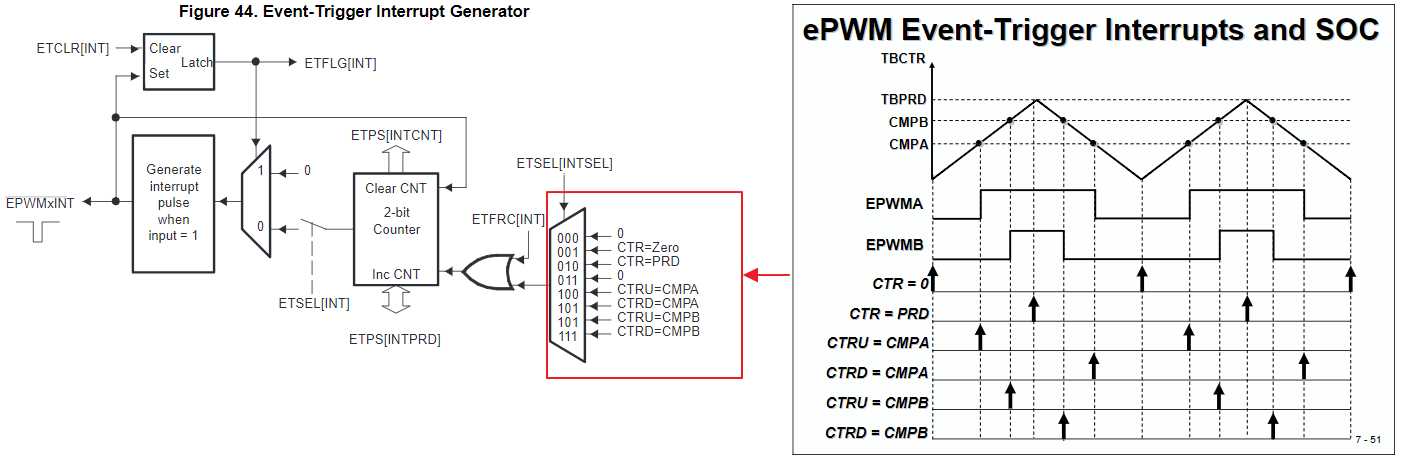

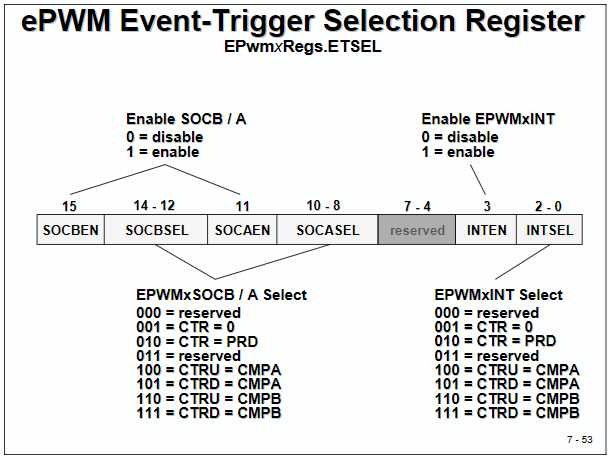

下圖顯示了事件觸發器的中斷生成邏輯。中斷週期(ETPS [INTPRD])位指定了引起中斷脈衝產生所需的事件數量。可用的選擇是:

- 不要產生中斷。

- 在每個事件上產生一次中斷

- 每兩個事件產生一次中斷

- 每三個事件產生一次中斷

也解釋哪個事件可以引起中斷由中斷選擇,由(ETSEL [INTSEL])位配置。

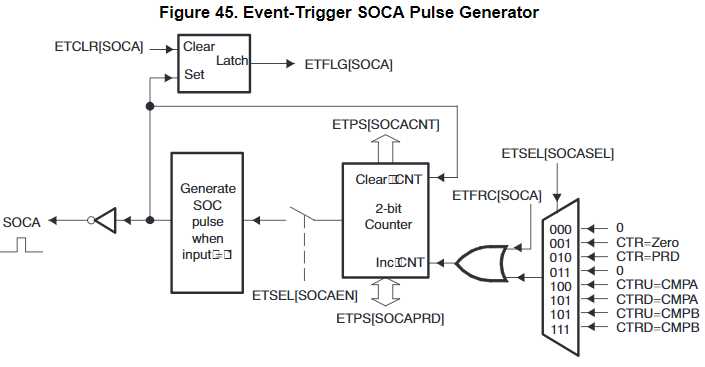

Event-Trigger SOCA Pulse Generator (用SOCA的脈衝觸發事件)

ePWM Event Trigger Module Registers

以上是关于DSP_ePWM Module的主要内容,如果未能解决你的问题,请参考以下文章